# A PREDICTIVE ANALOG DEAD-TIME CONTROL CIRCUIT FOR A HIGH EFFICIENCY SYNCHRONOUS BUCK CONVERTER

by

Luyan Mei

# A THESIS SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF

## MASTER OF APPLIED SCIENCE

in

The College of Graduate Studies

(Electrical Engineering)

## THE UNIVERSITY OF BRITISH COLUMBIA

(Okanagan)

May 2012

© Luyan Mei, 2012

## Abstract

The synchronous buck DC-DC power converter is the most common switching converter circuit used to step down a DC input voltage to a low logic level DC output voltage in computer applications. The synchronous buck converter has two power MOSFET switches that turn on in a complementary fashion. However, to avoid high input current spikes, a short duration of dead-time (i.e. a time interval when neither switch is on) is required. During dead-time intervals, the buck converter synchronous MOSFET internal body diode conducts the high inductor current, leading to high losses. To minimize this loss, a dead-time controller circuit is required to minimize the dead-time.

The majority of existing predictive dead-time controllers are digital. These dead-time controllers have problems caused by their discrete output including dithering in steady state and reduced accuracy. Furthermore, existing dead-time controllers are limited to buck converter switching frequencies of 300kHz. Therefore, for operation at switching frequencies above 300kHz, dead-time controllers need to be faster and should operate without dithering.

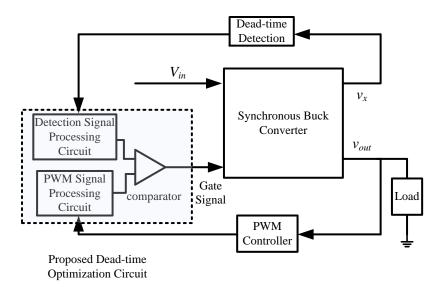

A one-step predictive dead-time control circuit for the synchronous buck converter is proposed in this thesis. It consists of a novel dead-time detection circuit and an analog optimization circuit. The detection circuit utilizes an integrated dead-time detection diode, which can be manufactured on the same die as the synchronous MOSFET in the buck converter. This results in an accurate detection signal indicating body diode conduction of the synchronous MOSFET. The dead-time optimization circuit is an analog circuit, which eliminates the shortcomings of digital control.

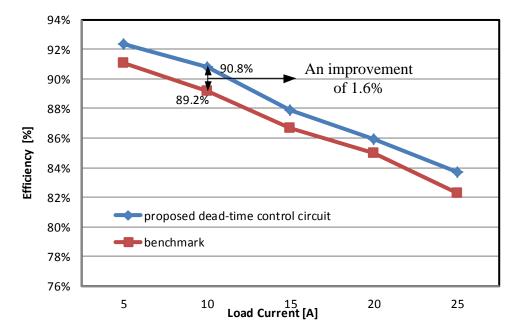

The proposed circuit is verified using PSIM simulation software. In comparison to the adaptive dead-time control using a TPS2832 MOSFET gate driver with minimal of 15ns deadii time, the proposed dead-time control circuit reduces the body diode conduction time of the synchronous MOSFET to 2ns at 10A half load, 12V input, 1.2V output and 500kHz switching frequency. As a result, the efficiency of the buck converter is increased from 89.2% to 90.8%.

## **Table of Contents**

| Abstract                                                         | ü     |

|------------------------------------------------------------------|-------|

| Table of Contents                                                | iv    |

| List of Tables                                                   | vii   |

| List of Figures                                                  | viii  |

| List of Symbols                                                  | xi    |

| List of Abbreviations and SI Units                               | xvi   |

| Acknowledgements                                                 | xvii  |

| Dedication                                                       | xviii |

| Chapter 1 Introduction                                           | 1     |

| 1.1 Introduction of Dead-time in Synchronous Buck Converters     | 1     |

| 1.2 Research Motivation and Objectives                           | 3     |

| 1.2.1 Dead-time Detection Circuit                                | 4     |

| 1.2.2 Dead-time Optimization Circuit                             | 4     |

| Chapter 2 Literature Review                                      | 5     |

| 2.1 Overview                                                     | 5     |

| 2.2 Metal Oxide Semiconductor Field Effect Transistors (MOSFETs) | 5     |

| 2.2.1 Structure of MOSFETs                                       | 5     |

| 2.2.2 MOSFET Mode of Operation                                   | 7     |

| 2.3 Dead-time Control Review                                     | 8     |

| 2.4 Review of Dead-time Detection                                | 10    |

| 2.4.1 Maximum Efficiency Point Tracking                          | 10    |

| 2.4.2 Sensorless Optimization of Dead-time                       | 11    |

| 2.4.3 Logic Gate Used as a Detector                              | 12    |

| 2.4.4 One-step Dead-time Correction                              | 14    |

| 2.4.5 Detecting MOSFET $Q_{det}$                                 | 15    |

| 2.4.6 Adaptive Timing Control with Phase Detector                | 17    |

| 2.5 Summary                                                      | 18    |

| Chapter 3 Proposed Body Diode Detection Circuit                  | 20    |

| 3.1 Overview                                                     | 20    |

|                                                                  |       |

| 3.2 Dead-time Detection Circuit                               |

|---------------------------------------------------------------|

| 3.3 Detection Signal Adjustment Circuit                       |

| 3.4 Implementation of the Detection Diode                     |

| 3.5 Detection Circuit Design Procedure                        |

| 3.5.1 Buck Converter Design                                   |

| 3.5.2 Dead-time Detection Circuit Design                      |

| 3.6 Design Example and Simulation Results                     |

| 3.6.1 Design Example                                          |

| 3.6.2 Simulation Results Using PSIM9                          |

| 3.7 Summary                                                   |

| Chapter 4 Proposed Dead-time Optimization Circuit             |

| 4.1 Overview                                                  |

| 4.2 Dead-time Optimization Circuit                            |

| 4.2.1 The PWM Signal Processing Circuit                       |

| 4.2.2 The Detection Signal Processing Circuit                 |

| 4.2.3 The Dead-time Optimization Circuit                      |

| 4.3 Dead-time Optimization Circuit Design Procedure           |

| 4.3.1 The PWM Signal Processing Circuit Design Procedure      |

| 4.3.2 Detection Signal Processing Circuit Design Procedure    |

| 4.4 Design Example and Simulation Results                     |

| 4.4.1 Design Example                                          |

| 4.4.2 Simulation Results                                      |

| 4.5 Summary                                                   |

| Chapter 5 Simulation Results of the Dead-time Control Circuit |

| 5.1 Overview                                                  |

| 5.2 Closed-loop Control                                       |

| 5.3 PWM Rising Edge with Dead-time Control                    |

| 5.4 Dual PWM Edge Dead-time Control                           |

| 5.5 Comparison with Adaptive Dead-time Control                |

| 5.5.1 Body Diode Conduction Time Comparison70                 |

| 5.5.2 Efficiency and Loss Comparison72                        |

| 5.6 Summary                                                   |

| v                                                             |

| Chapter 6 Conclusions and Future Work |  |

|---------------------------------------|--|

| 6.1 Conclusions                       |  |

| 6.2 Summary of Contributions          |  |

| 6.3 Future Work                       |  |

| References                            |  |

| Appendix A                            |  |

# List of Tables

| Table 3.1 | Operation condition summary for $v_x$ and $D_{det}$ state                       | .22  |

|-----------|---------------------------------------------------------------------------------|------|

| Table 3.2 | Buck converter design parameters                                                | .32  |

| Table 3.3 | Buck converter resultant parameters                                             | .33  |

| Table 3.4 | The selected MOSFETs, inductor and capacitor for the objective buck converter   | .33  |

| Table 3.5 | Detection circuit parameters                                                    | .34  |

| Table 4.1 | The parameters in the design of the PWM signal processing circuit               | .54  |

| Table 4.2 | The parameters in the design of the detection signal processing circuit         | .55  |

| Table 4.3 | Parameters of the comparator LT1394                                             | .55  |

| Table 5.1 | Simulated efficiency measurement data of the buck converter with proposed dead- |      |

|           | time control circuit                                                            | .74  |

| Table 5.2 | Simulated efficiency measurement data of the benchmark circuit                  | .74  |

| Table 5.3 | Power loss reduction by the proposed circuit                                    | .76  |

| Table A.1 | Preferred values for passive circuit components                                 | . 84 |

# List of Figures

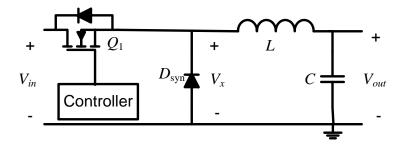

| Figure | 1.1  | The buck converter                                                                           | .1 |

|--------|------|----------------------------------------------------------------------------------------------|----|

| Figure | 1.2  | The synchronous buck converter                                                               | .2 |

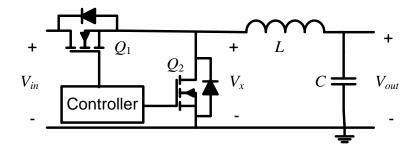

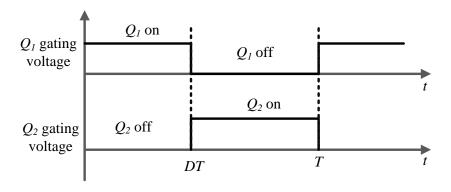

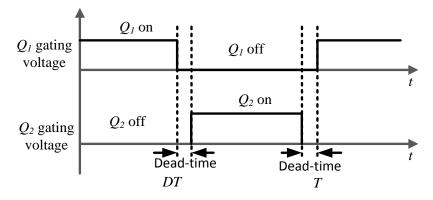

| Figure | 1.3  | Ideal $Q_1$ and $Q_2$ gate signal waveforms                                                  | .2 |

| Figure | 1.4  | Waveforms of $Q_1$ and $Q_2$ gate signals with dead-time                                     | .3 |

| Figure | 2.1  | n-type MOSFET (a) circuit symbol and (b) device structure                                    | .6 |

| Figure | 2.2  | Circuit symbol of a three-pin n-type MOSFET                                                  | .6 |

| Figure | 2.3  | (a) The physical origin of the body diode and, (b) circuit symbol of power                   |    |

|        |      | MOSFET with body diode                                                                       | .7 |

| Figure | 2.4  | The conductive channel between drain and source terminals when a positive $V_{gs}$ is        |    |

|        |      | applied between the gate and source terminals                                                | .7 |

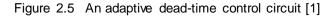

| Figure | 2.5  | An adaptive dead-time control circuit [1]                                                    | .9 |

| Figure | 2.6  | A curve of efficiency versus dead-time                                                       | 0  |

| Figure | 2.7  | Block diagram for sensorless optimization of dead-times                                      | 12 |

| Figure | 2.8  | A NOR gate is utilized to detect body diode conduction in [1]                                | 13 |

| Figure | 2.9  | Voltage waveforms of the switch node voltage, $V_x$ , $Q_2$ gate signal, $V_{gs2}$ , and the |    |

|        |      | NOR gate output                                                                              | 14 |

| Figure | 2.10 | Block diagram for the digital one-step dead-time correction                                  | 15 |

| Figure | 2.11 | The detection MOSFET is implemented on the same die as $Q_2$ and the body                    |    |

|        |      | diodes of the two MOSFETs conduct simultaneously                                             | 16 |

| Figure | 2.12 | The detection MOSFET, $Q_{det}$ , with the dynamic dead-time controller                      | 16 |

| Figure | 2.13 | A dead-time control loop which does not require a digital processor                          | 18 |

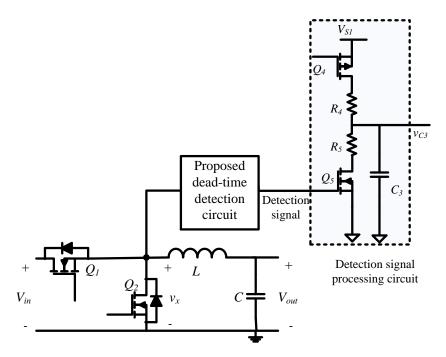

| Figure | 3.1  | Proposed dead-time detection circuit for the synchronous buck converter                      | 21 |

| Figure | 3.2  | The detection signal from the proposed dead-time detection circuit                           | 23 |

| Figure | 3.3  | The adjustment circuit used to modify the detection signal                                   | 24 |

| Figure | 3.4  | Voltage variations at point a, b, and c as well as input and output ports in the             |    |

|        |      | detection signal adjustment circuit                                                          | 25 |

| Figure | 3.5  | (a) The detection diode, $D_{det}$ , is proposed to be manufactured beside the               |    |

|        |      | synchronous MOSFET, $Q_2$ , on the same die and (b) the circuit symbol for this              |    |

|        |      | device                                                                                       | 27 |

|        |      |                                                                                              |    |

| Figure 3.6  | Simulation circuit of the buck converter with the proposed dead-time detection             |

|-------------|--------------------------------------------------------------------------------------------|

|             | circuit                                                                                    |

| Figure 3.7  | Simulated of the synchronous MOSFET voltage, $v_x$ , detection voltage, $v_{det}$ , and    |

|             | rising edge detection flag, <i>v</i> <sub>det_r</sub>                                      |

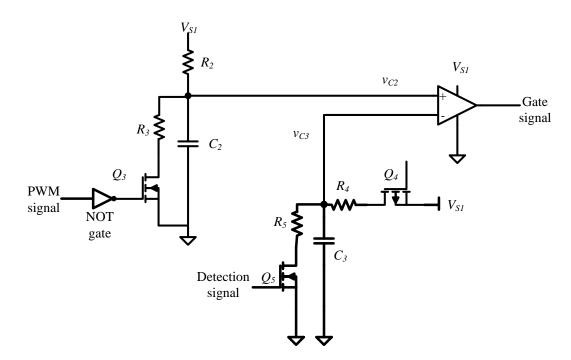

| Figure 4.1  | Block diagram of the proposed dead-time control circuit                                    |

| Figure 4.2  | The objective output waveform from the PWM signal processing circuit with a                |

|             | PWM input signal                                                                           |

| Figure 4.3  | The proposed PWM signal processing circuit                                                 |

| Figure 4.4  | Waveforms for the input signal, $Q_3$ gate signal, and the output signal of the            |

|             | proposed PWM signal processing circuit                                                     |

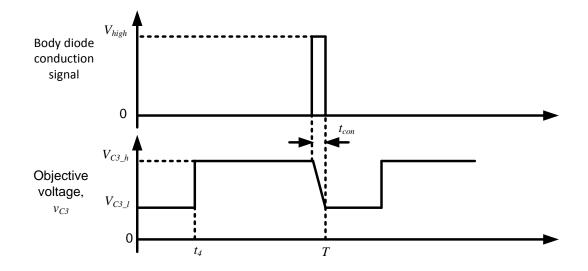

| Figure 4.5  | The expected output waveform of the detection signal processing circuit, where             |

|             | the body diode conduction signal is the input42                                            |

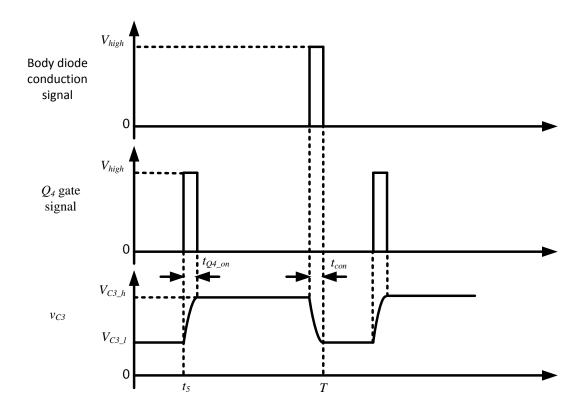

| Figure 4.6  | The proposed detection signal processing circuit                                           |

| Figure 4.7  | The input signal, $Q_4$ gate signal, and output signal of the proposed detection signal    |

|             | processing circuit                                                                         |

| Figure 4.8  | The proposed dead-time optimization circuit                                                |

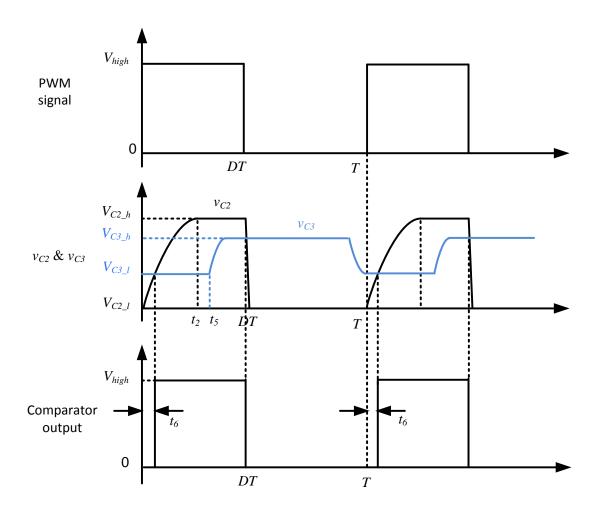

| Figure 4.9  | Signal waveforms of the non-optimized PWM signal, $v_{C2}$ , $v_{C3}$ , and the comparator |

|             | output or the optimized PWM signal in the proposed dead-time optimization                  |

|             | circuit when $t_5$ is smaller than $DT$                                                    |

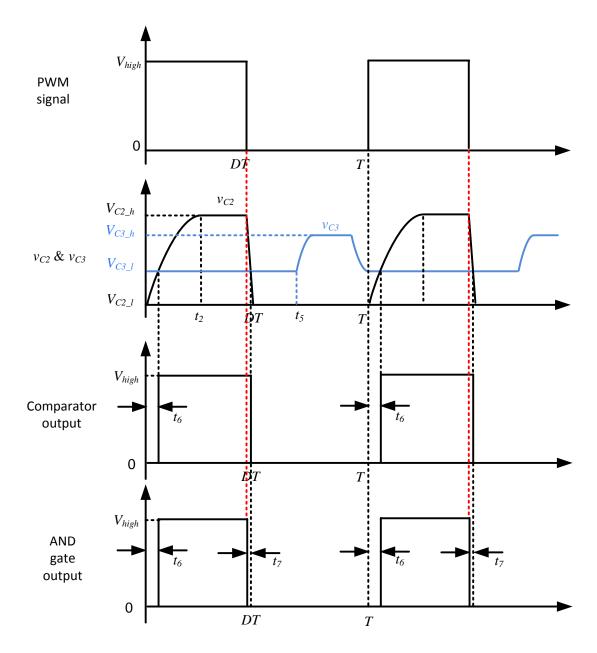

| Figure 4.10 | Signal waveforms of the non-optimized PWM signal, $v_{C2}$ , $v_{C3}$ , and the comparator |

|             | output or the optimized PWM signal in the proposed dead-time optimization                  |

|             | circuit when $t_5$ is greater than $DT$                                                    |

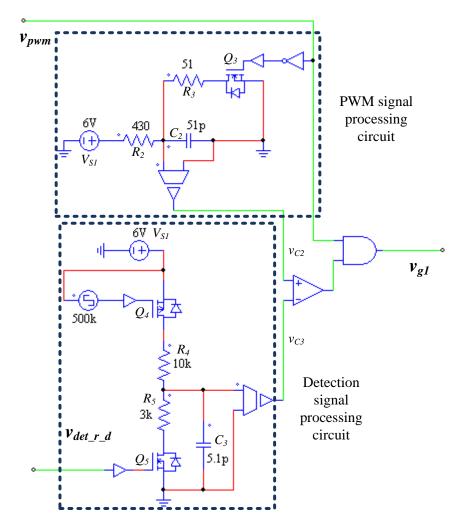

| Figure 4.11 | The dead-time optimization simulation circuit                                              |

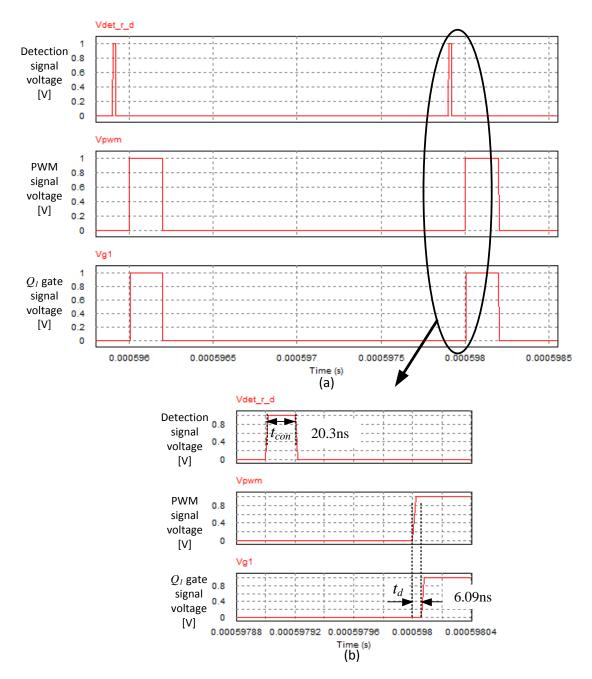

| Figure 4.12 | Simulation results of the dead-time optimization circuit (a) the delayed detection         |

|             | signal for the rising edge, the PWM signal, and the gate signal, (b) the enlarged          |

|             | drawing of the above signals                                                               |

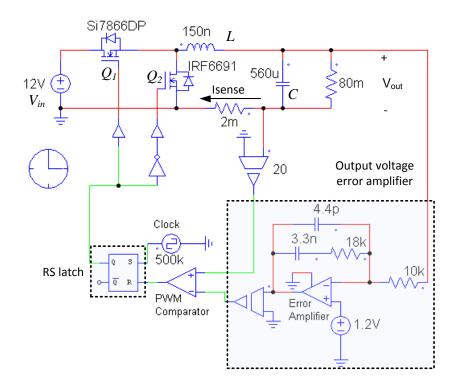

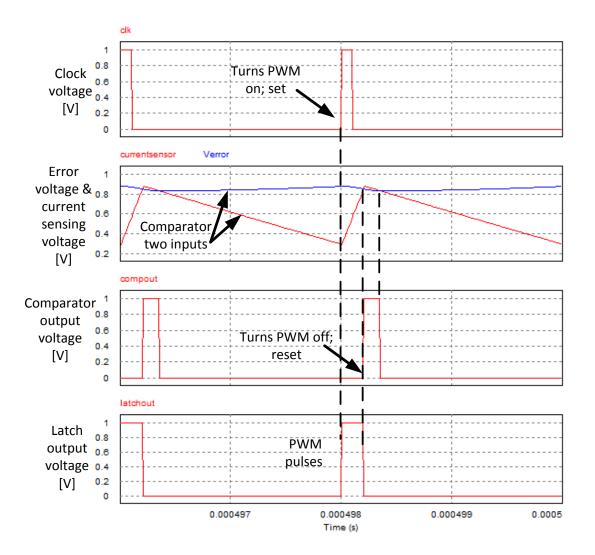

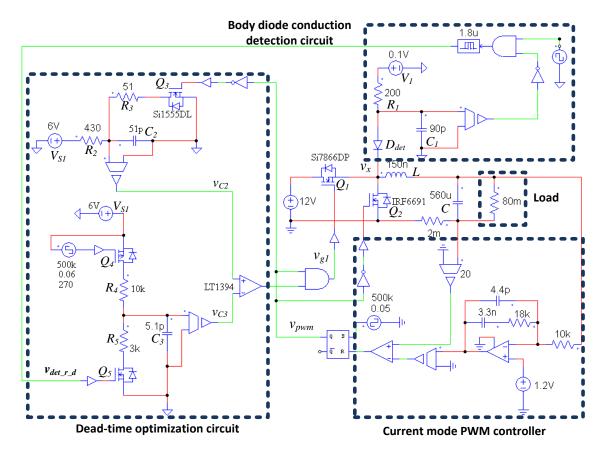

| Figure 5.1  | A current mode PWM controller for the buck converter                                       |

| Figure 5.2  | Waveforms from the current mode PWM controller                                             |

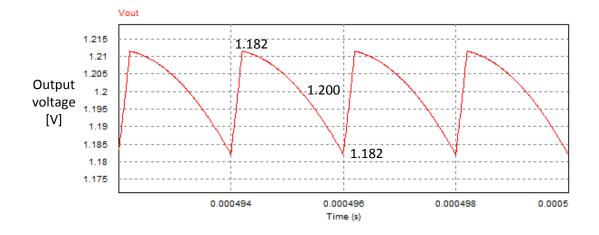

| Figure 5.3  | Four switching cycles of the output voltage of the buck converter                          |

| Figure 5.4  | The proposed dead-time control circuit for the rising edge combined with the               |

|             | current mode PWM control circuit                                                           |

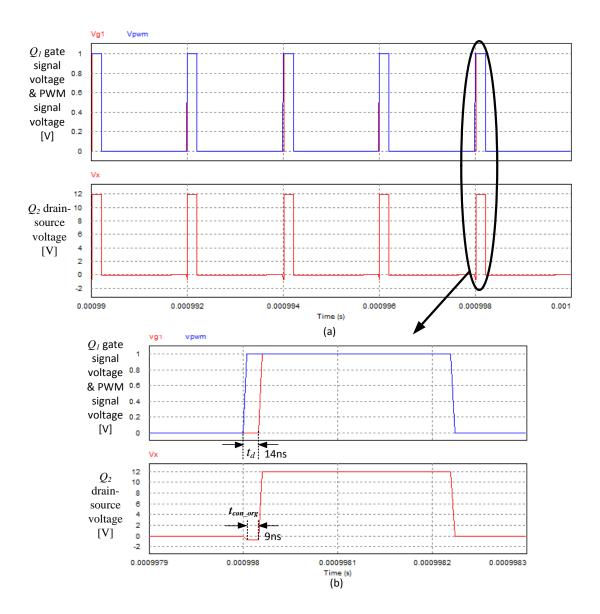

| Figure 5.5  | (a) PWM controller output, $v_{pwm}$ , $Q_I$ gate signal, $v_{gI}$ , and $v_x$ over five switching |    |

|-------------|----------------------------------------------------------------------------------------------------|----|

|             | cycles; and (b) $v_{pwm}$ , $v_{g1}$ , and $v_x$ illustrating one pulse width                      | 65 |

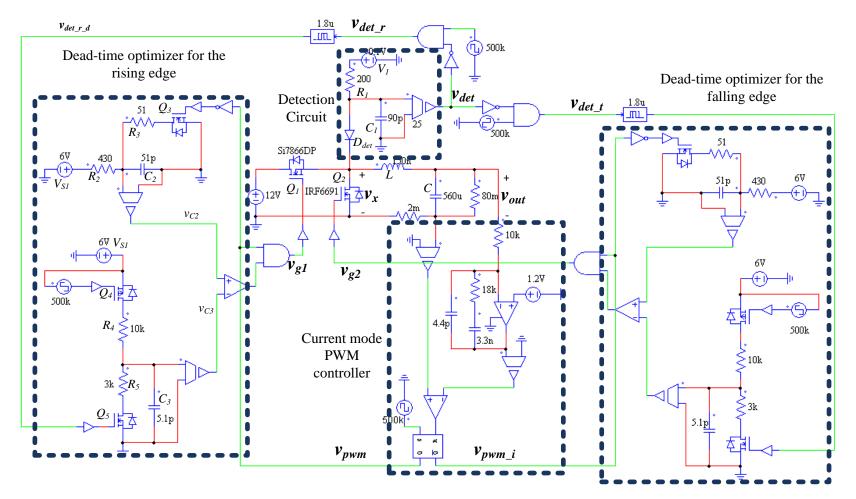

| Figure 5.6  | Complete dead-time optimization circuit including dual edge PWM dead-time                          |    |

|             | control and closed-loop output voltage regulation                                                  | 67 |

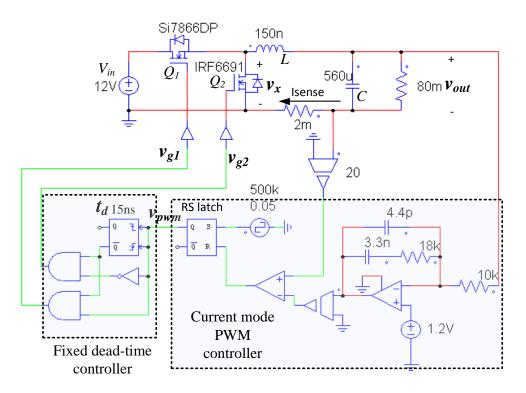

| Figure 5.7  | (a) Waveforms of the $Q_1$ gate signal, PWM signal, $Q_2$ gate signal, inverted PWM                |    |

|             | signal, and the voltage at the joint point of the two MOSFETs; (b) one PWM                         |    |

|             | pulse; (c) body diode conduction time at the rising edge; (d) body diode                           |    |

|             | conduction time at the falling edge                                                                | 69 |

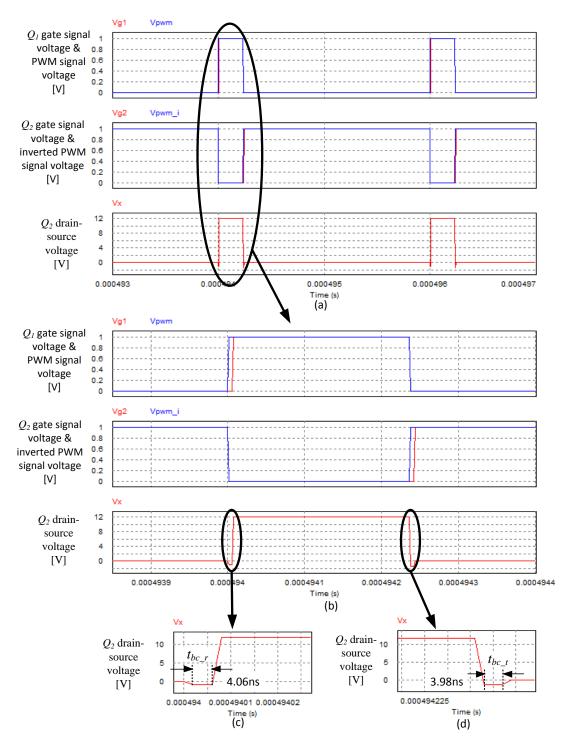

| Figure 5.8  | The benchmark circuit (fixed dead-time control)                                                    | 70 |

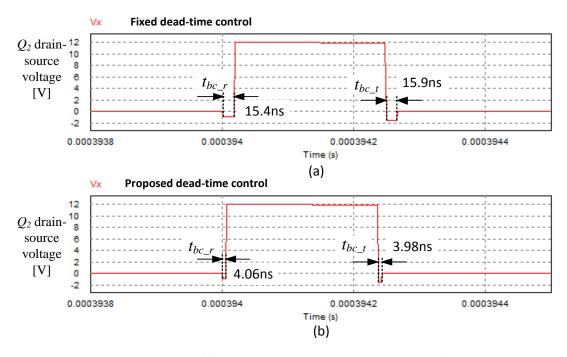

| Figure 5.9  | Buck synchronous MOSFET voltage at a load current of 15A (a) benchmark fixed                       |    |

|             | dead-time control (b) proposed dead-time control                                                   | 71 |

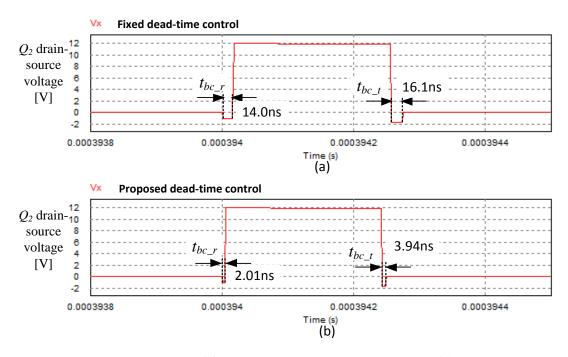

| Figure 5.10 | Buck synchronous MOSFET voltage at a load current of 20A (a) benchmark fixed                       |    |

|             | dead-time control (b) proposed dead-time control                                                   | 72 |

| Figure 5.11 | A comparison of the buck converter efficiency between the proposed circuit and                     |    |

|             | the benchmark circuit at different load currents                                                   | 75 |

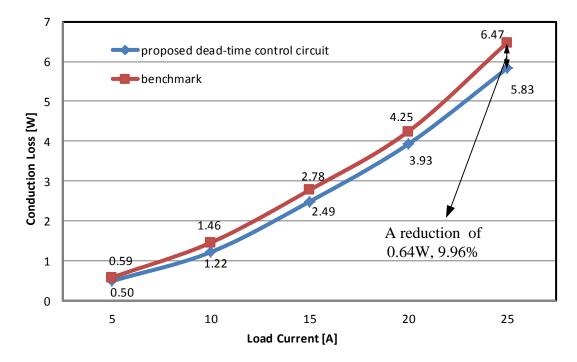

| Figure 5.12 | Comparison of the conduction loss in the proposed circuit and benchmark                            | 77 |

# List of Symbols

| b                     | MOSFET body terminal                                   |

|-----------------------|--------------------------------------------------------|

| С                     | Capacitor of the power stage filter                    |

| $C_1$                 | Capacitor in the detection circuit                     |

| $C_2$                 | Capacitor in the PWM signal processing circuit         |

| $C_3$                 | Capacitor in the detection signal processing circuit   |

| $C_{ctr}$             | Control capacitor                                      |

| $C_{min}$             | Minimal capacitance to limit the output voltage ripple |

| D                     | Duty cycle                                             |

| d                     | MOSFET drain terminal                                  |

| D(n)                  | Moving average duty cycle                              |

| d(n)                  | Current duty cycle                                     |

| D[5:1]                | 5-digits output of the finite state machine            |

| $D_{body}$            | Body diode of the synchronous MOSFET                   |

| $D_{det}$             | Dead-time detection diode                              |

| $D_{syn}$             | Synchronous diode                                      |

| DT                    | Dead-time                                              |

| DT0                   | Initial dead-time value                                |

| DW                    | Dead-time width                                        |

| е                     | the base of natural logarithm                          |

| $E_{ff}(n)$           | Buck converter efficiency at current switching cycle   |

| $E_{ff}(n-1)$         | Buck converter efficiency at previous switching cycle  |

| $f_s$                 | Switching frequency                                    |

| 8                     | MOSFET gate terminal                                   |

| <i>g</i> 1            | Gate signal for the power MOSFET                       |

| <i>g</i> <sub>2</sub> | Gate signal for the synchronous MOSFET                 |

| $I_B$                 | Input bias current of a comparator                     |

| $i_{CI}$              | Capacitor $C_1$ current                                |

| $i_{C2}$              | Capacitor $C_2$ current                                |

| $i_{C3}$              | Capacitor $C_3$ current                                |

| $I_d$                                    | Drain current of MOSFETs                                                |

|------------------------------------------|-------------------------------------------------------------------------|

| $i_{Dbody}$                              | Body diode current of the synchronous MOSFET                            |

| $i_{Ddet}$                               | Detection diode current                                                 |

| $I_{det}$                                | Drain-source current of the detection MOSFET                            |

| $I_{ds}$                                 | Drain-source current of MOSFETs                                         |

| $\dot{i}_{in}$                           | Input current of the buck converter                                     |

| $I_{in\_avr}$                            | Average input current of the buck converter                             |

| $I_{in\_c}$                              | Input current of a comparator                                           |

| $I_L$                                    | Inductor current                                                        |

| $I_{load}$                               | Load current of the buck converter                                      |

| $I_{Load}$                               | Average load current                                                    |

| $I_{Q2}$                                 | Drain-source current of the synchronous MOSFET                          |

| $i_{R2}$                                 | Resistor $R_2$ current                                                  |

| <i>i</i> <sub><i>R</i><sup>3</sup></sub> | Resistor $R_3$ current                                                  |

| $i_{R4}$                                 | Resistor $R_4$ current                                                  |

| $i_{R5}$                                 | Resistor $R_5$ current                                                  |

| Κ                                        | Magnification parameter of the voltage amplifier                        |

| $K_{rip}\%$                              | Output voltage peak-to-peak ripple                                      |

| L                                        | Inductor of the power stage filter                                      |

| $L_{cri}$                                | The critical inductance that ensures continuous current mode            |

| $O_{reg}$                                | Flip-flop output                                                        |

| $P_{in}$                                 | Average input power of the buck converter                               |

| $p_{in}$                                 | Input power of the buck converter                                       |

| $P_{ls}$                                 | Power loss at the buck converter                                        |

| $P_{lsl}$                                | Power loss of the buck converter with the proposed dead-time controller |

| $P_{ls2}$                                | Power loss of the buck converter with the benchmark circuit             |

| Pout                                     | Average output power of the buck converter                              |

| $p_{out}$                                | Output power of the buck converter                                      |

| $Q_1$                                    | Power MOSFET of the buck converter                                      |

| $Q_2$                                    | Synchronous MOSFET of the buck converter                                |

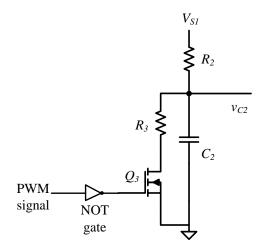

| $Q_3$                                    | MOSFET in the PWM signal processing circuit                             |

| $Q_4$                                    | Charging up MOSFET in the detection signal processing circuit           |

| $Q_5$                        | Discharging MOSFET in the detection signal processing circuit                    |

|------------------------------|----------------------------------------------------------------------------------|

| $Q_{\scriptscriptstyle det}$ | Dead-time detection MOSFET                                                       |

| $Q_{g}$                      | Gate charge of a MOSFET                                                          |

| $R_1$                        | Resistor in the detection circuit                                                |

| $R_2$                        | Charging up resistor in the PWM signal processing circuit                        |

| $R_3$                        | Discharging resistor in the PWM signal processing circuit                        |

| $R_4$                        | Charging up resistor in the detection signal processing circuit                  |

| $R_5$                        | Discharging resistor in the detection signal processing circuit                  |

| $R_L$                        | Equivalent load resistance                                                       |

| $R_{on}$                     | On resistance of MOSFETs                                                         |

| S                            | MOSFET source terminal                                                           |

| $SiO_2$                      | Silicon dioxide                                                                  |

| t                            | Time variable                                                                    |

| Т                            | Switching period                                                                 |

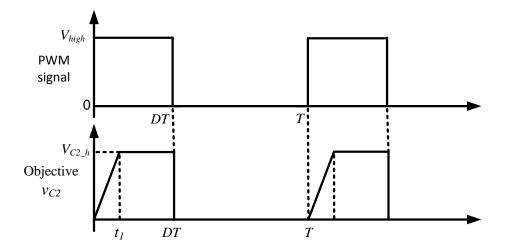

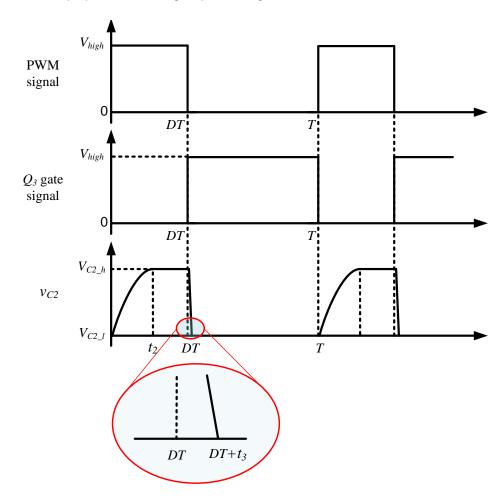

| $t_1$                        | Objective rising time of $v_{C2}$                                                |

| $t_2$                        | Experimental rising time of $v_{C2}$ at the proposed circuit                     |

| $t_3$                        | Experimental falling time of $v_{C2}$ at the proposed circuit                    |

| $t_4$                        | Objective time to charge up $C_3$ in each switching cycle                        |

| $t_5$                        | Experimental time starting to charge up $C_3$ at proposed circuit                |

| $t_6$                        | Delay generated by the optimization circuit for the rising edge of the PWM pulse |

| $t_7$                        | Delay caused by the optimization circuit at the trailing edge of the PWM pulse   |

| $t_{bc\_r}$                  | Body diode conduction time at the rising edge                                    |

| $t_{bc_t}$                   | Body diode conduction time at the trailing edge                                  |

| t <sub>con</sub>             | Detected body diode conduction time, output of the detection circuit             |

| $t_{con\_org}$               | Original body diode conduction time                                              |

| $t_d$                        | Time delay generated by dead-time controllers                                    |

| $t_d(n)$                     | Dead-time for the current switching cycle                                        |

| $t_d(n-1)$                   | Dead-time of the previous switching cycle                                        |

| $t_{d1}$                     | Time delay at the rising edge of the PWM pulse                                   |

| $t_{d2}$                     | Time delay at the trailing edge of the PWM pulse                                 |

| $t_{do}$                     | Optimal dead-time                                                                |

| $t_{off}$                    | Switch off time of a MOSFET                                                      |

|                              |                                                                                  |

| ton                           | Switch on time of a MOSFET                                                    |

|-------------------------------|-------------------------------------------------------------------------------|

| $t_{pd}$                      | Propagation delay of logic gates                                              |

| $t_{Q4\_on}$                  | Duration of the MOSFET $Q_4$ being turned on                                  |

| $t_{rr}$                      | Reverse recovery time of a diode                                              |

| $V_{I}$                       | Voltage source for the detection circuit                                      |

| $V_2$                         | Voltage source for signal shifting                                            |

| Va                            | Voltage signal at point a in the adjustment circuit                           |

| $v_b$                         | Voltage signal at point b in the adjustment circuit                           |

| V <sub>c</sub>                | Voltage signal at point c in the adjustment circuit                           |

| V <sub>Cl</sub>               | Voltage across the capacitor $C_1$ in the detection circuit                   |

| <i>V</i> <sub>C2</sub>        | Voltage across the capacitor $C_2$ in the PWM signal processing circuit       |

| $V_{C2\_h}$                   | High voltage value of $v_{C2}$                                                |

| $V_{C2\_l}$                   | Low voltage value of $v_{C2}$                                                 |

| <i>V</i> <sub><i>C</i>3</sub> | Voltage across the capacitor $C_3$ in the detection signal processing circuit |

| $V_{C3\_h}$                   | High voltage value of $v_{C3}$                                                |

| $V_{C3_l}$                    | Low voltage value of $v_{C3}$                                                 |

| <i>V<sub>Ddet</sub></i>       | Anode voltage of the detection diode                                          |

| <i>V<sub>det</sub></i>        | Dead-time detection signal voltage                                            |

| $V_{det_r}$                   | Detection signal voltage for the rising edge of the PWM pulse                 |

| $V_{det_t}$                   | Detection signal voltage for the trailing edge of the PWM pulse               |

| V <sub>dmax</sub>             | Maximal value of the dead-time detection voltage                              |

| $V_{dmin}$                    | Minimal value of the dead-time detection voltage                              |

| $V_{ds}$                      | Drain-source voltage of MOSFETs                                               |

| $V_{F\text{-}body}$           | Forward voltage of the synchronous MOSFET body diode                          |

| $V_{F-det}$                   | Forward voltage of the detection diode                                        |

| V <sub>g1</sub>               | MOSFET $Q_1$ gate signal                                                      |

| $V_{g2}$                      | MOSFET $Q_2$ gate signal                                                      |

| $V_{gs}$                      | Gate-source voltage of MOSFETs                                                |

| $V_{gs2}$                     | Gate-source voltage of the synchronous MOSFET                                 |

| $V_{high}$                    | Voltage value of logic high                                                   |

| V <sub>in</sub>               | Input voltage of the buck converter                                           |

| $V_{in}$                      | Average input voltage of the buck converter                                   |

|                               |                                                                               |

| $V_{logic}$                 | Analog voltage level of a logic gate                                              |

|-----------------------------|-----------------------------------------------------------------------------------|

| $V_{out}$                   | Average output voltage of the buck converter                                      |

| V <sub>out</sub>            | Output voltage of the buck converter                                              |

| V <sub>out</sub> rms        | Root-mean-square of the buck converter output voltage                             |

| $v_{pwm}$                   | Output of a PWM controller                                                        |

| $v_{pwm_i}$                 | Inverted output of a PWM controller                                               |

| $v_{R2}$                    | Voltage across the resistor $R_2$                                                 |

| $V_{R3}$                    | Voltage across the resistor $R_3$                                                 |

|                             | Voltage across the resistor $R_4$                                                 |

| <i>V<sub>R4</sub></i>       | Voltage across the resistor $R_5$                                                 |

| $v_{R5}$<br>$V_{SI}$        | Voltage source for the control circuit                                            |

|                             |                                                                                   |

| $V_{th}$                    | Threshold voltage of MOSFETs                                                      |

| $V_{x}$                     | Voltage at the junction point of the power MOSFET and the synchronous device      |

| α                           | Low pass filter factor; between 0 and 1                                           |

| $\varDelta E_{ff}$          | Efficiency improvement                                                            |

| $\Delta P\%$                | Power loss reduction percentage                                                   |

| $\Delta P_{ls}$             | Power loss reduction by the proposed circuit                                      |

| $\Delta t_d$                | Dead-time step                                                                    |

| $\Delta V_{out-pp} N_{out}$ | Peak-to-peak output voltage ripple                                                |

| η                           | Power efficiency of buck converters                                               |

| $	au_1$                     | Time constant of the detection circuit                                            |

| $	au_2$                     | Time constant of the rising transient at the PWM signal processing circuit        |

| $	au_3$                     | Time constant of the falling transient at the PWM signal processing circuit       |

| $	au_4$                     | Time constant of the rising transient at the detection signal processing circuit  |

| $	au_5$                     | Time constant of the falling transient at the detection signal processing circuit |

| • 3                         | This constant of the fulling transfert at the detection signal processing chedit  |

## List of Abbreviations and SI Units

| А      | Amperes                                     |

|--------|---------------------------------------------|

| С      | Coulombs                                    |

| DC     | Direct Current                              |

| DPWM   | Digital Pulse Width Modulation              |

| F      | Farads                                      |

| FSM    | Finite State Machine                        |

| Н      | Henries                                     |

| Hz     | Hertz                                       |

| IC     | Integrated Chips                            |

| k      | Kilo (10 <sup>3</sup> )                     |

| Μ      | Mega (10 <sup>6</sup> )                     |

| m      | Milli (10 <sup>-3</sup> )                   |

| MEPT   | Maximum Efficiency Point Tracking           |

| MOSFET | Metal Oxide Silicon Field Effect Transistor |

| n      | Nano (10 <sup>-9</sup> )                    |

| n-type | Negative-type                               |

| PID    | Proportion-integral-derivative              |

| p-type | Positive-type                               |

| S      | Seconds                                     |

| V      | Volts                                       |

| W      | Watts                                       |

| μ      | Micro (10 <sup>-6</sup> )                   |

| Ω      | Ohms                                        |

## Acknowledgements

First, I want to thank my supervisor, Dr. Wilson Eberle, for his patience, support, and help throughout my master's study in the School of Engineering at UBC, and especially his guidance for my thesis project. Moreover, I want to thank my colleagues in the Power Electronics Group in for their helpful advice.

I would also like to thank my family for their unconditional support during my work on the thesis. My father, Renxiang Mei, my mother, Huamei Xu, my sister Zhihong Mei and my 2-year old niece, Yi Chen have greatly encouraged me through the challenge during my study.

At last, I want to thank my dear friends in Kelowna, Man (Sapphire) Ding, Xian (Peter) Jin, Feng (Vicki) Wei, Xuegui Song, Xianchang Li, Faria and Hannah. They have helped me tremendously during my stay in Kelowna. To my parents

## **Chapter 1**

## Introduction

## 1.1 Introduction of Dead-time in Synchronous Buck Converters

A buck converter is a step down DC to DC conversion circuit. Figure 1.1 is the simplest and most widely used DC-DC converter topology. It is a switching mode power supply, with a frequency generally ranging from 50kHz to 1MHz. It is often used in modern low voltage DC power supplies, such as battery-supplied electronics, point of load converters and microprocessor power supplies.

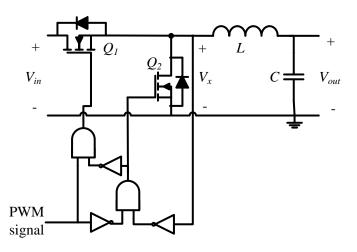

Figure 1.1 The buck converter

A synchronous buck converter uses a power MOSFET to replace the rectifier diode in order to achieve higher efficiency, because for low output voltage applications, a MOSFET exhibits lower conduction loss than a diode. Figure 1.2 illustrates the circuit of a synchronous buck converter, and Figure 1.3 shows its ideal gate-to-source driving waveforms.  $Q_1$  is called the control switch while  $Q_2$  is called the rectifier switch or synchronous rectifier. Ideally,  $Q_1$  and  $Q_2$ are turned on in a complementary fashion such that at t=DT,  $Q_2$  is turned on while  $Q_1$  is turned off simultaneously, and vice versa at t=0 or T.

Figure 1.2 The synchronous buck converter

Figure 1.3 Ideal  $Q_1$  and  $Q_2$  gate signal waveforms

Due to the non-zero turn-on and turn-off time of power MOSFETs, a dead-time needs to be inserted into the transition intervals, as shown in Figure 1.4. Without dead-time, it is possible that  $Q_2$  will turn-on when  $Q_1$  is not totally off, resulting in a shoot through current from the source through  $Q_1$  and  $Q_2$  to ground, leading to reliability problems and excessive power loss. Alternately, if the dead-time is longer than required such that  $Q_2$  is not turned-on when  $Q_1$  has been off, the body diode of  $Q_2$  is forced on, providing a continuous path for the inductor current. Generally, a body diode has greater conduction loss than a MOSFET channel. As a result, excessive dead-time results in a lower efficiency for the converter.

Figure 1.4 Waveforms of  $Q_1$  and  $Q_2$  gate signals with dead-time

## **1.2 Research Motivation and Objectives**

High efficiency is a requirement for the buck converter and all power converters. Their ability to achieve high efficiency (e.g. typically > 85%) is one of the reasons that buck converters are so widely used in power conversion. Therefore, much research has been done to increase efficiency. One method is to reduce the body diode conduction of the synchronous MOSFET in the buck converter.

Buck converters typically switch at frequencies between 200kHz and 500kHz. High switching frequencies result in better performance and design characteristics in many aspects, including a fast transient response, a smaller inductor, and a smaller capacitor. However, frequency dependent losses including switching loss, gate loss and body diode conduction loss increases with frequency. High switching loss and gate loss are not easily addressed; however, fast dead-time control circuits can minimize dead-time related conduction loss in order to achieve high efficiency.

The objective of this thesis is to propose a dead-time control circuit that reduces dead-time to a minimum value in comparison to benchmark circuits used presently in industry. A dead-time control circuit requires dead-time detection and dead-time optimization circuits, which are discussed in the following subsections.

## **1.2.1 Dead-time Detection Circuit**

The dead-time detection circuit needs to be sensitive. Otherwise it is impossible for the control circuit to achieve a small dead-time if the detector cannot even sense body diode conduction. Moreover, the detection circuit should be able to generate an output signal that precisely tells the body diode conduction time. Without doubt, it is beneficial if the circuit can be made denser.

### 1.2.2 Dead-time Optimization Circuit

Dead-time optimization circuits can be either analog or digital. However, most dead-time controllers are digital since it is relatively simple to insert dead-time to the PWM pulses. An important objective for the circuit is high speed so that the processing time is much less than the switching period which can be very small for high frequencies. Finally, since the timing of the pulses is critical for proper efficient converter operation, the optimization circuit should synchronize the gate signals for the two MOSFETs.

## **Chapter 2**

## **Literature Review**

## 2.1 Overview

In this chapter, the MOSFET semiconductor device is briefly introduced, and then a review of dead-time control circuits is presented. The advantages and shortcomings of the existing circuits are compared and summarized, thereby establishing the technical modification for the work presented in the remainder of the thesis.

### 2.2 Metal Oxide Semiconductor Field Effect Transistors (MOSFETs)

Among semiconductor devices, Metal Oxide Semiconductor Field Effect Transistors (MOSFETs) are the most widely used switching devices in low power and high frequency power conversion applications, due to desirable characteristics including, low on-state voltage drop, low gate drive currents, high current handling capability, and low cost. In this section, the basic structure and models of operation of power MOSFETs is introduced.

#### 2.2.1 Structure of MOSFETs

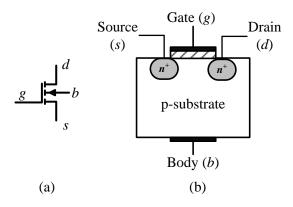

MOSFETs are semiconductor devices with four terminals including the drain, source, gate, and body. The semiconductor material used for the source and drain terminals in MOSFETs are categorized as n-type or p-type. For n-type MOSFETs, n-type source and drain are added to the body of p-type silicon substrates. A layer of insulative material, silicon dioxide ( $SiO_2$ ), is then manufactured on top of the substrates. Figure 2.1 illustrates the circuit symbol and device structure of an n-type MOSFET.

Figure 2.1 n-type MOSFET (a) circuit symbol and (b) device structure

For power MOSFETs, the body terminal is connected to the source, so the device effectively becomes a three-terminal device. Figure 2.2 illustrates the three-pin symbol of an n-type MOSFET.

Figure 2.2 Circuit symbol of a three-pin n-type MOSFET

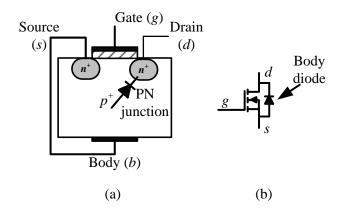

An intrinsic p-n junction exists between the  $p^+$  body region and the implanted  $n^+$  region, as shown in Figure 2.3 (a). This p-n junction is called the body diode in power MOSFETs. Figure 2.3 (b) illustrates the circuit symbol of a power MOSFET with a body diode.

Figure 2.3 (a) The physical origin of the body diode and, (b) circuit symbol of power MOSFET with body diode

#### 2.2.2 MOSFET Mode of Operation

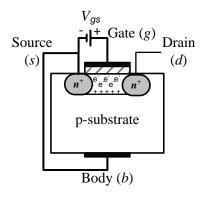

This subsection presents the modes of operation for a MOSFET. When a positive voltage source,  $V_{gs}$ , is applied between the gate and source terminals, as shown in Figure 2.4, the gate, the insulative silicon oxide and the base create a capacitive region. The positive voltage draws negative particles to the top of the p-substrate, thus forming a conductive electric channel. Current flows in this channel if another voltage source is present across the drain and source terminals.

Figure 2.4 The conductive channel between drain and source terminals when a positive  $V_{gs}$  is applied between the gate and source terminals

As a first order approximation, MOSFETs have three operation modes depending on the

magnitude of the applied voltages.

1) Cutoff mode

This mode occurs when  $V_{gs} < V_{th}$ , where  $V_{th}$  is the threshold of the device. That is, the gatesource voltage is too small to enable the formation of the conductive channel. This mode is the "off" mode, since the device cannot conduct current.

2) Triode mode

When  $V_{gs} > V_{th}$ , but  $V_{ds} < V_{gs}$  -  $V_{th}$ , the MOSFET device works like a resistor. The magnitude of the current,  $I_{ds}$  is linearly related to  $V_{ds}$  for a given value of  $V_{gs}$ .

3) Saturation mode

The device is called saturated when  $V_{gs} > V_{th}$ , and  $V_{ds} > V_{gs} - V_{th}$ . The value of  $I_{ds}$  is controlled by  $V_{gs}$  and is independent of  $V_{ds}$ .

The resistance between the drain and source terminals in the triode mode is called the on resistance, which is an important parameter in every MOSFET datasheet. The on resistance of a power MOSFET usually lies in the milliohm range, so it is typically ignored, except for use in loss calculations.

Due to high drain current and low drain voltage, power MOSFETs are intended to operate in the triode mode (low resistance) in the on state, and in the cutoff mode (very high resistance) in the off state.

#### 2.3 Dead-time Control Review

Dead-time control techniques can be divided into three types - fixed dead-time control, adaptive dead-time control, and predictive dead-time control [1].

With fixed dead-time, a constant uncontrolled dead-time is added to the gate signal for the

synchronous MOSFET. The fixed dead-time must be long enough to avoid over shoot in any conditions, regardless of changes in temperature, load, and the type of MOSFET device. Therefore, to avoid any chance of shoot through, the dead-time is usually much longer than that needed in most situations, resulting in excessive body diode conduction.

Adaptive dead-time control, however, is able to adjust the dead-time according to the current conditions in the circuit. An example of an adaptive dead-time control circuit is shown in Figure 2.5 [1]. With this technique, there is a feedback loop, which acts to detect body diode conduction. As a result, this method can only decrease body diode conduction rather than eliminate it.

The third type of dead-time control is predictive dead-time control, which uses information of the previous switching cycle to determine the dead-time needed in the current cycle. Depending on the numbers of cycles needed for the buck converter to reach steady state, predictive dead-time control can be further categorized into unit bit delay adjustment and one step adjustment.

### 2.4 Review of Dead-time Detection

### 2.4.1 Maximum Efficiency Point Tracking

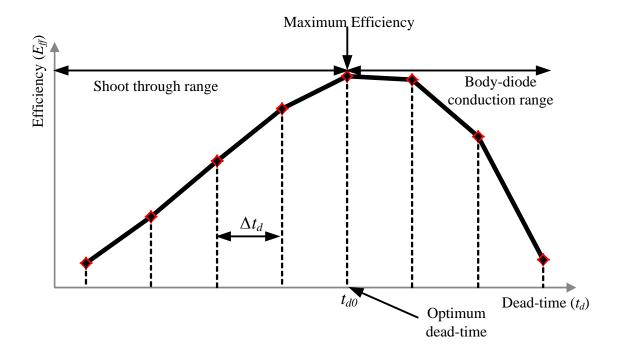

A method named "Maximum Efficiency Point Tracking" (MEPT) was proposed in [2]. This method was originally used in solar arrays, and later extended to the field of dead-time control. Figure 2.6 shows the efficiency curve of a buck converter in a certain dead-time range.  $t_d(n)$ represents dead-time values at current switching cycle, and  $E_{ff}(n)$  is the corresponding efficiency. Similarly, the previous step dead-time is  $t_d(n-1)$  and the efficiency  $E_{ff}(n-1)$ .  $\Delta E_{ff}$  and  $\Delta t_d$  are given by (2.1) and (2.2).

$$\Delta E_{ff} = E_{ff}(n) - E_{ff}(n-1)$$

(2.1)

$$\Delta t_d = t_d(n) - t_d(n-1) \tag{2.2}$$

Figure 2.6 A curve of efficiency versus dead-time

If  $\Delta E_{ff}$  and  $\Delta t_d$  have the same sign, that is both being positive or negative, dead-time for the

coming switching cycle is that of last switching cycle plus one step dead-time value,  $\Delta t_d$ ; otherwise, the dead-time is decreased by one step. The dead-time controller starts with a fixed worse-case dead-time, which ensures safety operating at all conditions. The dead-time is then modified step by step until the maximum efficiency is found.

One advantage of this method is that the algorithm is simple. The input current is sensed and used instead of maximum efficiency, since the lowest input current corresponds to the highest efficiency, if the output voltage is regulated. Therefore, an extra sensor is not needed because the input current is usually monitored for safety reasons. Another advantage is that the controller will adapt to the optimum dead-time if the load or input voltage changes. Disadvantages include long transient times and limited accuracy, depending on the step size of the dead-time. Since dead-time is changed step by step rather than continuously, there is a high chance that the actual optimum dead-time exists between two stepped dead-time values.

#### 2.4.2 Sensorless Optimization of Dead-time

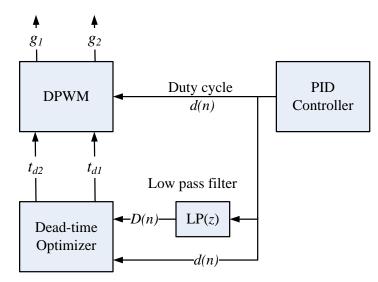

Another digital algorithm of dead-time control named sensorless optimization is proposed in [3]. The block diagram of this dead-time controller is provided in Figure 2.7. The PID controller adjusts the duty cycle to regulate the output voltage of the buck converter. In steady state, the optimum dead-time value produces the lowest duty cycle value. The output of the PID compensator is utilized to find the optimum dead-time. The dead-time optimizer starts with a fixed maximum dead-time value, which ensures safe operation of the buck converter under all conditions. Next, the dead-time is decreased step by step until it reaches the dead-time value which yields the lowest duty cycle. To avoid sudden changes, a moving average duty cycle, D(n), is used in the algorithm rather than the current duty cycle, d(n). The moving average duty cycle, given by (2.3), functions as a low pass filter.

$$D(n) = (1 - \alpha)D(n - 1) + \alpha d(n)$$

(2.3)

where  $\alpha$  is a factor between 0 and 1 and D(n) is equal to d(n) in steady state.

Figure 2.7 Block diagram for sensorless optimization of dead-times

There are several similarities between this sensorless dead-time optimizer and the previous MEPT algorithm. First, no extra sensor is needed to detect dead-time. In both algorithms, detection signals are generated from parameters which already exist in the voltage regulation loop. Second, both dead-time controllers start from a preset maximum value and are decreased step by step until the optimum value is found. For these reasons, the two algorithms are similar such that they share the same advantages and disadvantages.

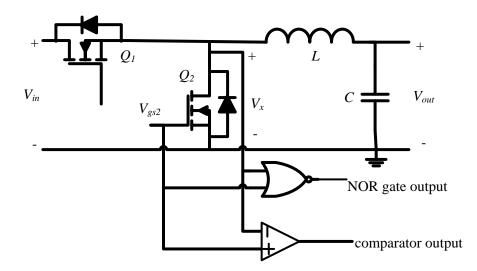

## 2.4.3 Logic Gate Used as a Detector

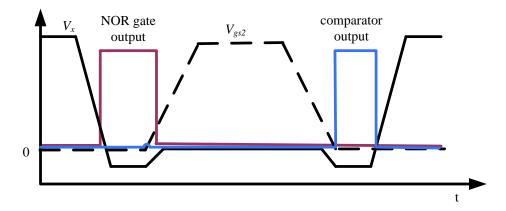

A NOR gate and a comparator are used to detect the body diode conduction of MOSFET  $Q_2$ in [1]. The circuit is provided in Figure 2.8. Waveforms of the NOR gate output, comparator output,  $Q_2$  drain-to-source voltage,  $V_x$ , and gate-to-source voltage,  $V_{gs2}$ , are provided in Figure 2.9. Only when both  $V_{gs2}$  and  $V_x$  are low will the NOR gate output be high. Therefore, the presence of a high NOR gate output illustrates body diode conduction and therefore excess deadtime. The dead-time in the controller is decreased by one step size for the next switching cycle until the high pulse of the NOR gate output is eliminated. When the NOR gate output remains low, a one-step size delay is added to the dead-time for the next switching cycle. As a result, a two-step dead-time size dithering occurs in steady state. The NOR gate is used to detect the body diode conduction before  $Q_2$  turns on; while the comparator is used to detect body diode conduction after  $Q_2$  turns off. This leads to complications in the control circuit and in addition, it takes several switching cycles to eliminate body diode conduction.

Figure 2.8 A NOR gate is utilized to detect body diode conduction in [1]

Figure 2.9 Voltage waveforms of the switch node voltage,  $V_x$ ,  $Q_2$  gate signal,  $V_{gs2}$ , and the NOR gate output

## 2.4.4 One-step Dead-time Correction

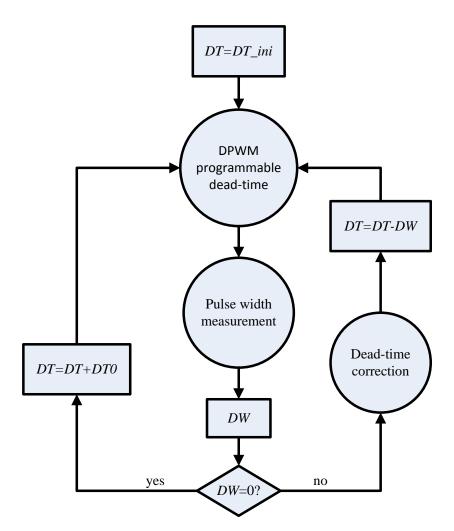

To avoid these shortcomings, an improved method, called "one-step digital dead-time correction" was proposed in [4]. A block diagram of this method is provided in Figure 2.10. The comparator in [1] is eliminated and the NOR gate is used to detect body diode conduction during the turn on and turn off transition intervals. This simplifies the circuit and improves its performance, since the NOR gate is faster than the comparator. After dead-time detection is achieved with the NOR gate, a pulse width measurement is implemented to measure the width of the NOR gate output pulse, *DW*. In the next switching cycle, *DW* is subtracted from the dead-time, *DT*. Theoretically, the body diode conduction can be eliminated in the next switching cycle rather than in several switching cycles, so "one-step correction" can be achieved. However, as in [1], a step-size dead-time value, *DTO*, is added when the output of the NOR gate remains low. Therefore, the dithering at the two-step size window remains as in [1].

Figure 2.10 Block diagram for the digital one-step dead-time correction

## 2.4.5 Detecting MOSFET Q<sub>det</sub>

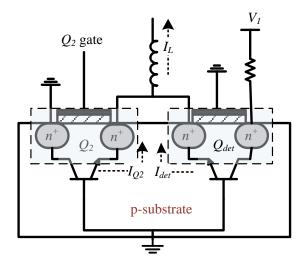

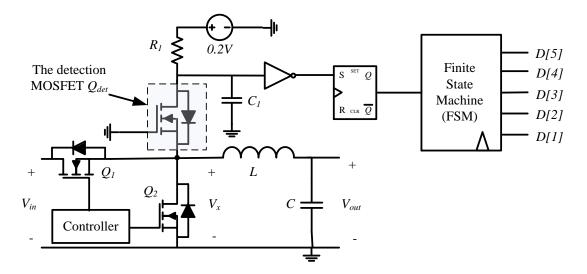

Dynamic dead-time control is introduced in [5]. Instead of a NOR gate, or a comparator, a detecting MOSFET,  $Q_{det}$ , is used. This MOSFET can be fabricated on the same die as the synchronous rectifier MOSFET  $Q_2$ , as illustrated in Figure 2.11. The dynamic dead-time control circuit with the buck converter is illustrated in Figure 2.12. When the body diode of  $Q_2$  is on,  $V_x$  is slightly negative (e.g. -0.7V). In addition, since  $Q_{det}$  is in parallel with  $Q_2$ , its body diode is also forced on. Therefore, when the body diode of  $Q_2$  is on, the voltage across  $C_1$  decreases. The time

that  $C_1$  voltage stays low reflects the body diode conduction time of  $Q_2$ . The finite state machine (FSM) controls a binary-weighted capacitor, which in turn adjusts the dead-time in the dead-time adjustor (DTA). If the output of the RS flip-flop,  $O_{reg}$ , is '1', the dead-time will be reduced in the next switching cycle; while if  $O_{reg}$  is '0', the FSM output, D[5:1], is increased, and therefore the next switching cycle dead-time is increased.

Figure 2.11 The detection MOSFET is implemented on the same die as  $Q_2$  and the body diodes of the two MOSFETs conduct simultaneously

Figure 2.12 The detection MOSFET,  $Q_{det}$ , with the dynamic dead-time controller

This dynamic dead-time control is similar to other digital controllers in many aspects except for the body diode conduction detection circuit, which has the built-in detecting MOSFET, unique from other detecting methods. This built-in detector is able to make the integrated control circuit denser than a separate discrete circuit. In addition, it reduces the influence of parasitic electric parameters between the sensor and the  $Q_2$  body diode, eliminating the wire between them. As a result, this sensor can be more accurate than the methods in [1]-[4]. Furthermore, this analog detecting technique is also suitable for an analog controller and thus the disadvantages of digital controllers can be eliminated.

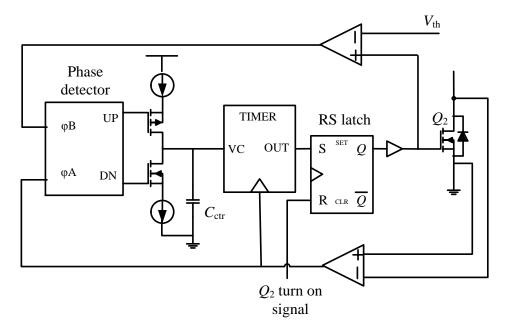

### 2.4.6 Adaptive Timing Control with Phase Detector

In [9], dead-time control is achieved without the need for a sophisticated digital signal processor. The control circuit presented in [9] is provided in Figure 2.13. The two comparators and the phase detector generate pulses at the "UP" output to increase the next switching cycle dead-time, or pulses at the "DN" output to reduce the dead-time. This control loop only optimizes the dead-time when the synchronous MOSFET  $Q_2$  is turned on. A symmetric dead-time control loop is required for the buck converter when  $Q_1$  is turned on and  $Q_2$  is turned off, because the control loop in Figure 2.13 only optimizes the dead-time interval before  $Q_2$  turns on.

Figure 2.13 A dead-time control loop which does not require a digital processor

This dead-time control circuit overcomes those shortcomings brought in by digital processors, since the dead-time is adjusted continuously rather than step by step. Moreover, the two-step size window dithering in steady state in digital controllers is also eliminated.

## 2.5 Summary

Body diode conduction detection and dead-time optimization circuits have been reviewed. The work is summarized as follows. Body diode detection methods differ in three ways. Some algorithms use parameters already monitored by the buck converter output voltage controller, such as input current or output voltage [2], [3]. Others use discrete components, like a NOR gate or a comparator, to detect body diode conduction directly [1], [4]. Finally a built-in detecting MOSFET, which is implemented on the same die of the synchronous MOSFET  $Q_2$ , is recently proposed to detect dead-time [5].

Unit bit dead-time optimization algorithms have been presented in [1]-[3], and [5]. These

methods work quite similarly despite the different dead-time detection algorithms used. However, if the dead-time for the last switching cycle is too long, it is reduced by one unit bit for the following cycle. A preset maximum dead-time value is stored in the controller and the iterative process stops when the optimum value is found. The number of switching cycles needed to reach steady state, and the accuracy of the optimum dead-time, depend on the size of the unit bit.

In contrast with unit bit dead-time adjustment, the one step adjustment algorithm attempts to reach steady state in one switching cycle [4]. The duration of body diode conduction of the last switching cycle is measured first and then the dead-time for the next switching cycle is set as that of last switching cycle minus body diode conduction time. This algorithm results in a short transient time.

In the chapters that follow, a novel analog body diode detection circuit is proposed in Chapter 3, followed by a novel analog dead-time optimization circuit in Chapter 4. The proposed circuits are combined and PSIM simulation results are used to verify and benchmark the contributions in Chapter 5. The conclusions are presented in Chapter 6.

# **Chapter 3**

## **Proposed Body Diode Detection Circuit**

#### 3.1 Overview

A sensitive detection circuit is critical for dead-time control circuits. In Chapter 2, it was noted that a comparator, or a NOR gate, is a relatively simple way to detect body diode conduction among all the other discussed methods. However, a built-in detector can achieve better performance than discrete devices, because for today's devices that operate at high frequencies, a properly integrated detector can minimize parasitic elements. Therefore, in this chapter, an integrated dead-time detection diode is proposed and the detection circuit operation discussed.

This chapter is organized in the following manner. The dead-time detection circuit is introduced in Section 3.2, followed by a description of an adjustment circuit. The adjustment circuit used to convert the detected non-regular waveform to a pulse waveform is introduced in Section 3.3. In Section 3.4, the detection diode implementation is explained. A design procedure with circuit parameters used is then presented in Section 3.5. Finally, a design example and simulation results are presented in Section 3.6.

### 3.2 Dead-time Detection Circuit

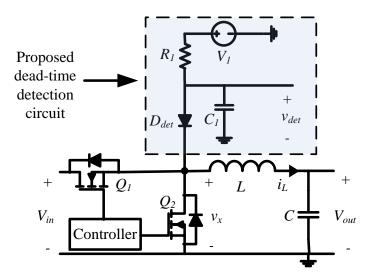

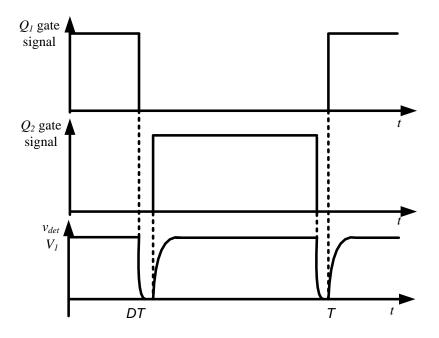

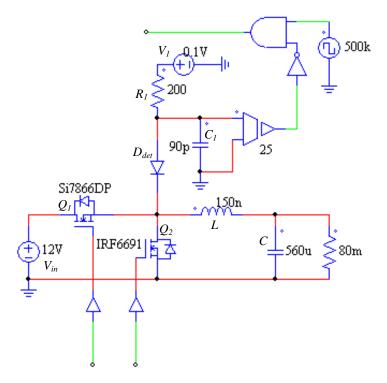

The proposed dead-time detection circuit for the synchronous buck converter is provided in Figure 3.1. A detection diode,  $D_{det}$ , and an auxiliary circuit, consisting of a resistor,  $R_1$ , comparator,  $C_1$ , and a low DC voltage source,  $V_1$  (e.g. 0.1V), are used to detect the conduction of the  $Q_2$  body diode.

Figure 3.1 Proposed dead-time detection circuit for the synchronous buck converter

In order to illustrate the circuit operation, the output voltage of the capacitor  $C_1$  is analyzed under three different operating conditions of the buck converter:

1) The power MOSFET  $Q_1$  is on while the synchronous MOSFET  $Q_2$  is off.

Switch node voltage  $v_x$  in Figure 3.1 is equal to the input voltage  $V_{in}$ , which is 12V in the design example of this thesis.  $V_i$  is a small value voltage source, having a value under 0.2V. As a result, a reverse voltage is formed over the diode  $D_{det}$  and  $D_{det}$  is therefore biased off. The output voltage signal  $v_{det}$  is the voltage across capacitor  $C_i$  and is equal to  $V_i$  during this time.

2) The power MOSFET  $Q_1$  is off while the synchronous MOSFET  $Q_2$  is on.

The inductor current flows through MOSFET  $Q_2$  during this time, so voltage  $v_x$  is negative and the absolute value of  $v_x$  is the product of the current through  $Q_2$  and the on-state resistance of  $Q_2$ . Usually, the on-state resistance of a power MOSFET is quite small, ranging from several milliohms to several hundred milliohms depending on the type of the MOSFET. As a result,  $v_x$  is usually greater than -0.5V during this time. For the components and circuit operating conditions in this thesis,  $v_x$  is approximately -0.1V when  $Q_2$  is on. Thus, diode  $D_{det}$  is biased off and the  $v_{det}$  is equal to  $V_1$ .

## 3) The power MOSFET $Q_1$ is off and the synchronous MOSFET $Q_2$ is also off.

A prerequisite to use this dead-time detector is that the buck converter is operating in continuous mode (i.e.  $i_L > 0$ ). Since neither switch is on, the body diode of MOSFET  $Q_2$  is forced on to provide a path for the inductor current. As a result  $v_x$  drops to a negative value, which is the voltage drop over the p-n junction of  $Q_2$ , and is approximately equal to -0.7V for silicon MOSFETs. Since the voltage source,  $V_1$ , is positive, a voltage drop, which exceeds 0.7V, is applied to  $D_{det}$ , and thus, it is biased on. Therefore, capacitor  $C_1$  is discharged and the output voltage,  $v_{det}$ , drops.

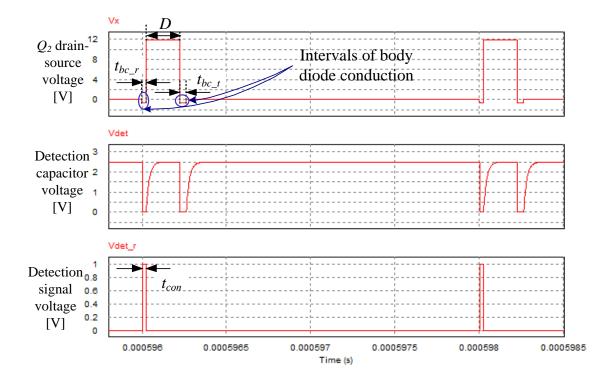

A summary of the states of  $D_{det}$  during the three operation states of the buck converter is provided in Table 3.1. Figure 3.2 provides the waveforms of the voltage signal  $v_{det}$ , along with the gate signals for MOSFETs  $Q_1$  and  $Q_2$ . The time interval of signal  $v_{det}$  being low represents the period when the body diode of the synchronous MOSFET  $Q_2$  is conducting. In other words, it is this period of time that is desired to be eliminated in order to increase the efficiency. Although  $v_{det}$ contains the information of the unwanted dead-time, its waveform is not ideal as a detection signal for the controller. A pulse signal would be preferred, and for this reason, a second circuit is added to adjust the direct detection signal. This adjustment circuit is described in the following subsection.

|                      | v <sub>x</sub>                      | Detection diode, $D_{det}$ |

|----------------------|-------------------------------------|----------------------------|

| $Q_1$ on, $Q_2$ off  | V <sub>in</sub> (12V)               | Off                        |

| $Q_1$ off, $Q_2$ on  | $-i_L R_{on} ~(\geq -0.1 \text{V})$ | Off                        |

| $Q_1$ off, $Q_2$ off | -0.7V                               | On                         |

Table 3.1 Operation condition summary for  $v_x$  and  $D_{det}$  state

Figure 3.2 The detection signal from the proposed dead-time detection circuit

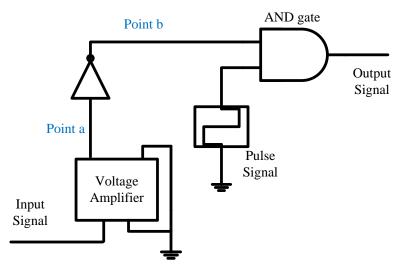

## 3.3 Detection Signal Adjustment Circuit

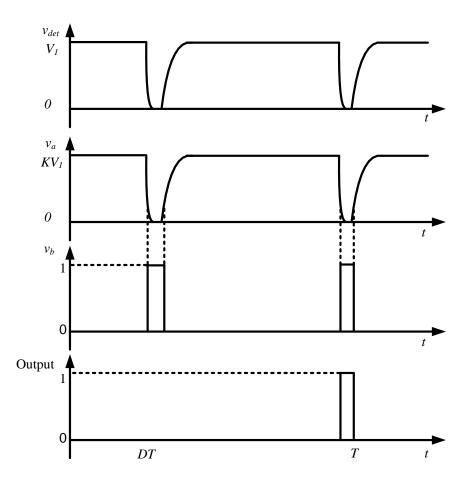

The proposed signal adjustment circuit is provided in Figure 3.3. The purpose of this adjustment circuit is to convert the dead-time detection signal,  $v_{det}$ , into a pulse waveform so that it will be easier for the controller input. Figure 3.4 shows voltage variation at several points of the circuit, including those at points a, b, and c as well as the input and output ports.

Figure 3.3 The adjustment circuit used to modify the detection signal

Figure 3.4 Voltage variations at point a, b, and c as well as input and output ports in the detection signal adjustment circuit

The adjustment circuit first magnifies the input signal  $v_{det}$  by K times through a voltage amplifier, generating signal  $v_a$ . K is an adjustable parameter of the voltage amplifier and is chosen to be a positive integer for this design. Then a logic inverter changes  $v_a$  to be pulse signal  $v_b$ .

Both the power MOSFET  $Q_1$  and the synchronous MOSFET  $Q_2$  are switched on and off once in every switching cycle. Therefore, each has two on-off transitions during one switching cycle, one while switching on and the other while switching off. Thus, there are two dead-time pulses in a switching cycle, as given by  $v_b$  in Figure 3.4. However, these two pulses are usually not of the same width because  $Q_1$  and  $Q_2$  typically have different characteristics and therefore 25 have different switching characteristics. Moreover, the inductor current also varies at the two switching edges. In steady state the inductor current reaches its maximum value when the MOSFET  $Q_I$  turns off and minimum value when  $Q_I$  turns on. Therefore, the two dead-time intervals should be optimized independently. Accordingly, a 50%-duty-cycle selecting pulse at the switching frequency is applied to one input of the AND gate in Figure 3.3, while  $v_b$  is applied to the other. Thus, if the selecting pulse does not have any phase delay, the dead-time signal at the switching on edge is output to the optimization circuit; otherwise, if the selecting pulse has a phase delay of 180 degrees, the dead-time signal at the switching off edge is output. For the design example in this chapter, the latter signal is chosen, as shown in Figure 3.4.

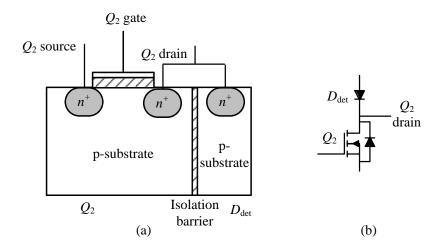

### 3.4 Implementation of the Detection Diode

The trend in modern power integrated circuit manufacturing is to build two, or more devices on the same die in order to reduce parasitic elements. In this section, the detection diode is proposed to be manufactured on the same die as the synchronous MOSFET  $Q_2$ .

The structure of the MOSFET has been reviewed in Chapter 2. The proposed implementation for the detection diode  $D_{det}$  is illustrated in Figure 3.5(a). The detection diode can be located immediately to the right of the MOSFET  $Q_2$  with an isolation barrier in the *p*-substrate. The cathode of  $D_{det}$  is connected to the drain of  $Q_2$ , which is consistent with the circuit arrangement shown in Figure 3.5(b).

Figure 3.5 (a) The detection diode,  $D_{det}$ , is proposed to be manufactured beside the synchronous MOSFET,  $Q_2$ , on the same die and (b) the circuit symbol for this device

There are three advantages of the proposed implementation. First, it is denser than two discrete semiconductors,  $D_{det}$  and  $Q_2$ , so, the dead-time controller can be made smaller. Second, this implementation gives a shorter connection between the  $Q_2$  drain and the  $D_{det}$  cathode than that of two discrete devices. This results in less parasitic inductance and capacitance, which enables the controller to be utilized in higher frequency applications. Third, since  $D_{det}$  and  $Q_2$  are using the same semiconductor material, the body diode of  $Q_2$  and the detection diode  $D_{det}$  have the same forward voltage drop, enabling the detection circuit to be more sensitive and accurate.

#### 3.5 Detection Circuit Design Procedure

Relationships between the circuit parameters of the buck converter are discussed in this section and equations are given in order to illustrate how one parameter influences another. Understanding these relationships enables a designer to choose the right devices for the circuit design and to optimize the expected results. Usually, parameters are chosen sequentially, starting from the initial given ones. Here, the application of the buck converter and design objectives are given. The design procedure for a buck converter is first introduced, followed by the design of the 27

proposed dead-time detection circuit.

### 3.5.1 Buck Converter Design

Given the input voltage,  $V_{in}$ , output voltage,  $V_{out}$ , switching frequency,  $f_s$ , load current,  $I_{load}$ , and peak-to-peak output voltage ripple assuming 100% efficiency, the duty cycle, D, of the power MOSFET is given by (3.1), and the switching period T, is given by the inverse of frequency  $f_s$ , as in (3.2).

$$D = \frac{V_{out}}{V_{in}} \tag{3.1}$$

$$T = \frac{1}{f_s} \tag{3.2}$$

In a design, the specifications for the two MOSFETs in the buck converter need to be decided using the above parameters. The switching speed for both MOSFETs should be sufficient such that the turn-on and turn-off transient times are much smaller than *T*. In addition, the drain-source voltage rating of both power MOSFETs must be larger than  $V_{in}$ , and the drain current rating must be larger than  $I_{load}$ . The larger the ratings chosen, the more robust the design will be. However, high ratings require MOSFETs that are large and therefore more expensive. Typically, the  $V_{ds}$  voltage rating is chosen to be about twice as large as  $V_{in}$ , leaving some safety margin in the design. Another factor that needs to be considered is the overall efficiency of the buck converter. For the power MOSFET  $Q_1$ , the switching loss can be larger than the conduction loss, thus MOSFETs with faster switching speeds, and therefore smaller die size, are preferred. However, the synchronous rectifier MOSFET  $Q_2$  does not have switching loss, but it does handle high currents, so minimizing conduction loss is most important and thus a large die size is preferred.

After selecting the MOSFET switches, the inductor value must be determined. The critical inductance value for continuous current mode is given by (3.3), where  $R_l$  in the equation 28

represents the resistance of a resistive equivalent load, given by (3.4). In order to produce a smooth output current, the buck inductor is usually chosen to be twice as large as  $L_{cri}$ , or even larger if the volume and the cost of the inductor are tolerable.

$$L_{cri} = \frac{1-D}{2} T_s R_l \tag{3.3}$$

$$R_l = \frac{V_{out}}{I_{load}} \tag{3.4}$$

The last component to be chosen for the power stage circuit is the capacitor. The minimal capacitance value,  $C_{min}$ , is given by (3.5), where L is the chosen inductance value and  $K_{rip}$ % is the allowed maximum output voltage ripple. A capacitance of 1.5 to 2 times  $C_{min}$  is typically selected.

$$C_{min} = \frac{1 - D}{8L f_s^2 (K_{rip}\%)}$$

(3.5)

#### 3.5.2 Dead-time Detection Circuit Design

The detection diode  $D_{det}$  is proposed to be fabricated together with the synchronous MOSFET  $Q_2$ , so instead of finding an appropriate pre-made diode product, the manufacturing requirements need to be defined. The forward voltage drop of the detection diode,  $V_{F\cdot det}$ , is a critical parameter since its value should be greater than  $V_1+i_LR_{on}$  to prevent undesired forward biasing of  $D_{det}$  during the synchronous MOSFET on time. However,  $V_{F\cdot det}$  should be less than  $V_1+V_{F\cdot body}$ , where  $V_{F\cdot body}$  is the forward voltage of the synchronous MOSFET's body diode. Otherwise the detection diode will not turn on as desired when the synchronous MOSFET body diode is on. Therefore, the forward voltage of the detection diode,  $V_{F\cdot det}$ , should meet the conditions described in (3.6).

$$V_1 + i_L R_{on} < V_{F-det} < V_1 + V_{F-body}$$

(3.6)

Voltage source,  $V_I$ , is used to provide a reference voltage for the detection signal. Since (3.6) should be met and the forward voltage of a silicon diode is typically 0.7V,  $V_I$  should be less than 0.7V. Therefore, a typical value for  $V_I$  is 0.1V.

To choose  $R_1$  and  $C_1$ , we need to analyze the variables in the circuit during the time when capacitor  $C_1$  is being charged and discharged. Both the rising and falling transition times are much less than the dead-time, therefore the inductor current,  $i_L$ , can be assumed to be constant, as given by (3.7), where  $i_{Ddet}$  is the current through the detection diode  $D_{det}$ , and  $i_{Dbody}$  is that of the  $Q_2$  body diode. Expressions for the circuit current and voltage during the transition can be derived from (3.8) and (3.9), where  $v_{Ddet}(i_{Ddet})$  is the detection diode forward voltage given from the diode characteristic curve when detection diode current is at  $i_{Ddet}$ , and  $v_{Dbody}(i_{Dbody})$  is the body diode forward voltage at  $i_{Dbody}$ .  $v_{Cl}$  is the voltage across capacitor  $C_1$ , which is also the output signal of the detection circuit. Therefore,  $v_{det} = v_{Cl}$ .

$$i_{Ddet} + i_{Dbody} = i_L = constant \tag{3.7}$$

$$\left(i_{Ddet} - C_1 \frac{dv_{C1}}{dt}\right) R_1 = V_1 - v_{C1}$$

(3.8)

$$v_{Ddet}(i_{Ddet}) + v_{C1} = v_{Dbody}(i_{Dbody})$$

(3.9)

It is not necessary to solve (3.8) and (3.9), since we are most interested in the impact of  $R_1$  and  $C_1$  on the detection voltage,  $v_{det}$ , as it drops. It is noted that the smaller  $C_1$  and  $R_1$  are, the faster the transition is.

During the rising transition of the detection voltage,  $v_{det}$ , the diode  $D_{det}$  turns off. Voltage source  $V_i$ , resistor  $R_i$ , and capacitor  $C_i$ , form a typical first-order RC circuit. The circuit variables are given by (3.10) and (3.11), where  $i_{CI}$  is the current flowing through  $C_i$ .

$$i_{C1} = C_1 \frac{dv_{C1}}{dt}$$

(3.10)

$$i_{C1}R_1 + v_{C1} = V_1 \tag{3.11}$$

Substituting (3.10) into (3.11), results in a first-order ordinary differential equation, as given by (3.12). The solution to (3.12) is given by (3.13), where the time constant  $\tau_I$  is expressed in (3.14). Variable  $v_{CI}(t)$  is the voltage across capacitor  $C_I$  at time t. So,  $v_{CI}(\infty)$  is the capacitor voltage value at infinite time, in other words, the steady state value, and  $v_{CI}(\theta_+)$  is that at time zero, or the initial state value.

$$R_1 C_1 \frac{d\nu_{C1}}{dt} + \nu_{C1} = V_1 \tag{3.12}$$

$$v_{C1}(t) = v_{C1}(\infty) + [v_{C1}(0_{+}) - v_{C1}(\infty)]e^{-t/\tau_{1}}$$

(3.13)

$$\tau_1 = R_1 C_1 \tag{3.14}$$

The time constant is defined as the time needed for variable  $v_{CI}(t)$  to reach 63% of the steady state value,  $v_{CI}(\infty)$ . It is often used to represent, or to estimate the transient speed. Therefore, the smaller  $C_I$  and  $R_I$  are, the smaller  $\tau_I$  is, and the faster the rising transition will be. Conversely, when the detection diode is on, the voltage across  $R_I$  is approximately  $V_I$ , so  $R_I$  must be large enough so as not to dissipate too much power.

For the detection signal adjustment circuit, the magnification parameter, K, of the voltage amplifier needs to be decided. K is given by (3.15), where  $V_{logic}$  is the threshold voltage of logic high.

$$K > \frac{V_{logic}}{V_1} \tag{3.15}$$

Parameters K and  $V_i$  are relatively less critical, compared to other parameters discussed above, such as the time constant  $\tau_i$ , the power stage inductor L, and capacitor C. K can be any 31 value that meets (3.15), and theoretically,  $V_1$  can be any value that turns on the detection diode only during the body diode conduction time.

## 3.6 Design Example and Simulation Results

### **3.6.1 Design Example**

The proposed dead-time controller is designed for computer regulators, which convert a 12V input voltage to a 1.2V output at a switching frequency of 500kHz and a load current of up to 25A. These parameters and a typical output voltage ripple specification of 1% are summarized in Table 3.2. The parameters provided are used in the design of the buck converter and its dead-time control circuit.

| Parameter                                              | Value  |

|--------------------------------------------------------|--------|

| Switching Frequency, $f_s$                             | 500kHz |

| Input Voltage, V <sub>in</sub>                         | 12V    |

| Output Voltage, V <sub>out</sub>                       | 1.2V   |