# Techniques for Clock Skew Reduction over Intra-Die Process, Voltage, and Temperature Variations

by

## JEFF MUELLER

M.B.A., University of Texas at Austin, 2001 M.S.E.E., University of Illinois at Urbana, 1995 B.S.E.E., University of Missouri at Rolla, 1991

## A THESIS SUBMITTED IN PARTIAL FULFILMENT OF THE REQUIREMENTS OF THE DEGREE OF

## DOCTOR OF PHILOSOPHY

in

The Faculty of Graduate Studies

(Electrical and Computer Engineering)

THE UNIVERSITY OF BRITISH COLUMBIA (Vancouver)

September 2010

© Jeff Mueller, 2010

### Abstract

Synchronous clock distribution continues to be the dominant timing methodology for very large scale integration circuit designs. As processes shrink, clock speeds increase, and die sizes grow, an increasingly larger percentage of the clock period is being lost to skew and jitter. New techniques to reduce clock skew and jitter must be deployed to utilize the faster clock frequencies possible with future process technologies, especially in the presence of on-chip process-voltage-temperature (PVT) variations.

This dissertation first proposes a *pre-silicon* design modification to symmetric clock buffers of traditional clock distribution networks. Specifically, clock performance is improved by targeting the critical clock edge (the edge activating rising edge-triggered flip-flops) while relaxing the requirements of the non-critical edge. This system uses alternating, asymmetric clock buffers to focus inverter resources on only one edge of the clock pulse; hence, it is called *Single Edge Clocking (SEC)*. A novel re-design of the traditional clock buffer is proposed as a drop-in replacement for existing clock distribution networks, yielding timing performance improvements of over 20% in latency and skew, and up to 30% in jitter; alternatively, these timing advantages could be traded off to reduce clock buffer area and power by 33% and 12%, respectively.

PVT variations, especially intra-die, increasingly upset the distribution of a synchronized clock signal, even in properly balanced clock tree networks. Hence, active clock deskewing becomes necessary to tune out unwanted clock skew after chip fabrication. This dissertation proposes a *post-silicon* autonomous deskewing system using tunable buffers to dynamically reduce clock skew. The operation of a specially designed phase detector is described, and four such phase detectors are used to construct a stable, autonomously locking *Quad Ring Tuning (QRT)* configuration that effectively links together four distributed Delay-Locked Loops (DLLs) without the need for any system-level controller. This cyclic, unidirectional, self-controlled, quad-DLL ring tuning technique is then implemented hierarchically to dynamically adjust clock signal delays across an entire chip during normal circuit operation. A simple form of the two-level QRT system is presented for a generic H-tree distribution network, demonstrating stable locking behavior and more than 50% average reduction in full-chip clock skew.

## Preface

The research presented in this dissertation has been previously published in two Institute of Electrical and Electronics Engineers (IEEE) Conference papers and will soon be published in an IEEE Journal paper, as detailed below.

The research covered in Chapter 3 has been published in: J. Mueller and R. Saleh, "Single Edge Clock (SEC) distribution for improved latency, skew, and jitter performance," *Proceedings of Very Large Scale Integration Design (VLSID) Conference*, pp. 214-9, Jan. 2008.

Most of the research covered in Chapter 4 has been published in: J. Mueller and R. Saleh, "A tunable clock buffer for intra-die PVT compensation in Single-Edge Clock (SEC) distribution networks," *Proceedings of International Symposium on Quality Electronic Design (ISQED)*, pp. 572-7, Mar. 2008.

The research covered in Chapter 5 will be published in: J. Mueller and R. Saleh, "Autonomous, multi-level ring tuning scheme for post-silicon active clock deskewing over intra-die variations," to be published in *IEEE Transactions on Very Large Scale Integration (TVLSI) Systems, 14 pages, 2010.*

These three papers and this dissertation present research conducted by "the author", Jeff Mueller, in collaboration with "the supervisor", Dr. Resve Saleh, who provided consultation on research and editing assistance on publications.

## **Table of Contents**

| ABSTRACT                                                                                                                       | ii     |

|--------------------------------------------------------------------------------------------------------------------------------|--------|

| PREFACE                                                                                                                        | iii    |

| TABLE OF CONTENTS                                                                                                              | iv     |

| LIST OF TABLES                                                                                                                 | viii   |

| LIST OF FIGURES                                                                                                                |        |

|                                                                                                                                |        |

| LIST OF SYMBOLS                                                                                                                | xi     |

| ACKNOWLEDGEMENTS                                                                                                               | xii    |

| CHAPTER 1 : INTRODUCTION AND OVERVIEW                                                                                          |        |

| 1.1 MOTIVATION                                                                                                                 |        |

| 1.2 Synchronous Clock Design Issues                                                                                            | 2      |

| 1.3 PVT VARIATIONS                                                                                                             | 5      |

| 1.4 SKEW AND JITTER REDUCTION AND COMPENSATION                                                                                 | 7      |

| 1.5 Research Statement                                                                                                         |        |

| 1.6 THESIS ORGANIZATION                                                                                                        |        |

| CHAPTER 2 : SYNCHRONOUS CLOCK BACKGROUND                                                                                       | 11     |

| 2.1 CLOCK FUNCTION AND DESIGN ISSUES                                                                                           |        |

| 2.1.1 Clock Source                                                                                                             |        |

| 2.1.2 Flip-Flop Timing Issues                                                                                                  |        |

| 2.1.3 Clock Distribution Network Design                                                                                        |        |

| 2.1.3.1 Basics of Clock Networks                                                                                               |        |

|                                                                                                                                |        |

| 2.1.3.2 Basics of Clock Buffer Design                                                                                          | 19     |

| 2.1.3.2       Basics of Clock Buffer Design         2.1.3.3       Other Clock Design Issues                                    |        |

| -                                                                                                                              |        |

| 2.1.3.3 Other Clock Design Issues                                                                                              |        |

| 2.1.3.3 Other Clock Design Issues                                                                                              |        |

| <ul> <li>2.1.3.3 Other Clock Design Issues</li> <li>2.1.4 Clock Timing Metrics</li> <li>2.2 PVT VARIATIONS AND SKEW</li> </ul> |        |

| <ul> <li>2.1.3.3 Other Clock Design Issues</li></ul>                                                                           | 22<br> |

| <ul> <li>2.1.3.3 Other Clock Design Issues</li></ul>                                                                           | 22<br> |

| <ul> <li>2.1.3.3 Other Clock Design Issues</li></ul>                                                                           |        |

|    | 2.3    | .2.2 Cyclic Architecture                              | 33 |

|----|--------|-------------------------------------------------------|----|

|    | 2.3    | .2.3 Acyclic Architecture                             | 35 |

| 2  | 2.4 BA | ACKGROUND SUMMARY                                     | 37 |

| СН | APTER  | 3 : SINGLE-EDGE CLOCKING (SEC)                        |    |

|    | 3.1 IM | IPROVED CLOCK PERIOD UTILIZATION WITH SEC             |    |

|    | 3.1.1  | Performance Trade-off between Clock Edges             |    |

|    | 3.1.2  | Practical Application of SEC                          |    |

| 2  | 3.2 SE | EC BUFFER DESIGN CONSTRAINTS                          |    |

|    | 3.2.1  | SEC Capacitance Constraint with Drop-in Compatibility |    |

|    | 3.2.2  | SEC Asymmetrical Inverter Pairs                       |    |

|    | 3.2.3  | SEC Inverters' Beta Modeling                          |    |

|    | 3.2.4  | Layout Area Considerations                            |    |

|    | 3.3 Ai | valysis of Asymmetric SEC Buffers                     |    |

|    | 3.3.1  | Voltage Transfer Characteristics                      |    |

|    | 3.3.2  | Noise Margins                                         |    |

| 2  | 3.4 Fi | JLL-CHIP SEC DISTRIBUTION DESIGN                      |    |

|    | 3.4.1  | H-tree Buffer Sizing                                  |    |

|    | 3.4.2  | Simulation Model Single Branch Model                  |    |

|    |        | JLL-CHIP SEC PERFORMANCE RESULTS                      |    |

|    | 3.5.1  | Latency Improvements                                  |    |

|    | 3.5.2  |                                                       |    |

|    | 3.5.3  |                                                       |    |

|    | 3.5.4  |                                                       |    |

| -  |        | JLL-CHIP SEC CONCLUSIONS                              |    |

|    | 5.0 PC | JLE-CHIP JEC CONCLUSIONS                              |    |

| СН | APTER  | 4 : TUNABLE SEC BUFFER DESIGN AND APPLICATIONS        | 69 |

| 4  | 4.1 Tu | JNABLE SEC BUFFERS                                    |    |

|    | 4.1.1  | Tunable Buffer Design                                 |    |

|    | 4.1    | .1.1 Capacitive Load                                  | 70 |

|    | 4.1    | .1.2 Starved Inverter                                 | 71 |

|    | 4.1.2  | Tunable SEC Simulation Results                        | 74 |

|    | 4.1    | .2.1 Single Branch Model (SBM)                        | 74 |

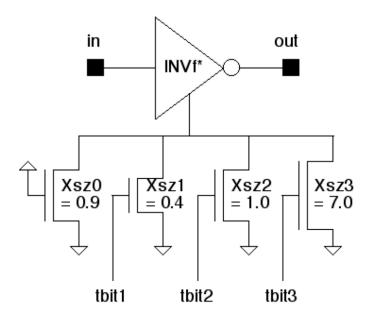

|    | 4.1    | .2.2 Tuning Range Waveforms                           | 75 |

|    | 4.1    | .2.3 Area and Power Comparisons                       | 77 |

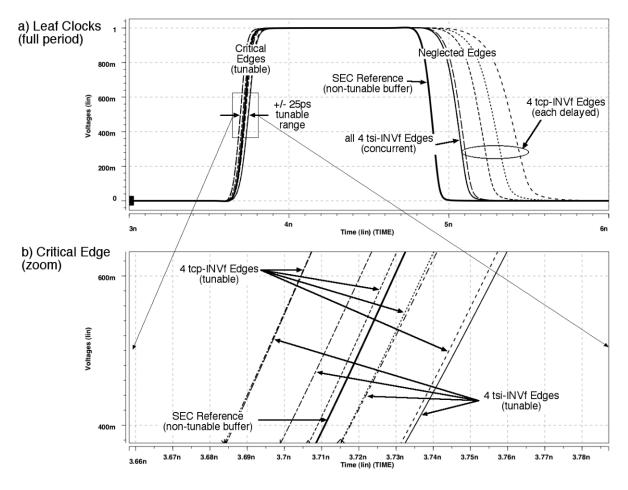

|    | 4.1.3  | PVT Variation Results                                 |    |

| 4.1.4   | Tunable SEC Buffer Limitations and Conclusions      |     |

|---------|-----------------------------------------------------|-----|

| 4.2 In  | NDIVIDUAL SEC BUFFERS FOR CLOCK EDGE ADJUSTMENTS    |     |

| 4.2.1   | Single SEC Buffer Substitution                      |     |

| 4.2.2   | Centering Tunable Buffers with SEC                  |     |

| 4.2.3   | Individual SEC Buffer Limitations and Conclusions   |     |

| 4.3 S   | EC APPLICATION LIMITATIONS AND SUMMARY              |     |

| CHAPTEI | R 5 : RING TUNING FOR POST-SILICON CLOCK DESKEWING  |     |

| 5.1 0   | VERVIEW OF ACTIVE CLOCK DESKEWING                   |     |

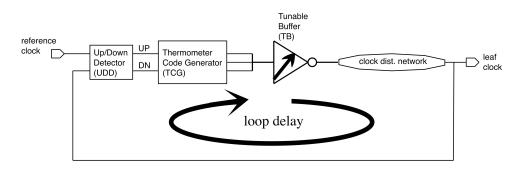

| 5.2 T   | HREE COMPONENTS FOR THE DESKEW LOOPS                | 90  |

| 5.2.1   | Up/Down Detector (UDD)                              |     |

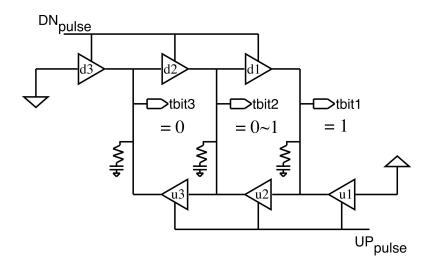

| 5.2.2   | Thermometer Code Generator (TCG)                    |     |

| 5.2.3   |                                                     |     |

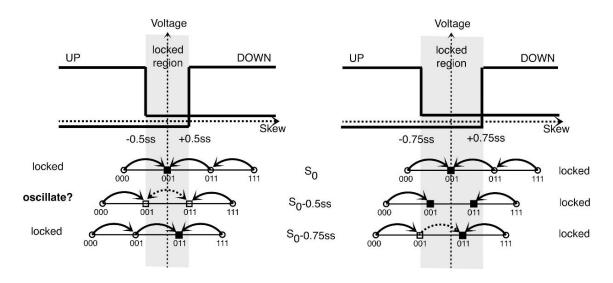

| 5.3 D   | ESKEW LOOP DESIGN FOR STABLE OPERATION              |     |

| 5.3.1   | Deskew Loop Delay Analysis                          | 100 |

| 5.3.2   | Measurement and Adjustment Resolutions              |     |

| 5.4 M   | IULTIPLE DESKEW LOOP CONNECTION FOR RING TUNING     | 105 |

| 5.4.1   | The Case for Ring Tuning over Acyclic Tuning        |     |

| 5.4     | 4.1.1 Avoiding the Global Controller                |     |

| 5.4     | 4.1.2 Avoiding Cyclic Instabilities                 |     |

| 5.4     | 4.1.3 Improving Skew Bound Hierarchically           |     |

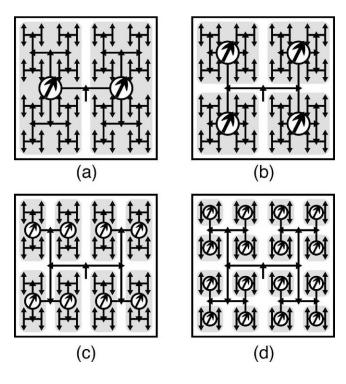

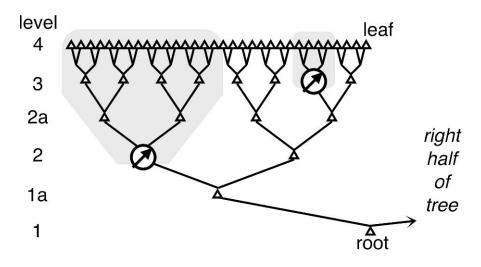

| 5.4.2   | Single-level Ring Tuning for H-tree                 | 112 |

| 5.4     | 4.2.1 Independent Tuning Zone Selection             |     |

| 5.4     | A.2.2         Ring Tuning Connection for Four Zones |     |

| 5.4.3   | Hierarchical Ring Tuning for H-tree                 | 118 |

| 5.5 H   | -TREE RING TUNING SIMULATION RESULTS                | 120 |

| 5.5.1   | Full H-tree Netlist                                 | 121 |

| 5.5.2   | PVT Variation Modeling                              |     |

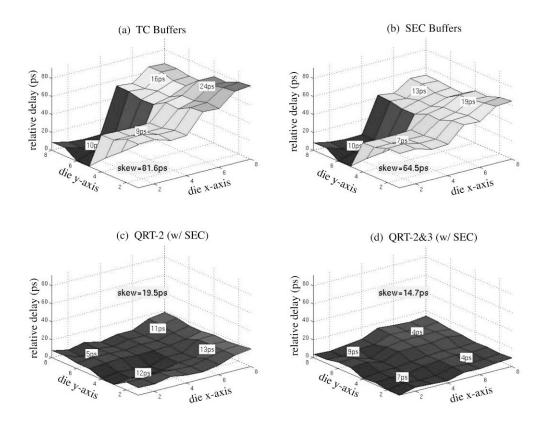

| 5.5.3   | SEC-only Improvements                               | 128 |

| 5.5.4   | SEC + QRT-2 Improvements                            | 129 |

| 5.5.5   | SEC + QRT-2&3 Improvements                          | 134 |

| 5.6 Q   | RT SUMMARY AND LIMITATIONS                          | 139 |

| CHAPTEI | R 6 : SUMMARY, CONCLUSIONS, AND FUTURE WORK         |     |

| 6.1 P   | RE-SILICON SKEW REDUCTION                           | 143 |

| 6.1.1   | Summary of Contributions                            | 143 |

| 6.1.2      | Limitations                 |     |

|------------|-----------------------------|-----|

| 6.1.3      | Proposed Future Work        | 145 |

| 6.2 Pos    | T-SILICON SKEW COMPENSATION | 146 |

| 6.2.1      | Summary of Contributions    | 146 |

| 6.2.2      | Limitations                 | 148 |

| 6.2.3      | Proposed Future Work        | 149 |

| REFERENCES |                             |     |

## List of Tables

| TABLE 1-1 : CLOCK PERIOD LOST TO SKEW FROM FIGURE 1.1 DATA               | 2   |

|--------------------------------------------------------------------------|-----|

| TABLE 3-1 : SEC BUFFER DEGRADATION FACTOR CHOICES                        |     |

| TABLE 3-2 : MULTIPLE-SOURCE NOISE MARGINS                                |     |

| TABLE 4-1 : DELAY VALUES FOR ALL POSSIBLE TBIT SETTINGS                  | 73  |

| TABLE 5-1 : COMPARISON OF ACYCLIC METHOD TO TWO RING TUNING METHODS      |     |

| TABLE 5-2 : PVT VARIATIONS USED IN SIMULATIONS                           | 126 |

| TABLE 5-3 : OVERALL CLOCK SKEW RESULTS FOR SEC VERSUS TC                 |     |

| TABLE 5-4 : TUNABLE BUFFER BITS STATE AND UP/DN SIGNAL OVER LOCKING TIME |     |

| TABLE 5-5 : OVERALL CLOCK SKEW RESULTS FOR QRT                           | 133 |

| TABLE 5-6 : SUB-QUADRANT SKEW RESULTS FOR QRT                            | 138 |

## List of Figures

| FIGURE 1.1 : CLOCK SKEW OVER PROCESS TECHNOLOGY (FROM [2])                            | 1  |

|---------------------------------------------------------------------------------------|----|

| FIGURE 1.2 : BASIC CLOCK DISTRIBUTION NETWORKS: H-TREE, GRID, AND HYBRID (FROM [7])   | 3  |

| FIGURE 1.3 : PROCESS VARIATION OVER ONE DIE FROM A WAFER (FROM [16])                  | 5  |

| FIGURE 1.4 : CONCENTRIC CIRCLES REPRESENTING P, V, AND/OR T VARIATIONS (FROM [2])     | 6  |

| Figure 2.1 : Ideal Synchronous Clock Period (from [5])                                |    |

| FIGURE 2.2 : RISING EDGE-TRIGGERED D FLIP-FLOP (FROM [30])                            |    |

| FIGURE 2.3 : FLIP-FLOP SETUP AND HOLD TIME DEFINITIONS (FROM [30])                    |    |

| FIGURE 2.4 : CLOCK TREE COMPONENTS [ROOT, BRANCHES, AND LEAVES] (FROM [5])            |    |

| FIGURE 2.5 : TYPICAL CMOS INVERTER (FROM [30])                                        |    |

| FIGURE 2.6 : TYPICAL SYNCHRONOUS CLOCK NETWORK [H-TREE AND FFS] (FROM [7])            |    |

| FIGURE 2.7 : CLOCK LATENCY, SKEW, AND JITTER. (#1 = ROOT BUFFER AND #4 = LEAF BUFFER) |    |

| FIGURE 2.8 : PVT VARIATION SKEW MODELING (FROM [36])                                  |    |

| FIGURE 2.9 : BALANCED H-TREE FOR SKEW REDUCTION (FROM [19])                           |    |

| FIGURE 2.10 : BALANCED BUFFERS FOR REDUCED SKEW (FROM [45])                           |    |

| FIGURE 2.11 : A BASIC POST-SILICON SKEW COMPENSATION SYSTEM (FROM [49])               |    |

| FIGURE 2.12 : PREVIOUS MULTIPLE PLL RING ARCHITECTURE (FROM [57])                     |    |

| FIGURE 2.13 : PREVIOUS ACYCLIC MULTIPLE PLL CONNECTIONS (FROM [61])                   |    |

| FIGURE 3.1 : TRADITIONAL AND MODIFIED DEFINITION OF PULSE WIDTH                       |    |

| FIGURE 3.2 : CLOCK PERIOD UTILIZATION                                                 |    |

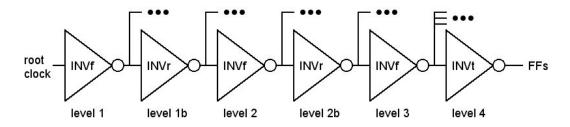

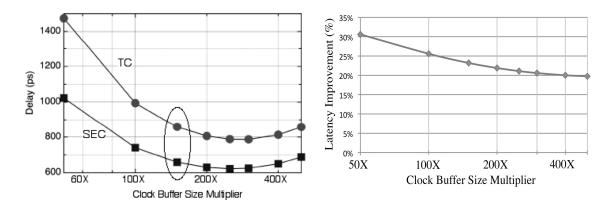

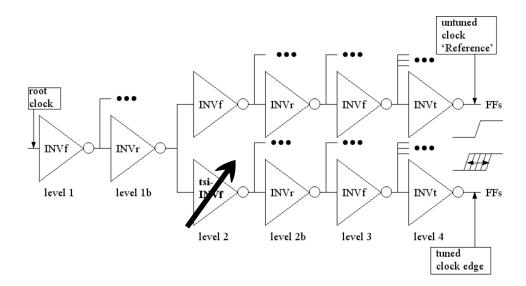

| FIGURE 3.3 : 4-LEVEL H-TREE                                                           |    |

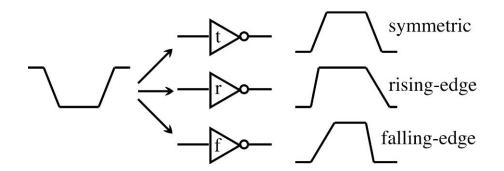

| FIGURE 3.4 : FASTER AND SHARPER EDGES FOR SEC INVERTERS (INVT VERSUS INVR & INVF)     | 50 |

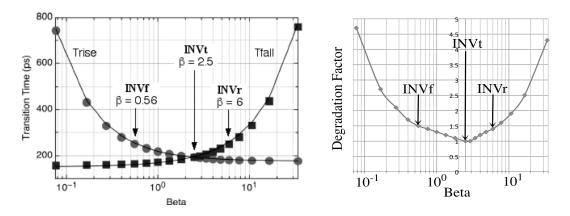

| FIGURE 3.5 : <i>Trise</i> and <i>Tfall</i> (left) and h (right) versus buffer b       |    |

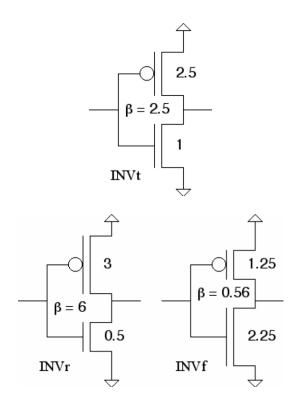

| FIGURE 3.6 : RELATIVE TRANSISTOR SIZING FOR TC & SEC CLOCK BUFFERS                    |    |

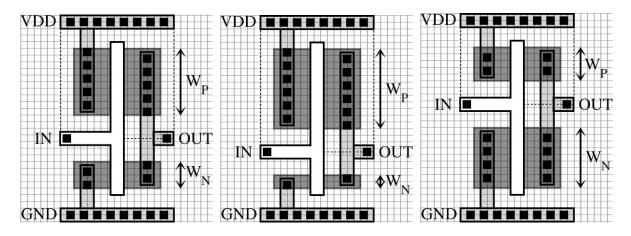

| FIGURE 3.7 : LAYOUT OF THREE INVERTERS (INVT, INVR, INVF)                             |    |

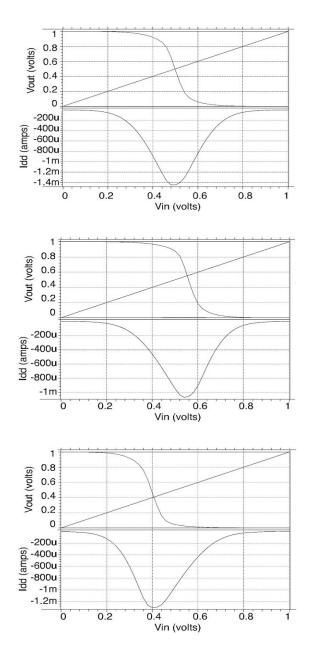

| FIGURE 3.8 : VTC AND CURRENT CURVES (INVT, INVR, INVF)                                |    |

| FIGURE 3.9 : SBM SCHEMATIC                                                            |    |

| FIGURE 3.10 : TIMING WAVEFORMS FOR TC AND TWO CHOICES OF SEC                          |    |

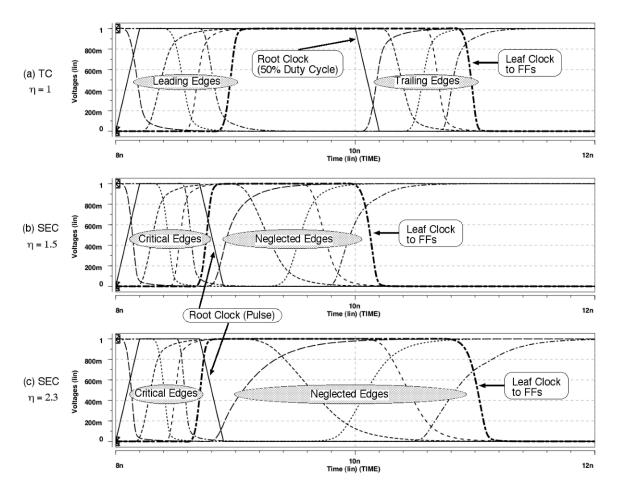

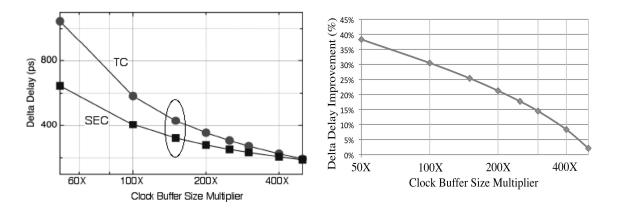

| FIGURE 3.11 : LATENCY VERSUS BUFFER SIZE                                              |    |

| FIGURE 3.12 : WORST-CASE SKEW VERSUS BUFFER SIZE                                      |    |

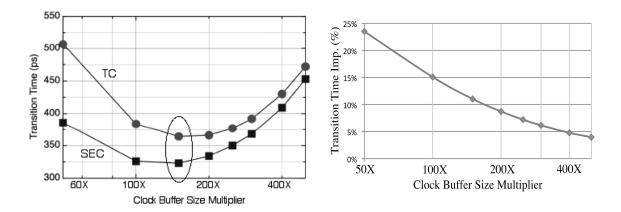

| FIGURE 3.13 : AVERAGE TRANSITION TIME VERSUS BUFFER SIZE                              |    |

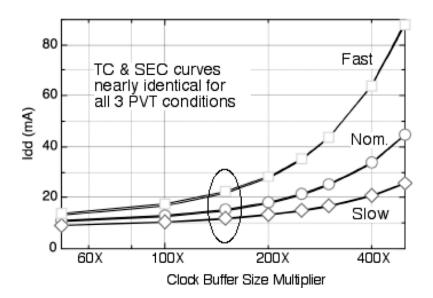

| FIGURE 3.14 : AVERAGE IDD VERSUS BUFFER SIZE                                          |    |

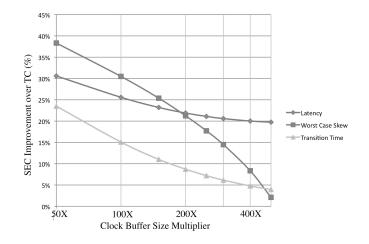

| FIGURE 3.15 : PERCENT IMPROVEMENT OF SEC OVER TC                                      |    |

| FIGURE 4.1 : CAPACITIVE LOAD DELAY BUFFER                                             |    |

| FIGURE 4.2 : SINGLE-SIDED STARVED INVERTER DELAY BUFFER                               |    |

| FIGURE 4.3 : SBM SCHEMATIC WITH TUNABLE BUFFER (TB)                                     | 75  |

|-----------------------------------------------------------------------------------------|-----|

| FIGURE 4.4 : TSI AND TCP WAVEFORMS OVER 4 DELAY SETTINGS                                | 76  |

| FIGURE 4.5 : PROCESS, VOLTAGE, AND TEMPERATURE TUNING RANGES                            |     |

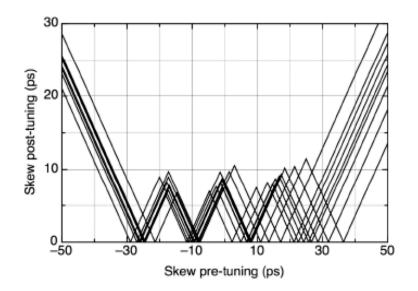

| FIGURE 4.6 : PRE-TUNING SKEW VERSUS POST-TUNING SKEW                                    | 79  |

| FIGURE 4.7 : CENTERING THE SEC TUNABLE BUFFER                                           |     |

| FIGURE 5.1 : DLL DESIGN FOR USE IN RING TUNING                                          |     |

| FIGURE 5.2 : UDD SCHEMATIC                                                              |     |

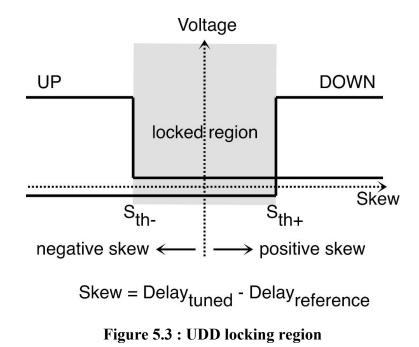

| FIGURE 5.3 : UDD LOCKING REGION                                                         | 94  |

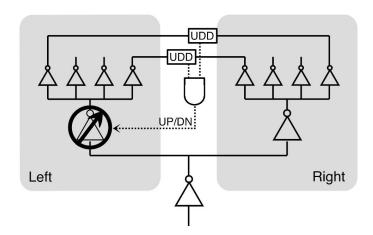

| FIGURE 5.4 : LOGICAL OPERATION ON MULTIPLE UDDS                                         |     |

| FIGURE 5.5 : TCG SIMPLIFIED FUNCTIONAL SCHEMATIC [74]                                   |     |

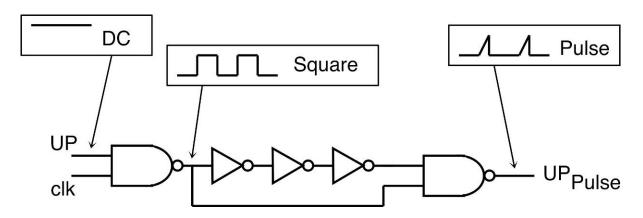

| FIGURE 5.6 : PULSE GENERATOR FOR TCG                                                    |     |

| FIGURE 5.7 : LOOP DELAY CONSIDERATION FOR STABILITY                                     |     |

| FIGURE 5.8 : STABLE LOCKING OVER PVT VARIATIONS                                         | 102 |

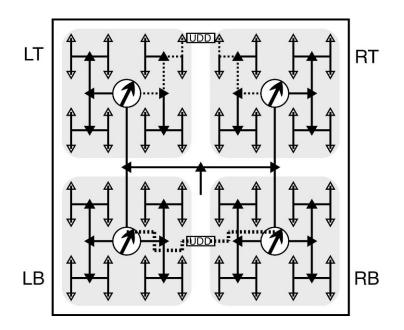

| FIGURE 5.9 : FOUR POSSIBLE TUNING ZONES TBS AT (A) LEVEL-1A, (B) LEVEL-2, (C) 2A, (D) 3 | 114 |

| FIGURE 5.10 : H-TREE HIERARCHY (LEFT HALF ONLY)                                         | 115 |

| FIGURE 5.11 : UDD CONNECTIONS                                                           | 116 |

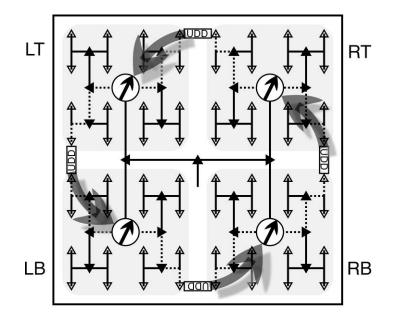

| FIGURE 5.12 : QRT LEVEL-2 OPERATION                                                     | 117 |

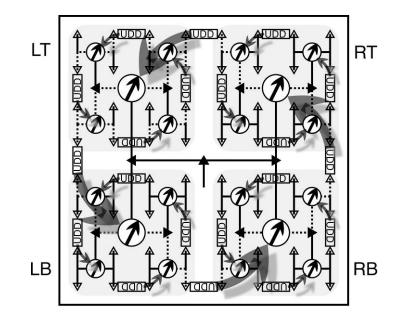

| FIGURE 5.13 : QRT LEVEL-2&3 OPERATION                                                   | 119 |

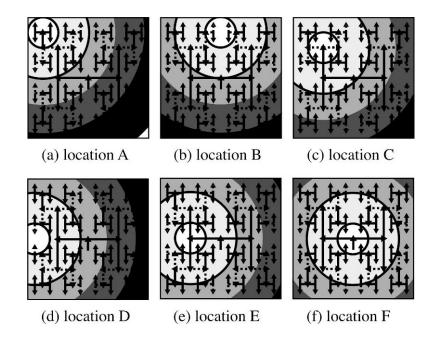

| FIGURE 5.14 : LOCATION OF SPATIAL VARIATIONS                                            | 124 |

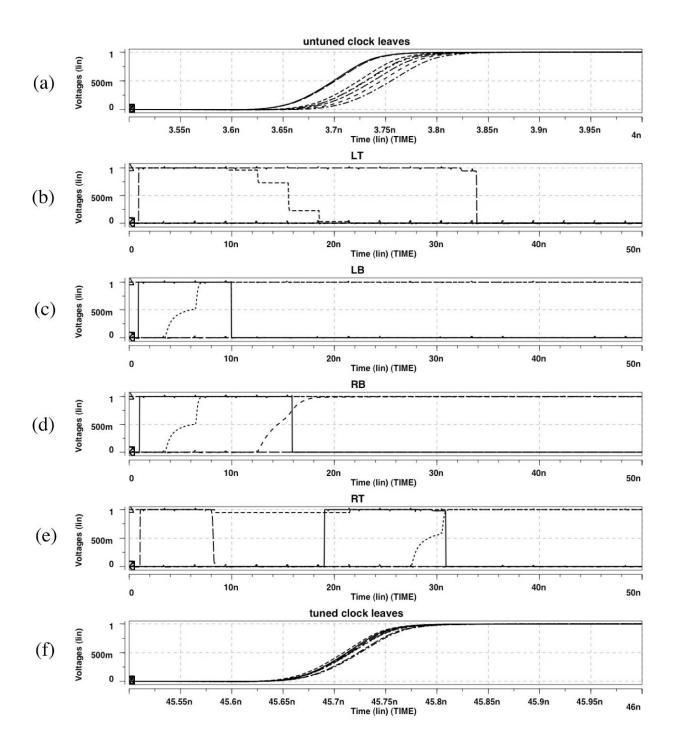

| FIGURE 5.15 : TRANSIENT SIMULATION WAVEFORMS OF QRT-2 OPERATION                         | 131 |

| FIGURE 5.16 : SURFACE PLOTS OF H-TREE LEAF CLOCKS FOR FOUR CLOCK DESIGNS                | 136 |

## List of Symbols

| β                   | beta of an inverter $(=W_P/W_N)$                                   |

|---------------------|--------------------------------------------------------------------|

| η                   | degradation factor of SEC (=t <sub>negl</sub> /t <sub>crit</sub> ) |

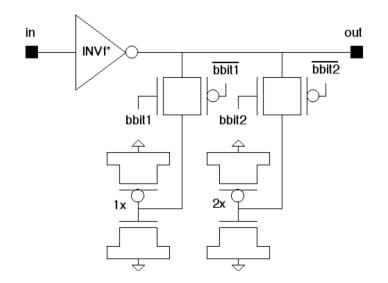

| bbit1, bbit2        | binary tuning bits for a tcp-INVf                                  |

| DLL                 | delay locked loop                                                  |

| FF                  | flip-flop                                                          |

| INVf                | inverter used as falling edge clock buffer in SEC                  |

| INVr                | inverter used as rising edge clock buffer in SEC                   |

| INVt                | inverter used as clock buffer in TC                                |

| ISF                 | impulse sensitivity function (a measure of jitter)                 |

| LT/LB/RB/RT         | four quadrants of QRT                                              |

|                     | (left-top, left-bottom, right-bottom, and right-top)               |

| M.C.                | Monte Carlo simulation                                             |

| PLL                 | phase locked loop                                                  |

| PVT                 | variations created by process, voltage, and temperature            |

| PW                  | pulse width of the clock signal                                    |

| QRT                 | quad ring tuning (i.e. RT with four tuning zones)                  |

| QRT-2               | single level QRT implemented at clock level-2                      |

| QRT-2&3             | hierarchical QRT implemented at clock level-2 and level-3          |

| r.s.a.              | range sharing algorithm                                            |

| RT                  | ring tuning                                                        |

| $\mathbf{S}_{th}$   | skew threshold of UDD                                              |

| SBM                 | single branch model                                                |

| SEC                 | single edge clocking                                               |

| SS                  | step size of TB                                                    |

| s.w.a.              | spinning wheel algorithm                                           |

| tcp-INVf            | tunable INVF buffer delayed by load capacitance                    |

| tsi-INVf            | tunable INVf buffer delayed by a starved inverter                  |

| tbit1, tbit2, tbit3 | thermometer code tuning bits for a tsi-INVf                        |

| t <sub>crit</sub>   | critical edge transition time of the clock signal                  |

| t <sub>negl</sub>   | neglected edge transition time of the clock signal                 |

| T <sub>clk</sub>    | period of the clock signal                                         |

| TB                  | tunable buffer                                                     |

| TC                  | traditional clocking                                               |

| TCG                 | thermometer code generator                                         |

| UDD                 | up/down detector                                                   |

| W <sub>N</sub>      | width of the NMOS device of an inverter                            |

| $W_P$               | width of the PMOS device of an inverter                            |

## Acknowledgements

Thanks to everyone who has helped me along the way!

Special thanks go to: Supervisor: Dr. Resve Saleh Co-supervisor: Dr. Shahriar Mirabbasi Committee Members: Drs. Steve Wilton and John Madden Head's Nominee: Dr. Mark Greensteet Chair: Dr. Andre Ivanov.

Also, thanks to our SoC Lab experts: Dr. Roberto Rosales Roozbeh Mehrabadi.

| Thanks to my fellow SoC students, most notably: | Dr. Dipanjan Sengupta |

|-------------------------------------------------|-----------------------|

|                                                 | Dr. Xiongfei Meng     |

|                                                 | Dr. Peter Hallschmid. |

Thanks to our funding sources:

Natural Sciences and Engineering Research Council of Canada (NSERC) PMC-Sierra, Burnaby, BC Canada (including use of their design tools) Canadian Microelectronics Corporation (CMC).

Finally, and most importantly, thank you to my family -- especially Mom and Dad who have always been there for me. And lastly, Thank You Dana for everything.

## **Chapter 1 : Introduction and Overview**

#### 1.1 Motivation

Synchronous clock delivery has always been a major design challenge in application specific integration circuits (ASICs). Without an adequate clock signal, synchronous circuits will experience setup time and/or hold time violations on flip-flops that may lead to logic errors, and they will consequently fail to operate as expected. Much of the effort in clock design is spent on reducing two key timing issues of *skew* and *jitter* [1]. *Skew* is defined as the difference in clock edge arrival times for two different clock wires (or clock paths). Skew is typically caused by mismatches in the branches of the clock distribution network. *Jitter* is defined as the difference in clock wire (or clock path). Jitter is typically caused by circuit-induced noise effects on the clock signal. Today, significant area, power, and metal resources are required to distribute a synchronous, high-speed clock across a large die with minimal skew and jitter. Yet, the synchronous clock delivery problem is expected to be even more difficult in the future, as seen in Figure 1.1.

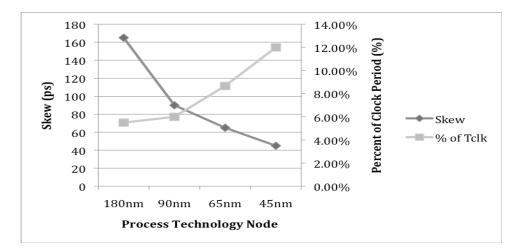

Figure 1.1 : Clock skew over process technology (from [2])

| Technology | Clock Period | Skew  | % Lost to Skew |

|------------|--------------|-------|----------------|

| 180nm      | 3ns          | 165ps | 5.5%           |

| 90nm       | 1.5ns        | 90ps  | 6.0%           |

| 65nm       | 750ps        | 65ps  | 8.7%           |

| 45nm       | 375ps        | 45ps  | 12.0%          |

Table 1-1 : Clock Period Lost to Skew from Figure 1.1 Data

Although the absolute level of clock skew is seen to be decreasing in the graph of Figure 1.1, the amount of clock skew as a percentage of clock period is in fact increasing for each new process technology node. Assuming a reasonable clock frequency of 333MHz for the 180nm node, and doubling the clock frequency for each subsequent node, the percent of clock period lost to skew is calculated for each process technology and displayed on Figure 1.1 and in Table 1-1. The percent of clock period lost to skew is seen doubling from the 90nm to the 45nm node. While these are somewhat conservative predictions, in reality, predictions for overall variability in process nodes beyond 45nm have been shown to further exacerbate the clock skew problem, as well as jitter. In fact, according to projections in [3], as processes scale further down into the nanometer range, larger percentages of the clock design approaches. Therefore, new techniques to improve overall clock timing performance (clock skew and jitter) are needed.

### 1.2 Synchronous Clock Design Issues

The vast majority of present-day ASICs use synchronous clocks [1] driving singleedge triggered flip-flops (FFs). Furthermore, even the larger chip sizes of very large-scale integrated (VLSI) circuit designs, which in the future may adopt a *globally asynchronous* clock, will still rely on *locally synchronous* clocks for logical circuit operation [4]. Therefore, synchronous clock circuit design will be the focus of the research here since today it is a critical component of IC design and will continue to be so in the future.

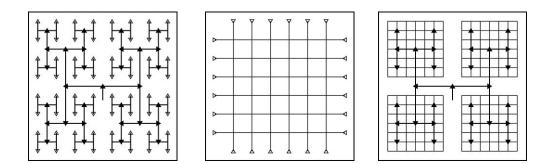

The design and architecture of many commonly used clock distribution systems are thoroughly described in several papers [5][6]. Standard inverters, commonly referred to as clock buffers, are typically used to drive the clock signal from the root (the phase-locked loop or delay-locked loop source) to the leaves (the FFs) of a clock distribution network (e.g., H-tree, grid, hybrid) [7][8][9][10][11]. Three different forms of clock networks are illustrated in Figure 1.2, with the H-Tree in some form being the most common.

Figure 1.2 : Basic Clock Distribution Networks: H-tree, Grid, and Hybrid (from [7])

The primary goal of these different architectures is to reduce maximum clock skew and maximum jitter. For the purposes of this research, skew will be defined here as the difference in clock edge arrival times for two different clock branches,  $\Delta t_{i\cdot j} = t_i - t_j$ . The arrival time for each unique clock branch will be measured at its terminal clock leaf and represented as  $t_i$ . Therefore, the *maximum clock skew* will be given by the absolute value maximum of  $\Delta t_{i\cdot j} = t_i - t_j$  for  $i \neq j$ , where *i* and *j* cover every clock leaf of the entire chip. Likewise, jitter will be defined as the difference in clock edge arrival time for a single clock branch. Therefore, the jitter at any given clock leaf is represented as  $\Delta t_k = t_{k,max} - t_{k,min}$ , and the *maximum jitter* is given by the absolute value maximum of  $\Delta t_k$ , where *k* covers every clock leaf of the entire chip. Illustrated representations of skew and jitter will be provided later in Section 2.1.4.

Skew can be caused by mismatches in the routing of the clock distribution network and also by intra-die process variations of one clock path, or branch, versus another clock branch. Ideally, the routing paths between the clock's root node and two different FFs should be laid out identically; but this option is often not possible and, hence, skew is created. Furthermore, the process variations, supply voltage fluctuations, and temperature gradients across the chip during its operation are increasingly significant factors in skew today [12][13][14]. Thus, both sources of clock skew (layout mismatches and process, voltage, and temperature variations) should be reduced. In addition, clock *latency*, which is the total path delay from the clock root to its leaves, where FFs are connected, is another useful timing metric since a lower latency often implies a lower skew.

Jitter is expected to be a significant source of problems for clock designers according to the projections of [3]. The effects of supply noise, coupling noise, and other noise sources are expected to increase in the future and significantly reduce the usable clock period due to jitter. At the same time the clock period will continue to shrink with each technology generation and further exacerbate the problem. Previous work on jitter, or phase noise as it is often called by analog designers, has lead to the metric of Impulse Sensitivity Function (ISF) [15], which relates jitter performance to clock edge transition slope. When the clock signal is stable (at a high or low level) or when the clock's non-critical edge is transitioning, then noise impulses are not a concern in terms of jitter. However, each transition of the clock's critical timing edge leaves it exposed to these noise impulses and

4

therefore vulnerable to jitter. So, if the critical edge-rate of the clock signal can be sharpened, the jitter performance will likely improve. Other techniques to shield the clock and reduce noise injection levels can greatly improve the jitter as well.

#### **1.3 PVT Variations**

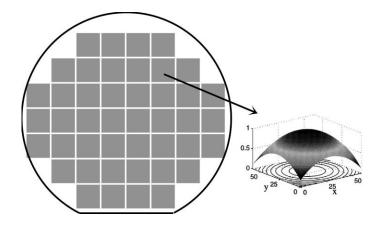

Circuit designers have long been aware of the three primary categories of variation mentioned earlier that affect circuit delays across a chip: *Process Parameters* for NMOS and PMOS devices, *Supply Voltage*, and *Temperature* -- collectively referred to as 'PVT'. Each one varies independently, although there may be correlations between them. These variations could generally be different from within a chip, from chip-to-chip, and from wafer-to-wafer due to integrated circuit (IC) wafer processing and in-situ system performance. However, the chip-to-chip variations (an example of which is shown in Figure 1.3) and wafer-to-wafer variations would equally impact all components and branches of a single chip's clock distribution network. Accordingly, they would not significantly contribute to clock skew within a given chip. Therefore, the greater concern for clock timing performance is due to *intra-chip PVT variation* [12].

Figure 1.3 : Process variation over one die from a wafer (from [16])

The diagram of Figure 1.4 demonstrates an idealized representation of how P, V, and/or T could vary across an H-tree clock distribution network of a single chip. A variety of other gradients are possible by repositioning the center of the variation(s) elsewhere on the clock distribution tree, or by distorting the geometric shapes of the contour lines. These PVT variations could bring about time-invariant differences between the clock branches, or they could be time-varying during circuit operation. Typically, process variations tend to be static in nature but may drift slowly over time, while supply voltage and temperature variations are truly dynamic in nature and depend primarily on the layout of the power/ground grids, the floorplan of the blocks on the chip, and the activity levels of the blocks themselves. As a result, PVT variations must be expected throughout any clock network and will affect latency, skew, and jitter on the clock signal [17][18][19][20][21].

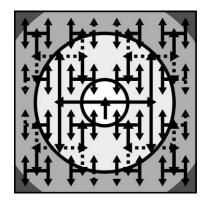

Figure 1.4 : Concentric circles representing P, V, and/or T variations (from [2])

Process variations can be further classified into two distinct categories based upon their degree of correlation across the chip. *Random variations* are considered uncorrelated spatially and therefore they can be modeled as random variables at every location on the chip. *Spatial variations* are highly-correlated across the chip and therefore are modeled as a spatial pattern or gradient across the chip, as in Figure 1.4. Some circuits (e.g., small, matched, localized blocks) may be more affected by random variations, while others (e.g., large, global, dispersed blocks) may be more affected by spatial variations; so, both random and spatial variations must be considered in clock timing analysis.

#### **1.4** Skew and Jitter Reduction and Compensation

Various techniques involving clock buffer sizing and placement, along with clock distribution and power grid balancing, and symmetric layout have been used to keep PVT-induced clock skew and jitter under control [22][23][24][25][26]. Predictions for future process nodes shown earlier indicate that increases in clock skew and jitter will limit the speed gains (due to clock period reductions) that smaller device sizes may offer [3]. Therefore, new and better techniques to reduce clock skew and jitter must be developed and implemented. The main objective in this research is to *greatly reduce clock skew* without degrading clock jitter (or perhaps even improving it) in the presence of PVT variations, and this achievement constitutes the key contribution described in this dissertation.

The research described in the chapters to follow begins by proposing a new method which is minimally disruptive to the ASIC flow and which does not require any changes to the interconnect wires or any increase in the clock buffer area or power. Yet, this new *presilicon* method significantly improves the clock network's timing performance and reduces the effects of intra-chip PVT variations on the clock distribution. This new method is called *Single-Edge Clocking (SEC)*. It focuses clock buffer resources on the timing-critical clock edge to reduce skew and jitter by reducing latency and increasing the edge rate. SEC systems propagate asymmetrical clock signals to favor the clock's critical edge over its other, non-critical, edge. To implement the SEC method, two asymmetric, single-edge

buffers are required to alternately propagate the critical edge through the clock network, and these asymmetric buffer designs are also described in detail.

The results will show that significant timing gains can be realized by replacing the single chain of equal rise/fall buffers with an alternating pattern of asymmetric rise/fall buffers that focus the majority of their current drive only on the one truly critical clock edge -- the edge that ultimately activates the leaf FFs. The other, non-critical, clock edge will be somewhat degraded. However, depending upon the circuit's clock period and timing requirements, that degradation may present no real liability to the circuit's overall performance; therefore, these significant timing gains can be made in nearly any synchronous clock network at little or no additional costs.

Such *pre-silicon* techniques work well to reduce clock skew by adjusting for design and/or layout related imbalances in the clock distribution network and its loads. In fact, the primary advantage of any *pre-silicon* technique is its ability to reduce clock skew prior to the major expense of reticle (or mask set) creation, but its primary disadvantage is its inability to address the causes of clock skew that only arise during circuit operation (after chip fabrication). As previously indicated, each processes shrink causes the on-chip or intradie variability due to numerous PVT variations to grow, and these potentially sizeable postsilicon variations cause clock skew (and jitter) to rapidly consume an increasingly larger percentage of the clock period [12][13]. Since these full-chip variations are nearly impossible to predict and/or control during the design/layout phase, they cannot be addressed until after chip fabrication. Therefore, various types of *post-silicon* techniques will become necessary [22] as PVT variations continue to increase. It is expected that most future designs will incorporate some form of *post-silicon* clock adjustment (via tunable clock buffers, for example) to compensate for the majority of intra-die PVT variations [27][28].

A worthwhile direction for *post-silicon* skew compensation is to configure active (always-on) tuning loops that self-monitor for clock skews and appropriately adjust their tunable buffers [29]. This post-silicon adjustment necessitates the creation and proper insertion of adjustable or tunable components within the clock distribution network – namely, tunable clock buffers. It also requires methods of measuring skew differences of clocks at the appropriate points in the circuit, which are then fed back to the tunable buffers to enable the necessary adjustments. Such systems are commonly referred to as adaptive circuits or active deskewing circuits. As [28] clearly states, new scaling issues will cause more variability in circuits, and therefore designers will likely use more of these adaptive circuits. The work described in later chapters will focus on deskewing networks consisting of multiple clock zones without the availability of chip-wide reference clocks or signals. In particular, this research proposes a novel method of interlinking multiple instances of delaylocked loops (DLLs) into a stable ring configuration. This technique, called ring tuning (RT), will be presented in full for the post-silicon skew compensation of a typical H-tree clock distribution network.

#### **1.5 Research Statement**

#### **Research Objective:**

To build a better clock distribution network for ASICs that is able to automatically compensate for on-chip PVT variations in order to reduce clock skew and clock jitter with no significant increase in overall clock network area or power consumption.

#### **Methodology:**

- Develop a technique that optimizes only one edge of the clock signal -- single-edge clocking (SEC).

- Design asymmetric clock buffers to be used in conjunction with SEC.

- Extend the buffers to provide a tunable mechanism and determine appropriate locations and sizes of these SEC tunable buffers.

- Design a circuit to measure skew between clock edges at different points in the chip for use in automatic skew compensation.

- Develop an overall architecture for clock edge calibration (i.e., setting the adjustable clock buffer tuning values) in order to reduce clock skew.

#### **1.6 Thesis Organization**

The rest of this thesis is organized as follows. Chapter 2 provides the needed background and overview of clock distribution systems. Chapter 3 presents the new *Single Edge Clocking* method for pre-silicon skew reduction. Chapter 4 presents the tunable buffer for SEC, and introduces more specialized SEC applications. Chapter 5 presents the novel *Ring Tuning* architecture for post-silicon skew compensation. Chapter 6 summarizes the findings and recommends directions for future work.

### **Chapter 2 : Synchronous Clock Background**

This introductory chapter provides a background and overview of synchronous clocking techniques and associated definitions for clock metrics. The key issues for clock design are presented, along with a few techniques for clock improvements based on previous work. Section 2.1 begins with a brief review of the clock function, starting with the basic concepts and continuing with clock networks and flip-flops. Section 2.2 discusses Process, Voltage, and Temperature (PVT) variations and their effect on the clock signal. Section 2.3 presents traditional clock buffer design concepts and more advanced adaptive deskewing compensation methodologies. Finally, Section 2.4 summarizes the chapter.

#### 2.1 Clock Function and Design Issues

The clock circuit is the central heartbeat of most VLSI chips and is therefore a critical design component in both digital and analog circuits today. The clock source's primary function is to generate a periodic clock signal that regulates the timing of the entire chip [5]. Almost all circuits designed today are synchronous; although there are some exceptions that are *globally asynchronous*, they still make use of *locally synchronous* clocks [1][4], which is known as 'GALS'. Therefore, this thesis will focus only on the improvement of clocks in synchronous circuits.

Typical synchronous circuits rely upon a highly precise clock signal to trigger the computation of multiple combinational logic blocks which may be widely-distributed across an entire chip. The entire clock system can be divided into three main components: the clock source, the timing flip-flops (FFs), and the clock distribution network.

11

#### 2.1.1 Clock Source

High-frequency clock signals are typically generated on-chip based on a lowfrequency system clock provided at one of the chip input pins. Complex analog circuits designs, such as phase-locked loops (PLLs) or delay-locked loops (DLLs) are commonly used to produce a square-wave signal of the appropriate frequency for the entire chip's timing needs. This "source" clock signal is intended, ideally, to trigger each of the numerous FFs attached to the clock network at exactly the same instance in time. However, since the source clock is only available at the output of the PLL and the timing FFs are widely-distributed across the entire chip, a vast distribution network must be employed to deliver the clock signal ubiquitously and precisely.

#### 2.1.2 Flip-Flop Timing Issues

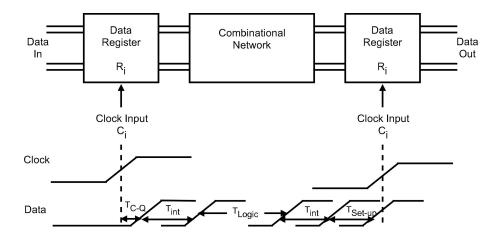

The ultimate timing-related performance of a synchronous circuit depends upon the simultaneous triggering of all the timing FFs. As shown in Figure 2.1, the minimum clock period is ideally the sum of delays through the FFs, logic, interconnect and the FF setup time. However, this simultaneity may be difficult to accomplish since there are many differences (to be elaborated further in this chapter) through the buffers and interconnects from the clock source to the leaf nodes. The key is to identify and to compensate for these differences in the design of the clock distribution network. Hence, any technique to improve the timing accuracy of the final clock signal(s), which triggers the FF(s), will improve the timing performance of the entire chip.

Figure 2.1 : Ideal Synchronous Clock Period (from [5])

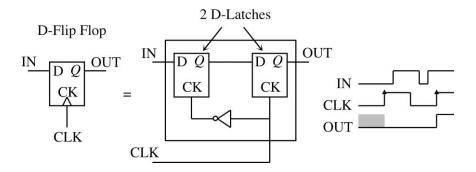

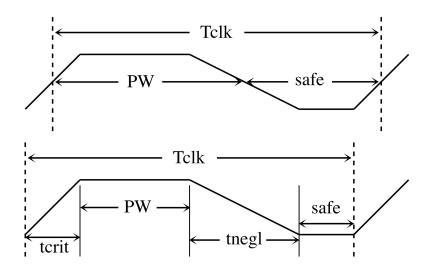

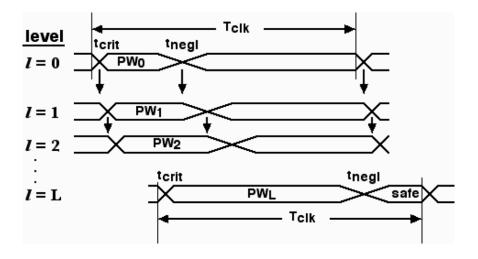

The majority of circuit designs utilize single-edge triggered FFs, such as the one shown in Figure 2.2. Although implementations may vary, this type of FF can be viewed as a D-latch pair. By common definition, latches are *transparent* when their clock, or CK, line is *high*, while FFs are only triggered by a clock *edge*. As the diagrams show, the clock's low level sets up the Q output of the first D-latch, and the clock's subsequent rising edge actually triggers that input value to the FFs output. Therefore, this design is referred to as a *rising-edge triggered* FF. The only timing critical event is the clock's rising edge, provided that the clock's low level is long enough to pass the IN data through the first D-latch. The falling edge of the clock is only used to set up for the next rising edge that triggers the FF again, so the falling edge can occur at any time before the end of the clock period without FF error.

Figure 2.2 : Rising edge-triggered D Flip-flop (from [30])

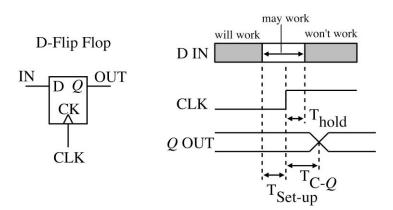

For proper operation, the FF must satisfy certain setup and hold requirements, as shown in Figure 2.3. The FF setup time is defined as the time required for the input data signal to be valid before the incoming clock edge arrives to trigger its capture. Violations of the setup time are due to slow paths in the combinational logic. The setup time adds directly to the idealized clock period, shown earlier in Figure 2.1, and effectively slows down the operating frequency of the chip. The hold time is the time required for the input data to remain valid after the clock edge transition has occurred. Violations are due to fast paths in the logic circuit and they must be slowed down, typically by using delay buffers, to avoid timing problems. As a result, designers work to minimize both setup and hold times of FF's.

Figure 2.3 : Flip-flop setup and hold time definitions (from [30])

The effect of the clock arriving at different times to different FF's may cause them to inadvertently capture incorrect data, which leads to a malfunction in an otherwise working logic design. In effect, the setup and hold times of the FFs are violated by late-arriving or early-arriving clock signals. To be safe, the clock period must be extended by the expected degree of clock edge variation to ensure that the design works properly. While the frequency of operation of the design may be reduced to fix set-up time violations, oftentimes the resulting slower frequency may not satisfy the design specification. Therefore, it is important to identify the sources of the clock edge uncertainty and to reduce this uncertainty as much as possible, as described in the sections to follow.

#### 2.1.3 Clock Distribution Network Design

While a basic understanding of the clock source and leaf FFs is necessary, the research in this dissertation is exclusively focused on improving clock signal delivery via the clock distribution network. The background on this topic is covered in the section below.

#### 2.1.3.1 Basics of Clock Networks

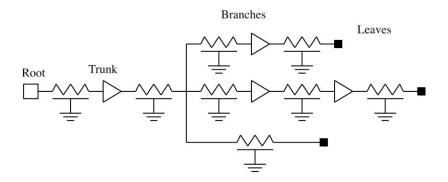

The clock distribution network is usually constructed as either a branching clock tree or some form of an interconnected clock tree/grid hybrid. Regardless of the chosen architecture, the typical clock distribution network is merely composed of two fundamental circuit elements: *buffers* and *wires*, as depicted in Figure 2.4 for a representative clock tree.

Figure 2.4 : Clock Tree Components [Root, Branches, and Leaves] (from [5])

The wires may use all metal layers, but the major trunks are typically routed using the upper layers of metal that tend to be wider and thicker, since large currents are expected to flow through the wires on every cycle. These metal wires are actually distributed RC lines which can be modeled as lumped RC circuits using a  $\pi$ -model for simulation purposes using the effective resistance and capacitance per unit length values. The layout and routing of the clock lines can be quite complex since they compete with power/ground lines and other global signals that also use the upper layers of metal.

In keeping with the "tree" metaphor, the final clock signals (outputs of the final clock buffers) are commonly referred to as the "leaf" nodes of the clock; likewise, the initial or source clock signal is referred to as the "root" node of the clock, and the pathway from the root to any leaf node is a clock "branch". A standard clock tree will have only one root, but multiple branches and leaves. It is the design (placement, sizing, routing, etc.) of these *buffers* and *wires* that ensures the accurate and precise delivery of the clock signal from its single source (root) to its numerous, widespread triggering nodes of FFs (leaves).

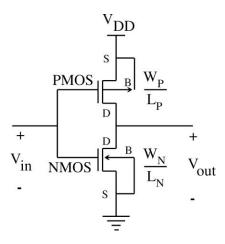

#### 2.1.3.2 Basics of Clock Buffer Design

Clock buffers in CMOS circuits are predominantly large CMOS inverters, as shown in Figure 2.5. They must be large in order to propagate clock signals quickly to the target flops and to drive the large interconnect lines between them. These inverters are sized and placed throughout the clock tree according to various factors usually involving a trade-off between timing (including edge rates and skew), power, and area.

Figure 2.5 : Typical CMOS Inverter (from [30])

The principle design consideration for a CMOS inverter is the ratio of the PMOS width,  $W_P$ , to NMOS width,  $W_N$  [31]. The 50% of VDD crossing point for the timing response equations of the NMOS and PMOS transistors can be used as a measure of the propagation delays for the high-to-low and low-to-high transitions, respectively [30]. A first-order approach to creating a symmetrical clock inverter (i.e., the high-to-low and low-to-high propagation delays are equal) is by plugging the large-scale effective resistance values,  $R_{eff}$  (30k $\Omega/\Box$  for PMOS, 12.5k $\Omega/\Box$  for NMOS) into the propagation delay equation and setting the two equations equal to each other, with  $L_N=L_P$ , leading to:

$$W_P/W_N = 30k\Omega/12.5k\Omega = 2.4$$

(2-1)

Therefore, if the clock buffers are designed to be symmetrical, the PMOS device is customarily 2.4 times larger than the NMOS device for equal rise/fall delays. In the past, this ratio resulted largely from the difference of mobility between holes (for PMOS) and electrons (for NMOS). Today, it is primarily due to differences in velocity saturation of the two types of devices. However, for the remainder of this dissertation, this 2.4X ratio will be rounded up to 2.5X for consistency with other publications. The 2.5X ratio provides a better balance between equal rise/fall times and optimal signal propagation delay through a chain

of inverters. So, this practical value (from HSPICE models derived from actual process data) is more appropriate for use when designing inverters and clock buffers.

A secondary design consideration of the clock buffers is their input and output capacitances. The purpose of a clock buffer is to propagate the input signal to the output by properly driving the output load, but any buffer placed in a signal path, such as the clock tree, will necessarily affect the signal itself. Most significantly, a clock buffer will contain input and output capacitances that must be considered in the signal path's load calculations.

The input capacitance of a CMOS inverter is commonly referred to as the gate capacitance, since the gate terminal is its sole input connection. Basic first-order analysis of a typical CMOS inverter results in the following equation for the inverter's gate capacitance:

$$C_G = C_{Gn} + 2 C_{OL} + C_{Gp} + 2 C_{OL} = (C_{ox}L + 2 C_{ol})(W_N + W_P)$$

(2-2)

Here,  $C_{Gn}$  and  $C_{Gp}$  are gate capacitances of NMOS and PMOS devices, respectively, and  $C_{OL}$  is the overlap capacitance. Since the first parenthesized term of this expression is a constant for a given process technology, the gate capacitance, or input capacitance, of a clock buffer is proportional to the sum of the transistor widths, or  $(W_N + W_P)$ .

The output capacitance, commonly referred to as the self-capacitance, of the same CMOS inverter can be analyzed to obtain:

$$C_{self} = C_{DBn} + C_{DBp} + 2 C_{OL} + 2 C_{OL} = C_{eff} (W_N + W_P)$$

(2-3)

where  $C_{DBn}$  and  $C_{DBp}$  are junction capacitances of NMOS and PMOS devices, respectively, and  $C_{eff}$  is the effective capacitance per width which is taken to be a constant for a given process technology. As a result, the output capacitance is also seen to be proportional to the sum of the transistor widths ( $W_N + W_P$ ), similar to the input capacitance.

#### 2.1.3.3 Other Clock Design Issues

Other issues in clock design concern power and area, as well as noise issues that either affect the clock or are affected by the clock [5]. Predominantly, for power and area reduction, CMOS clock distribution networks have utilized clock inverters in place of (true, non-inverting) clock buffers, and balanced clock trees in place of high-load metal grids. Additionally, clock gating [30] is commonly used to minimize the number of FFs that are unnecessarily triggered, thereby reducing the overall clock power. Interconnect noise issues are typically dealt with by shielding and spacing techniques on the clock wires [6]. Power grid noise is addressed by placing decoupling capacitors close to the large clock buffers [30].

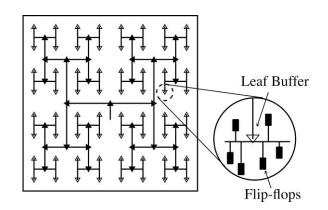

#### 2.1.4 Clock Timing Metrics

This thesis will focus on a common configuration of clock distribution networks; namely, CMOS inverters driving metal wires in the H-tree configuration of Figure 2.6. This regular structure will also allow for a proper, but controlled, test vehicle for the comparison of traditional techniques with new methods to improve the timing characteristics of clocks that will be presented in this thesis.

Figure 2.6 : Typical Synchronous Clock Network [H-tree and FFs] (from [7])

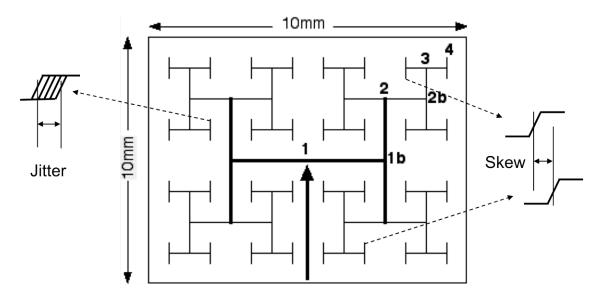

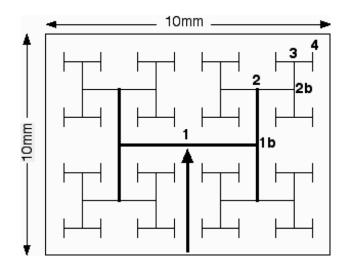

Three important metrics are used to assess the timing performance of a synchronous clock: latency, skew, and jitter, as shown in Figure 2.7. *Latency* is the total path delay from clock root to its leaves where flip-flops (FF) are connected. In Figure 2.7, latency would be measured as the total time for a clock signal to pass from the root buffer (#1) through all the branch wires and buffers (#1b, #2, #2b, and #3) and through the leaf buffer (#4). When two clock architectures both employ the same metal wire H-tree, have the same number of buffers, and roughly the same buffer area and power, yet one delivers the critical clock edge significantly earlier than the other, the faster method would be preferred since a lower latency often implies a lower skew.

Figure 2.7 : Clock Latency, Skew, and Jitter. (#1 = root buffer and #4 = leaf buffer)

In this research no distinction between *local clock skew* (the maximum skew within a given clock zone inside of the chip) and *global clock skew* (the maximum skew within the entire chip) will be made. The design task will be to reduce full-chip clock skew; specifically, to minimize the *maximum clock skew* as defined in Section 1.2, as measured across each of the 64 leaf clocks.

Skew can be caused by mismatches in the clock distribution network and intra-die process variations of one clock path or branch versus another branch. In Figure 2.7, skew is depicted as the measured difference in latency, or delay, between *any two clock leaves*. Designers aim to minimize this value since it directly reduces the usable clock period by the clock skew. That is, it requires that the clock period be increased by at least the amount of skew. Ideally, the paths between the root node and two different FF's should be laid out identically, but this perfect symmetry is often not possible and consequently skew is created [32]. Perhaps even more importantly, the process variations, supply voltage fluctuations, and temperature gradients across the chip (i.e., PVT variations) are major factors in clock skew today.

Jitter is primarily caused by noise impulses on the clock signal, and is therefore very difficult to model and simulate using circuit simulators such as SPICE. In Figure 2.7, it is represented as the time-varying clock edge at *one clock leaf*. The amount of jitter also directly increases the clock period and therefore must be reduced as much as possible. Jitter is due to noise injection effects of the voltage supply, coupling to neighbors that are switching, and other sources such as substrate noise. These noise levels are expected to increase in the future and significantly reduce the usable clock period due to jitter [3], while at the same time the clock period will continue to shrink with each technology generation to further exacerbate the problem. As a result, designers will have to use a variety of methods to get jitter under control. The issue is that each transition of the critical edge of the clock may be exposed to these noise impulses and therefore vulnerable to jitter. Therefore, if the edge-rate of the clock signal can be sharpened, the jitter performance will likely improve. Previous work on jitter, or phase noise in the parlance of analog designers, has led to an

associated metric called the Impulse Sensitivity Function (ISF), which relates jitter performance to clock edge transition slope [15].

#### 2.2 PVT Variations and Skew

Clock distribution networks are *ideally* designed to be perfectly balanced; consequently, every clock branch is identical and no differences in latency exist between any two branches (i.e., zero skew); actually, this layout balance is difficult to achieve but designers and computer-aided design (CAD) tools have been able to reduce skew down to acceptable levels. However, in real-world designs, the variations due to process gradients, and voltage and temperature fluctuations will inevitably impact every clock branch of an actual operating chip differently [33]; therefore, techniques must be applied to the circuit models used for simulation to replicate these PVT variations to obtain early information about the degree of impact they may have on skew, and to propose clock design changes.

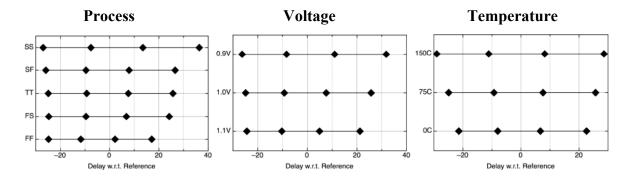

Programs such as HSPICE have built-in static models for simulating different process corners. In a typical process corner each of the contributing factors is listed as Fast (F), Typical (T), or Slow (S). Representation of the NMOS device is listed first, then the PMOS device (e.g., FS for fast-NMOS and slow-PMOS). The supply voltage variations can be VDD+10% (F), VDD (T), and VDD-10% (S). The temperature ranges can be low (F), nominal (T), and high (S). Best-case, worst-case and typical PVT corners can be established with various combinations of P, V and T.

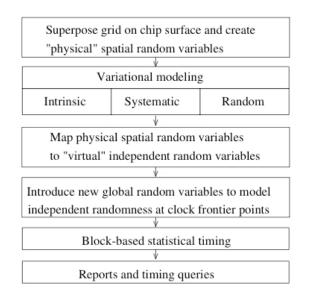

The precise level of skew experienced across any clock distribution network requires highly-accurate models of random and spatial intra-chip variations [2][34][35], which are rarely available for every given process technology, fabrication site, and chip application. Therefore, *two different techniques of modeling the skew caused by PVT variations will be*

*used in this research*. The first technique uses modifications in the circuit model parameters for P, V, and T in order to compare a clock with the fastest possible inverters to one with the slowest possible inverters -- this technique is referred to here as the *worst-case skew* metric. The second technique uses higher-level circuit parameters (such as transistor size or wire length) to mimic intra-die PVT variations that result in clock skew.

The *relative comparison*, which provides meaningful data of the robustness to skew of two clock distribution methods, can be obtained by simulating their *worst-case skew*. Here, the worst-case skew will be taken as the difference in latency, or path delay, of a clock branch simulated with Slowest corner (SS, 0.9V, 150°C) parameters and with Fastest corner (FF, 1.1V, 0°C) parameters in a 90nm CMOS process with a nominal supply voltage of 1.0V. This *worst-case skew* technique works well to compare two clock branches with two separate transient simulations; however, the difficulty of independently setting P, V, and T parameters for every component of a full-chip netlist leads to the usage of higher-level circuit parameters.

Figure 2.8 : PVT Variation Skew Modeling (from [36])

The *higher-level circuit parameter technique* allows for easy and independent modification of every circuit component (transistors and wire segments) within a full-chip netlist. The full-chip schematic is partitioned into numerous sub-blocks and two Matlab created matrices (one for transistors and one for wire segments) are superimposed to create the PVT-induced variations. This higher-level variation technique can be used in the manner outlined in Figure 2.8 to model both *random variations* and *spatial variations* across the full-chip during a single circuit simulation, making it very useful for the Monte Carlo simulations carried out in a later chapter on the topic of ring tuning.

As seen in Chapter 5, both the worst-case skew technique (applied in Chapter 3 simulations) and the higher-level circuit parameter technique (applied in Chapter 5 simulations) result in comparable skew improvement results, confirming their effectiveness.

#### 2.3 Skew Reduction Techniques

Understandably, there have been a wide variety of techniques developed to reduce skew over the years. Here, recently published techniques for skew reduction in clock circuits are summarized. Most attempts are applied in the circuit design phase (i.e., static), called *pre-silicon* techniques. Other attempts are invoked one time or multiple times during a circuit's operation (i.e., dynamic), called *post-silicon* techniques.

#### 2.3.1 Pre-silicon Techniques

Pre-silicon techniques commonly involve a matching or balancing of the clock wires [37], the clock buffers, or both. Design adjustments to the clock distribution network are made based upon simulation and modeling of extracted data -- prior to chip tape-out.

24

#### 2.3.1.1 Balancing Clock Distribution Wires

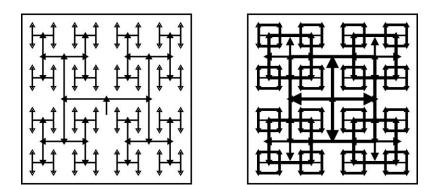

Many elaborate design techniques have been proposed and employed to reduce skew and/or jitter: grid tuning [38], wire snaking [8], delay insertion [23][39], mesh hybrids [24], and link insertion [25][26][40][41][42], to name a few. These techniques recognize that a perfectly balanced distribution network will minimize the variation between clock branches, and thereby reduce clock skew [43]. Unfortunately, the act of balancing out a distribution network typically involves the *addition* of metal, thereby increasing other undesirable effects. One such balancing technique is depicted in Figure 2.9. A typical H-tree (shown on the left) can be better balanced by adding square, metal links in a grid-like fashion (shown on the right).

Figure 2.9 : Balanced H-tree for skew reduction (from [19])

This technique increases the upper layer metal wire area of the distribution network, which in all likelihood will increase its capacitive loading and its power dissipation, and may also necessitate the use of larger clock buffers, further increasing power dissipation and switching noise. It also creates more routing congestion for other global signals that require this metal layer. Therefore, this method of distribution network balancing through 'bulkingup' of the wires will come at a price, so it should only be used sparingly.

#### 2.3.1.2 Balancing Clock Buffers

The clock buffers, or inverters, used to distribute the clock signal have been traditionally balanced in two ways.<sup>1</sup> First, they have been commonly designed as symmetric inverters in which the rising-edge and falling-edge transitions are designed to be equal-but-opposite, as explained previously. This clock signal symmetry has several advantages, such as 50% duty-cycle propagation, minimum combined switching time, and a single, edge-invariant inverter design.

Figure 2.10 : Balanced Buffers for reduced skew (from [45])

The second method of balancing the clock buffers is described in [45] and is shown in Figure 2.10. The primary finding was to show that clock skew can be lessened by keeping the sum of the PMOS devices and the sum of the NMOS devices consistent in all clock branches – regardless of the number of inverters in each branch. By keeping the pullup networks and pull-down networks equal strength across every clock branch, any PVT variations will more likely affect each branch similarly and the resulting clock skew will be minimized.

<sup>&</sup>lt;sup>1</sup> Note that other more elaborate clock buffer techniques have been published to reduce skew, but their complex implementation makes them more of a new clocking architecture rather than just a balanced clock buffer technique [44].

One novel research topic in this dissertation proposes a method of using *asymmetric* inverters in place of symmetric ones for better timing performance with little to no power or area cost. *This asymmetric clock buffer design contravenes the first balanced buffer technique by using unequally weighted pull-up and pull-down individual inverters, but adheres to the second balanced buffer technique by maintaining equal pull-up/pull-down summations throughout every clock branch.*

These asymmetric buffers will be designed such that their  $W_P/W_N$  ratio will be different from the value used by traditional buffers (2.5), but they will keep  $(W_P+W_N)$  the same to ensure that their input and output capacitance effects are nearly identical to the traditional buffers that they are designed to replace. Subsequent design of a complete clock distribution tree involves a combination of the following three in-depth, inverter-design procedures:

- Detailed load calculations The loading along the entire clock tree must be modeled accurately in order to properly design the drive sizes of the clock buffers. Inverter input and output loads, wire loads, and the terminal FF loads all must be considered.

- Gate sizing for optimal path delay More realistic clock waveforms (not just step functions) and transistor models (not just effective channel resistance) must be used along with the detail load model from above when calculating signal and path delays.

Buffer insertion for very long wires - The quadratic delay of long clock wires must be reduced to nearly linear delays with the proper insertion and sizing of additional buffers, or signal repeaters.

One last consideration regarding the clock distribution network design is, of course, the architecture chosen (tree, grid, hybrid, etc.). The balanced, fanout-of-four (FO4) H-tree architecture chosen for this research places several constraints on the placement and fanout of the clock buffers. Modified versions of the H-tree are implemented in practice since it is difficult to use the idealized structure directly on a design with irregular blocks. Clock grids tend to have much lower skews at the expense of area and power, and the hybrid methods attempt to balance the advantages and disadvantages of trees and grids. However, these networks introduce additional constraints depending on the chip being designed. These constraints tend to override some of the detailed calculations from above procedures, so they must be accounted for as well; hence, the idealized H-tree is the best vehicle for comparing the new techniques introduced in this thesis. Further details of the final clock distribution network design will be presented in the next chapter.

# 2.3.2 Post-silicon Techniques (Active De-skewing)

*Pre-silicon* techniques, such as those described in the previous section, work well to reduce clock skew by adjusting for design and/or layout related imbalances in the clock distribution network and its loads. However, on-chip PVT variations are nearly impossible to predict and/or control during the design/layout phase, they cannot be addressed until after chip fabrication. Therefore, some form of post-silicon clock adjustment of skew will be necessary to compensate for the majority of intra-die PVT variations. This post-silicon

adjustment necessitates the creation of an adjustable or tunable component within the clock distribution network – namely, a tunable clock buffer. Furthermore, methods of measuring the skews at key points in the circuit must be developed along with reliable methods of feeding back the skew data to the tunable buffers for skew adjustment.

Research has been performed on tunable delay buffers for various applications [46], targeting the symmetric waveforms of traditional clocking. One-time programmable tunable clock buffers have been used to reduce skews by adjusting clock delays post-silicon based upon wafer probe or assembly final test data gathered from Automatic Test Equipment (ATE) or from a start-up characterization step [47][48]. However, the challenge of precisely measuring numerous internal clock signals during ATE test makes this technique difficult and costly. Furthermore, PVT variations may change over time during normal circuit operation, so an initial, single clock adjustment may not suffice over the device's lifetime usage.

A better approach for post-silicon skew compensation is to configure active (alwayson) tuning loops that self-monitor for clock skews and appropriately adjust their tunable buffers. Such systems are commonly referred to as adaptive circuits or active deskewing circuits. As [28] clearly states, new scaling issues will cause more variability that affects circuit designs, and therefore designers will likely use more of these adaptive circuits.

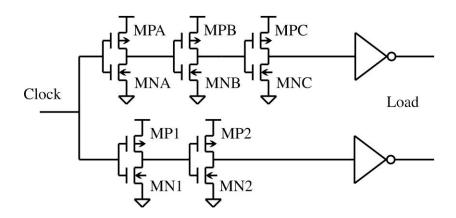

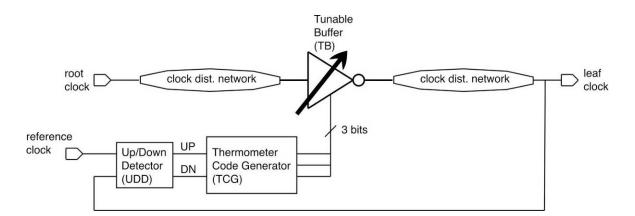

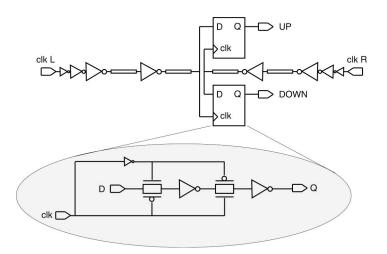

Figure 2.11 : A basic post-silicon skew compensation system (from [49])

Some previous implementations of active deskewing have been adequate at measuring and adjusting two clock regions (or tuning zones) with respect to each other across the entire chip [49][50], as in Figure 2.11. The clock distribution shown on the left side is made tunable by the addition of a phase detector, deskew control, and tunable delay line shown on the right side. However, the anticipated increasing levels of intra-die variations will require a finer resolution of adjustability consisting of many more than just two tunable clock zones, so the sharing of multiple clock zone phase information is critical.

#### 2.3.2.1 Multiple Tuning Zone Synchronization

The traditional DLL architecture, which is commonly used to synchronize clock phases in an active deskewing system, consists of two clock signals: the *tunable clock* is adjusted via tunable buffers to align with a *reference clock*. As mentioned above, the synchronization of clock networks consisting of only two tuning zones is straightforward using a single DLL -- one zone is chosen as the reference, and the other zone is tuned to align with it. However, for clock networks of more than two tuning zones, referred to here as multi-zone networks, a more elaborate configuration of clock phase sharing must be

employed. The simplest of the multi-zone phase sharing configurations is the use of a global reference clock. Having a single ubiquitous reference clock would allow for each tuning zone to align its tunable clock to a single, chip-wide clock phase. The multi-zone synchronization problem can therefore be reduced to multiple instances of the simple two-zone configuration -- one DLL for each zone aligns its tunable clock to the global reference clock. Unfortunately, generating that global reference clock with constant phase for use across the entire chip can be costly.

One such implementation of multi-zone synchronization via a global clock reference is given in [51]. A reference clock is routed in parallel with the main clock to be used for local synchronization, but it requires the addition of a second, identical, balanced clock Htree exclusively for the reference clock distribution. Since the reference clock has no loads, this removes many constraints from the design of its clock tree allowing lower skew to be achieved. In addition, the drivers in the reference network can be smaller than those in the main network. Clock distribution networks are very costly in terms of die area, metal routing, and power consumption; therefore, adding a second clock distribution network is a costly addition that should be avoided if possible.

Another similar implementation is the use of return clocks for phase alignment as in [52][53][54]. Note that a *reference* clock is routed from the clock root to the clock leaves for phase comparison, whereas a *return* clock is routed from the clock leaves back to the clock root for phase comparison, but they both provide the two clocks necessary for multiple implementations of the simple two-zone deskewing system. Again, however, the additional distribution of a return clock can be quite challenging. In [54], the return clock is to be delivered via the clock shielding wires. The shielding wires are included in most clock

distribution networks to isolate the clock signal from the rest of the chip; they are typically connected to ground to help attenuate any switching noise. Redesigning the shielding wires to double as clock returns presents additional complexity in the design.

A slight variant to the global clock reference method is the use of a global timing reference or global control voltage in the case of [55]. That system essentially converts the clock phase difference between the source clock and a return reference clock into a voltage level for use at multiple PLLs. However, distributing a precise, analog control voltage across an entire chip is also challenging, although solutions could be developed to address this issue. Such a voltage reference distribution would still be subject to the unavoidable intra-die PVT variations and various noise sources that would impact each tuning zone randomly, creating skew between zones for which the single, global control voltage could not be adjusted.

Based on the above issues, the work described in this dissertation will focus on deskewing networks consisting of more than two tunable clock zones without requiring chip-wide reference clocks or control signals. A model for multiple PLL clock distribution systems was created in [56] predicting that single PLL systems will be adequate for the 130nm process node, but that four PLLs will be superior for the 100nm node. Continuing with that trend further, multiple PLL (or DLL) clock distribution networks should be considered for future synchronous VLSI designs. Two such multi-zone clock-synchronizing configurations are examined below. The first is a series multi-module architecture, also referred to as a cyclic configuration, and the second is an acyclic configuration. Later, the research described in this dissertation will propose a new method of interlinking multiple instances of DLLs into a stable ring configuration that addresses problems of the previous

32

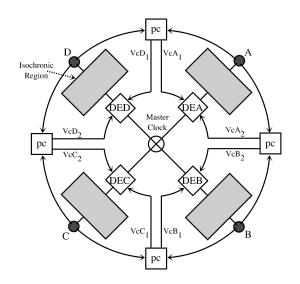

two methods. This novel technique of *Ring Tuning (RT)* will be presented in Chapter 5 for the post-silicon skew compensation of a typical H-tree clock distribution network.

#### **2.3.2.2** Cyclic Architecture

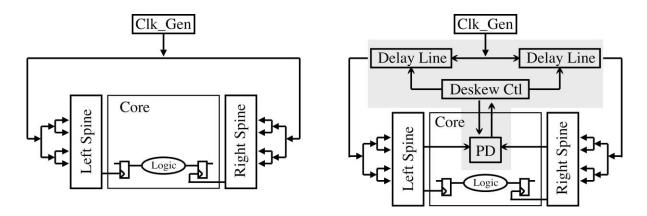

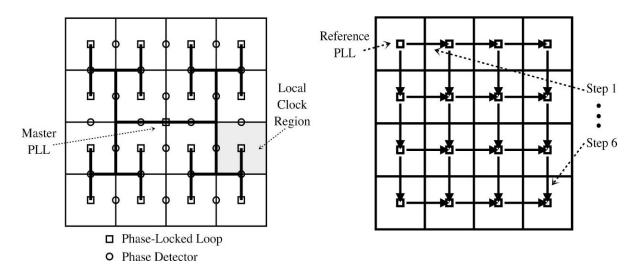

An early multiple PLL system is described in [57]. The schematic of their four PLL series architecture is shown in Figure 2.12. The master clock at the center is distributed to four delay elements that supply their tuned clocks to the four regions labeled A through D. The tuned clock from each region is then fed to two skew sensors (or phase detectors) for comparison with neighboring clocks. Two major issues exist with this proposed implementation: PVT variations on the signals and overall system stability.

Figure 2.12 : Previous multiple PLL ring architecture (from [57])

Firstly, the specifics of distributing the primary clock signals, the analog control voltages, and the feedback clock signals across the entire chip are not addressed. With the high levels of intra-die variation of present and future process nodes, the chip-wide distribution problem must be specified and included in any clock skew results reported. Secondly, the issue of system stability is not adequately covered. As seen in the diagram of

Figure 2.12, each phase comparator (labeled 'pc') produces two control voltages (one for each of two neighboring delay elements), and consequently each delay element receives two different analog control voltages. How these separate voltages are handled so as not to result in overall system instability is not sufficiently discussed. In fact, three distinct types of stability must be considered for any cyclic architecture. For the purpose of this research, these three varieties of stability will be referred to as *Mode-lock, Mode-lock Oscillation*, and *Cyclic-Feedback Oscillation*.