# Implementation of Algorithms to Determine the Capacitance Sensitivity of Interconnect Parasitics in the Magic VLSI Layout Tool

by

Nick Kuan-Hsiang Huang B.A.Sc., The University of British Columbia, 2007

## A THESIS SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF

MASTER OF APPLIED SCIENCE

$\mathrm{in}$

The College of Graduate Studies

(Electrical Engineering)

THE UNIVERSITY OF BRITISH COLUMBIA

(Okanagan)

September 2009

© Nick Kuan-Hsiang Huang, 2009

# Abstract

VLSI interconnect capacitance is becoming more significant and also increasingly subject to process variation in the deep submicron regime. A new set of capacitance models is implemented in the Magic VLSI layout tool to improve the capacitance accuracy based on 2.5D capacitance models. This involves a new technology file, equations, and search algorithms. In addition, a simple technique to extract from layout the sensitivity of interconnect parasitic capacitance to linewidth process variation is proposed based on the new capacitance models and implemented in Magic. The derivative of each extracted capacitance with respect to linewidth variation in every level is obtained. Coincident edges in layout result in distinct "shrinking" and "bloating" derivatives. The derivatives therefore form a gradient that may be multiplied by a vector of the variations on each level to give the total expected deviation from nominal capacitance. The gradient allows the process sensitivity of each capacitance to be determined by simply inspecting the netlist. In the end, the impact of process variation is simulated in a crosstalk application to emphasize the necessity of process variation awareness.

# **Table of Contents**

| Ab       | ostrac     | t              |          |        |       | • •  |      | ••  | ••             | ••• | • | ••• | • • | • | ••• | • | ••• | • | • | ••• | ii   |

|----------|------------|----------------|----------|--------|-------|------|------|-----|----------------|-----|---|-----|-----|---|-----|---|-----|---|---|-----|------|

| Lis      | st of I    | <b>F</b> ables |          |        |       |      |      | ••• | •••            |     | • | ••• | ••• | • | ••• | • |     | • | • | • • | viii |

| Lis      | st of I    | Figures        | • • • •  |        |       |      |      |     |                |     | • | • • |     | • |     | • |     | • | • |     | ix   |

| Lis      | st of A    | Acronyr        | ms       |        |       |      |      |     | •••            |     | • | • • |     | • |     | • |     | • | • |     | xii  |

| Ac       | know       | ledgem         | ents     | ••••   |       | •••  |      |     |                |     | • |     |     | • |     | • |     | • | • |     | xiv  |

| 1        | Intro      | oductio        | n        |        |       | ••   |      |     |                |     | • |     |     | • |     |   |     |   | • |     | 1    |

|          | 1.1        | Motiva         | ation    |        |       |      | ••   |     | •••            |     |   |     |     | • |     |   |     | • | • |     | 1    |

|          | 1.2        | Resear         | rch Goal | s      |       |      | •••  |     | •••            |     | • |     |     | • |     | • |     | • | • |     | 2    |

|          | 1.3        | Thesis         | Organiz  | zation |       |      |      | ••• |                |     | • | ••• | • • | • |     | • |     | • | • | ••• | 4    |

| <b>2</b> | Back       | ground         | l and Re | levant | : Wo  | ork  |      |     |                |     |   |     |     | • |     | • |     | • | • |     | 5    |

|          | <b>2.1</b> | Interco        | onnect I | Design | The   | eory | •    | ••• | •••            |     | • | ••• | ••• | • |     | • |     | • | • |     | 6    |

|          |            | 2.1.1          | Deep-S   | ubmic  | ron   | Inte | erco | onn | $\mathbf{ect}$ |     | • | ••• | ••• | • |     | • | ••• | • | • |     | 6    |

|          |            | 2.1.2          | Parasit  | ic Res | sista | nce  | ••   | ••• | •••            |     | • | ••• |     | • |     | • |     | • | • |     | 7    |

|          |            | 2.1.3          | Parasit  | ic Cap | oacit | anc  | е.   |     |                |     |   |     |     | • |     | • |     |   | • |     | 8    |

|   |             | 2.1.4 | Inductance                                                                               | 11 |

|---|-------------|-------|------------------------------------------------------------------------------------------|----|

|   | 2.2         | Capac | itance Extraction                                                                        | 13 |

|   |             | 2.2.1 | Analytical Formulae                                                                      | 13 |

|   |             | 2.2.2 | Field Solver                                                                             | 15 |

|   |             |       | 2.2.2.1 Random Walk Method                                                               | 15 |

|   |             |       | 2.2.2.2 Volume-Based Method                                                              | 17 |

|   |             |       | 2.2.2.3 Surface-Based Method                                                             | 18 |

|   |             |       | 2.2.2.4 Field Solver Summary                                                             | 21 |

|   |             | 2.2.3 | Library Look-Up Based Method                                                             | 21 |

|   | 2.3         | Comm  | nercial Parasitic Extraction                                                             | 22 |

|   |             | 2.3.1 | Synopsys - Star-RCXT                                                                     | 23 |

|   |             | 2.3.2 | Cadence QRC Extraction                                                                   | 23 |

|   |             | 2.3.3 | Mentor Graphics - Calibre LFD                                                            | 25 |

|   |             | 2.3.4 | Magma - QuickCap                                                                         | 25 |

|   |             | 2.3.5 | Space 3D                                                                                 | 27 |

|   |             | 2.3.6 | Industry Parasitic Extraction Summary                                                    | 27 |

|   | <b>2.4</b>  | Magic | Technology Files for Look Up-Based Method                                                | 28 |

|   |             | 2.4.1 | Stack File                                                                               | 28 |

|   |             | 2.4.2 | Techgen                                                                                  | 29 |

| 0 | <b>D!</b> - |       |                                                                                          | 20 |

| 3 |             | 0     | apacitance Extraction Model of Magic                                                     | 30 |

|   | 3.1         | 0     | Database                                                                                 | 31 |

|   |             | 3.1.1 | Geometry                                                                                 | 31 |

|   |             |       | $3.1.1.1  \text{Point}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $ | 31 |

|   |             |       | 3.1.1.2 Rectangle                                                                        | 31 |

|   |             | 3.1.2 | Corner Stitched Tile                                                                     | 32 |

|   |             | 3.1.3 | Plane                                                                                    | 34 |

|   |             |       | 3.1.3.1 Coverage                                                                         | 36 |

|   |             |       | 3.1.3.2 Strips                                                                           | 36 |

|   |            |         | 3.1.3.3 Stitches                        | 37 |

|---|------------|---------|-----------------------------------------|----|

|   | <b>3.2</b> | Magic   | Technology File                         | 38 |

|   |            | 3.2.1   | Planes                                  | 39 |

|   |            | 3.2.2   | Contact                                 | 40 |

|   |            | 3.2.3   | DRC                                     | 41 |

|   |            |         | 3.2.3.1 Width rules                     | 41 |

|   |            |         | 3.2.3.2 Spacing rules                   | 41 |

|   |            | 3.2.4   | Extract                                 | 42 |

|   |            |         | 3.2.4.1 Resistance                      | 45 |

|   | <b>3.3</b> | Magic   | Capacitance Extraction                  | 45 |

|   |            | 3.3.1   | Overlap Capacitance Extraction          | 46 |

|   |            | 3.3.2   | Sidewall Capacitance Extraction         | 47 |

|   |            | 3.3.3   | Sidewall Overlap Capacitance Extraction | 49 |

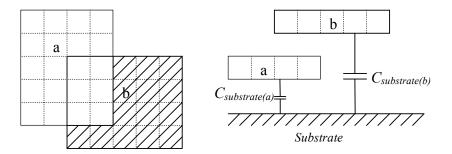

|   |            | 3.3.4   | Substrate Capacitance Extraction        | 50 |

|   | <b>3.4</b> | Magic   | Extraction Output                       | 51 |

|   |            | 3.4.1   | Extraction File                         | 52 |

|   |            | 3.4.2   | Simulation File                         | 53 |

|   | 3.5        | Summ    | nary                                    | 53 |

| 4 | Inte       | gration | of New Capacitive Model into Magic      | 55 |

|   | 4.1        | CUP 1   | models                                  | 55 |

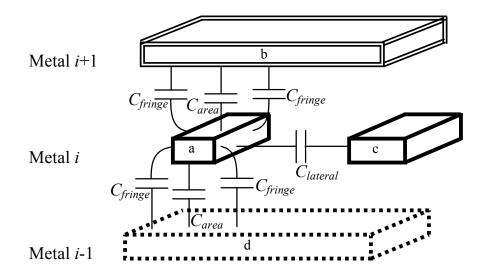

|   |            | 4.1.1   | Area Capacitance                        | 56 |

|   |            | 4.1.2   | Lateral Capacitance                     | 58 |

|   |            | 4.1.3   | Fringe Capacitance                      | 61 |

|   |            | 4.1.4   | Model Fit                               | 65 |

|   | 4.2        | Chang   | ges to Magic File Formats               | 66 |

|   |            | 4.2.1   | Technology File Changes                 | 66 |

|   |            | 4.2.2   | New Extraction Output                   | 66 |

|   | 4.3        | Linew   | idth Variation                          | 67 |

|          | 4.4        | Algorithms Implementation              | 69 |

|----------|------------|----------------------------------------|----|

|          |            | 4.4.1 Real Edges                       | 70 |

|          |            | 4.4.2 Coincident Edges                 | 70 |

|          |            | 4.4.3 Pixel-based Search Algorithms    | 72 |

|          | 4.5        | Summary                                | 75 |

| <b>5</b> | Sim        | lation and Evaluation                  | 76 |

|          | 5.1        | Capacitance Comparison                 | 77 |

|          |            | 5.1.1 Space 3D - OptEM                 | 78 |

|          |            | 5.1.2 Capacitance Comparison Results   | 79 |

|          | 5.2        | Linewidth Process Variation Evaluation | 81 |

|          |            | 5.2.1 Crosstalk                        | 81 |

|          |            | 5.2.1.1 Interconnect                   | 82 |

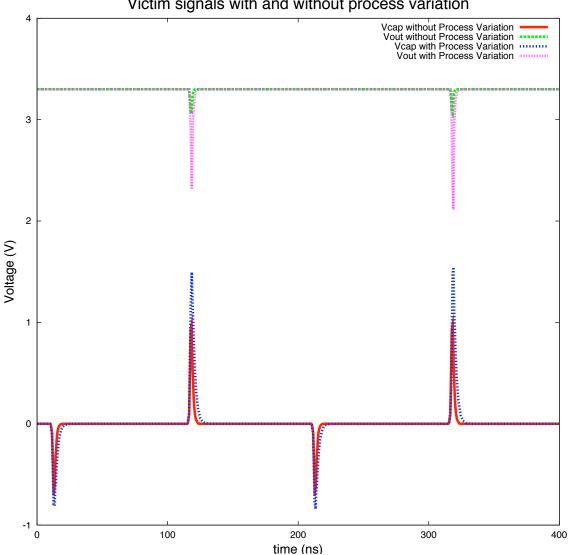

|          |            | 5.2.2 Crosstalk Simulation Results     | 88 |

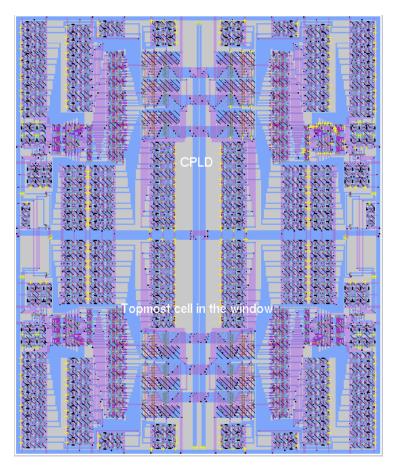

|          | 5.3        | Runtime Analysis                       | 90 |

|          | <b>5.4</b> | Summary                                | 93 |

| 6        | Con        | lusion and Future Work                 | 94 |

|          | 6.1        | Contributions                          | 94 |

|          | 6.2        | Interpretation of Results              | 94 |

|          | 6.3        | Limitations                            | 95 |

|          | 6.4        | Future Work                            | 96 |

|          |            | 6.4.1 Process Variations               | 96 |

|          |            | 6.4.2 Capacitance Models               | 96 |

|          |            | 6.4.3 Accuracy                         | 97 |

|          |            | 6.4.4 Runtime                          | 97 |

| Bi       | bliogi     | phy                                    | 98 |

|          | 0          |                                        |    |

| Aj           | ppendices                               | 105 |

|--------------|-----------------------------------------|-----|

| A            | Stack file                              | 106 |

|              | A.1 Create a Stack File                 | 106 |

|              | A.2 Stack Diagram                       | 107 |

| В            | Magic Tile Search Algorithm             | 108 |

| С            | Area Capacitance Edge Implementation    | 110 |

| D            | Magic Technology File on Extraction     | 112 |

| $\mathbf{E}$ | Magic Output Files                      | 118 |

|              | E.1 Ext File                            | 118 |

|              | E.2 Spice File                          | 119 |

|              | E.3 Final Spice File                    | 119 |

| F            | Model Fit to Field Solver               | 120 |

| $\mathbf{G}$ | Magic Codes                             | 132 |

|              | G.1 Real and Coincident Edge Algorithms | 132 |

|              | G.2 Pixel-Based Search Algorithms       | 140 |

Table of Contents

# List of Tables

| 2.1 | Information of Figure 2.4           | 10 |

|-----|-------------------------------------|----|

| 2.2 | Commercial extraction methods       | 27 |

| 3.1 | Planes section                      | 40 |

| 3.2 | Contact section                     | 40 |

| 3.3 | DRC section                         | 41 |

| 3.4 | Extract section                     | 43 |

| 3.5 | Node output                         | 52 |

| 3.6 | Coupling capacitance output         | 53 |

| 4.1 | New technology parameters           | 67 |

| 4.2 | Capacitance derivative array        | 68 |

| 5.1 | Capacitance comparison              | 79 |

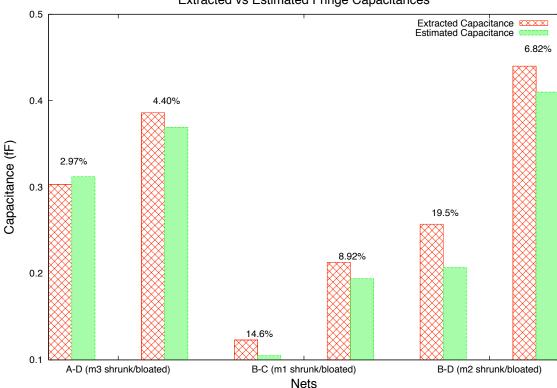

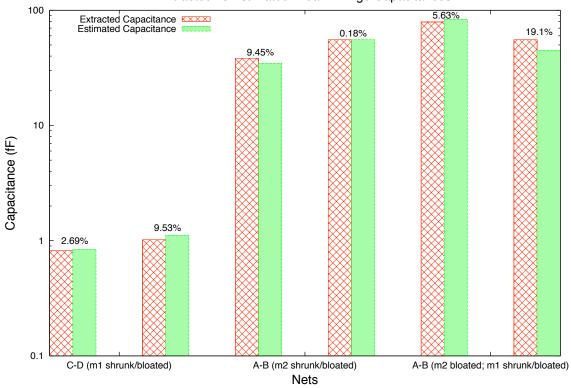

| 5.2 | Extracted vs estimated capacitances | 85 |

| 5.3 | Runtime record                      | 92 |

# List of Figures

| 2.1  | Resistance cross-sectional area reduction from 90 nm to 65 nm technology    |    |

|------|-----------------------------------------------------------------------------|----|

|      | nodes                                                                       | 8  |

| 2.2  | Capacitance configuration in a typical DSM technology with 1.5 aspect ratio | 8  |

| 2.3  | Capacitance in old assumption and DSM                                       | 9  |

| 2.4  | Interconnect vs gate delay                                                  | 11 |

| 2.5  | Conductor with a rectangular cross-section                                  | 14 |

| 2.6  | Sample random walk method                                                   | 16 |

| 2.7  | Sample finite element method (idealization of a beam)                       | 17 |

| 2.8  | Overall flow of interconnect library model                                  | 22 |

| 2.9  | Star-RCXT's sensitivity-based extraction solution                           | 24 |

| 2.10 | Cadence QRC extraction's advanced capabilities                              | 25 |

| 2.11 | QuickCap NX's process variation solution                                    | 26 |

| 3.1  | Point structure                                                             | 31 |

| 3.2  | Rectangle structure                                                         | 32 |

| 3.3  | Corner-stitching (Manhattan shape)                                          | 32 |

| 3.4  | Basic tile structure                                                        | 34 |

| 3.5  | Coverage tile                                                               | 36 |

| 3.6  | Strips tile                                                                 | 37 |

| 3.7  | Stitch tile                                                                 | 38 |

| 3.8  | Tile search algorithm pseudo code                                           | 39 |

| 3.9  | Sidewall technology line description                                        | 44 |

|      |                                                                             |    |

### List of Figures

| 3 10 | Overlap capacitance                                                                                                         | 46  |

|------|-----------------------------------------------------------------------------------------------------------------------------|-----|

|      |                                                                                                                             |     |

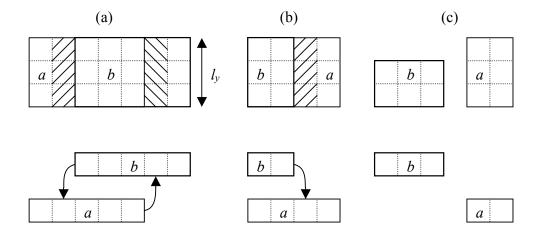

| 3.11 | Sidewall capacitance                                                                                                        | 47  |

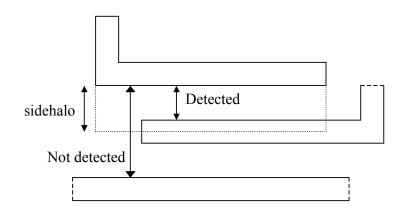

| 3.12 | Sidewall capacitance detection                                                                                              | 49  |

| 3.13 | Sidewall overlap capacitance                                                                                                | 50  |

| 3.14 | Substrate capacitance                                                                                                       | 51  |

|      |                                                                                                                             | ~ - |

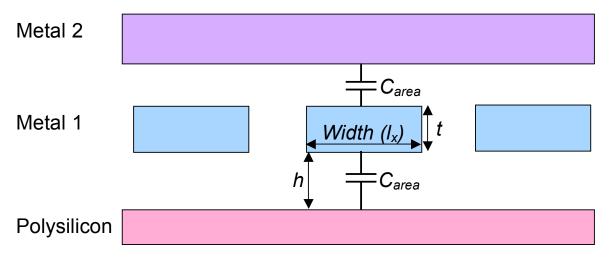

| 4.1  | Capacitance configuration                                                                                                   | 57  |

| 4.2  | Area capacitance                                                                                                            | 57  |

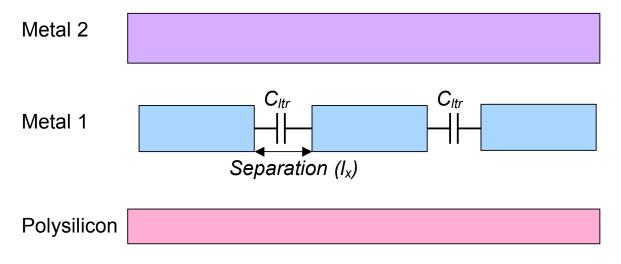

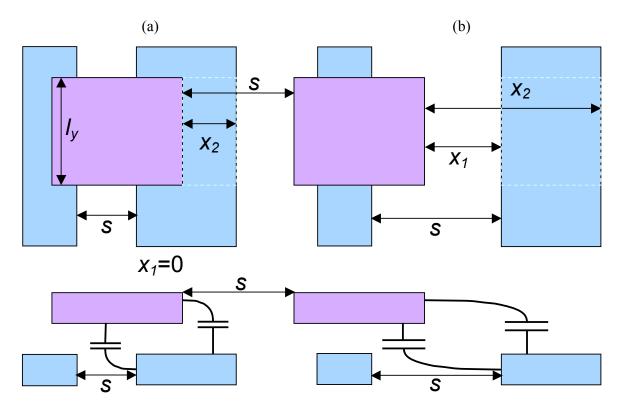

| 4.3  | Lateral capacitance                                                                                                         | 58  |

| 4.4  | Lateral capacitance schematic                                                                                               | 60  |

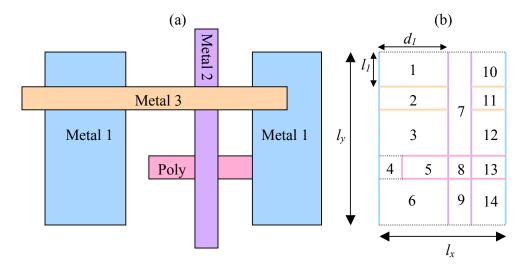

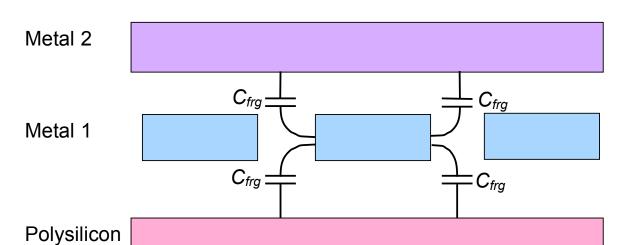

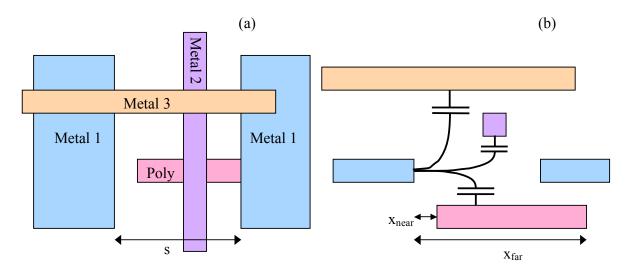

| 4.5  | Fringe capacitance                                                                                                          | 62  |

| 4.6  | Lateral capacitance between two layers                                                                                      | 63  |

| 4.7  | Fringe capacitance schematic                                                                                                | 64  |

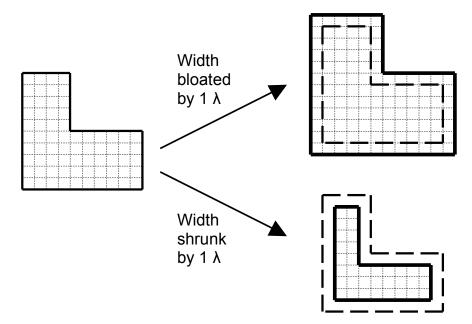

| 4.8  | Linewidth variation                                                                                                         | 69  |

| 4.9  | A sample layout illustrating real edges                                                                                     | 70  |

| 4.10 | A sample layout illustrating coincident edges                                                                               | 71  |

| 4.11 | $extRealEdge() \ function \ pseudocode \ \ \ldots $ | 73  |

| 4.12 | Pixel-based search algorithm                                                                                                | 74  |

| 5.1  | CAD flow                                                                                                                    | 77  |

| 5.2  | Space 3D layout                                                                                                             | 78  |

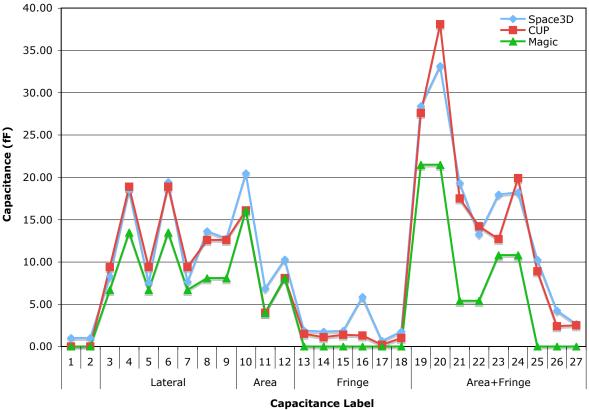

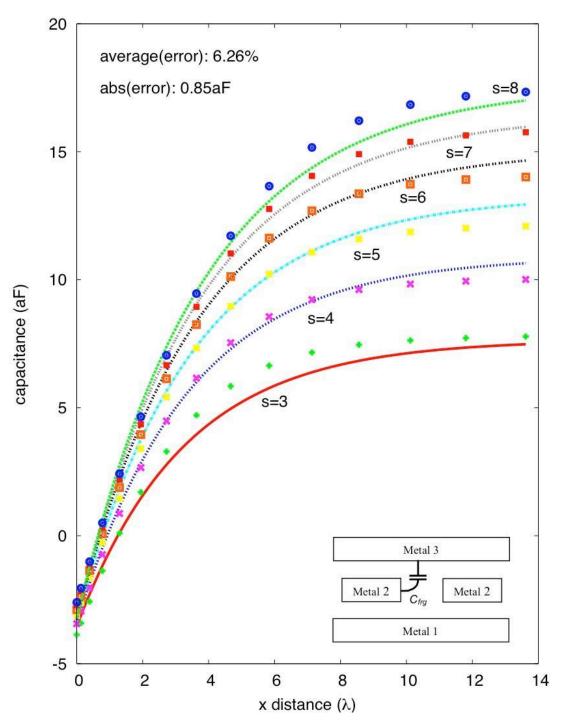

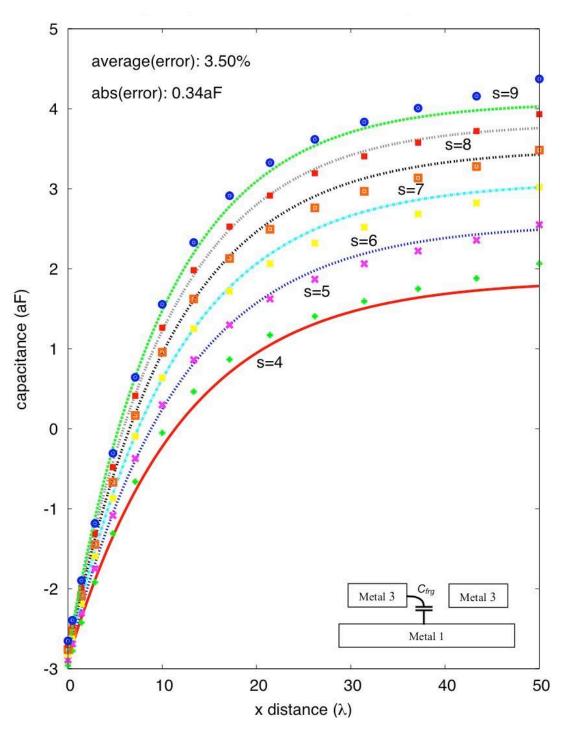

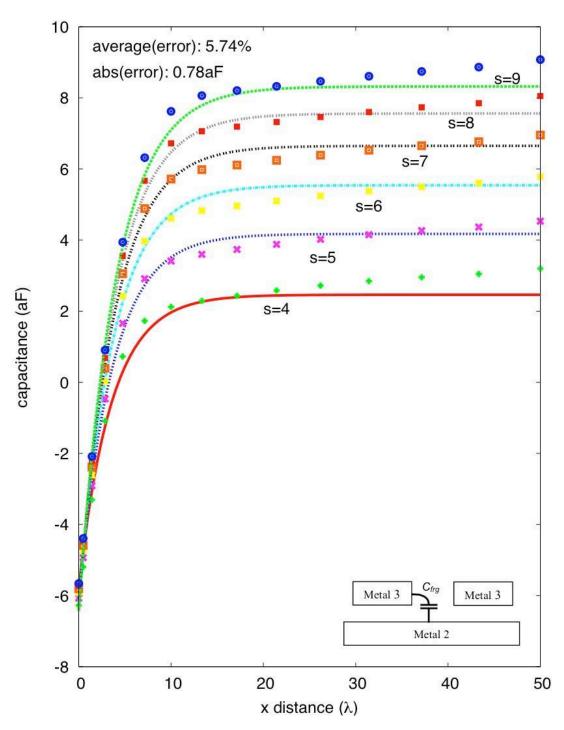

| 5.3  | Capacitance comparison between Space 3D, CUP, and Magic                                                                     | 80  |

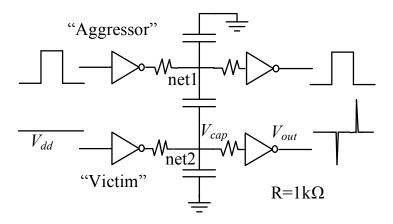

| 5.4  | Crosstalk configuration                                                                                                     | 82  |

| 5.5  | Magic interconnect layouts with nets A, C on metal 1, B on metal 2, and D                                                   |     |

|      | on metal 3                                                                                                                  | 83  |

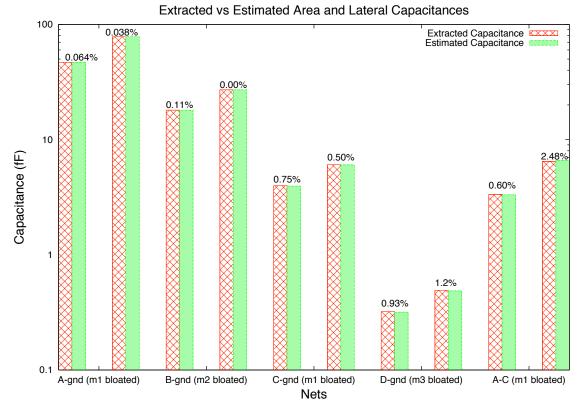

| 5.6  | Extracted vs estimated area and lateral capacitances                                                                        | 86  |

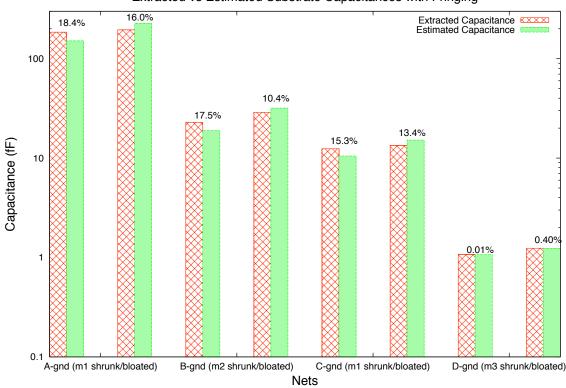

| 5.7  | Extracted vs estimated substrate capacitances with fringing                                                                 | 87  |

| 5.8  | Extracted vs estimated fringe capacitances                                                                                  | 88  |

| 5.9  | Extracted vs estimated area + fringe capacitances                                                                           | 89  |

### List of Figures

| 5.10 | Victim signals with and without process variation                      | ) |

|------|------------------------------------------------------------------------|---|

| 5.11 | CPLD layout                                                            | 1 |

| 5.12 | Runtime analysis                                                       | 2 |

| A.1  | Metal configuration from the stack file                                | 7 |

| B.1  | Magic tile search algorithm                                            | 3 |

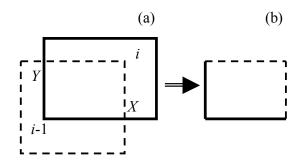

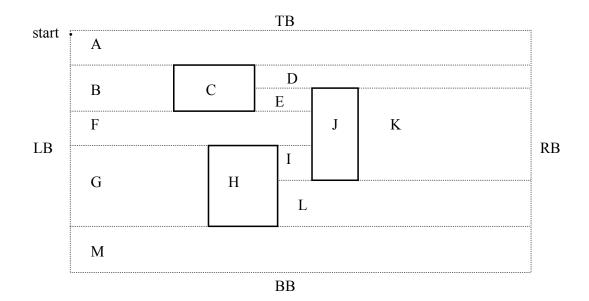

| C.1  | Area capacitance edge computation                                      | 1 |

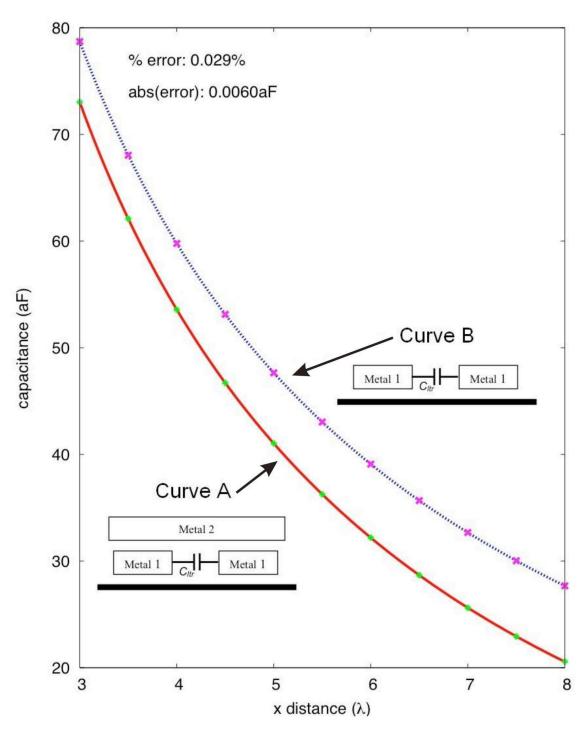

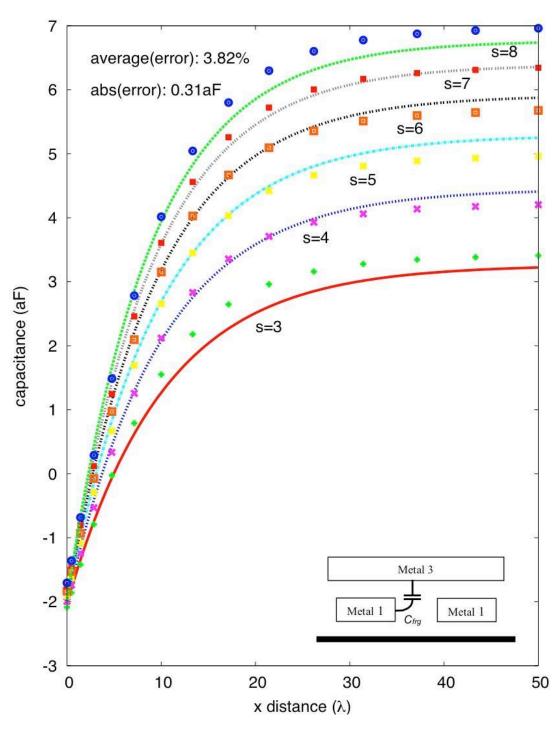

| F.1  | Lateral capacitance on metal 1 per $\lambda$                           | 1 |

| F.2  | Lateral capacitance on metal 2 per $\lambda$                           | 2 |

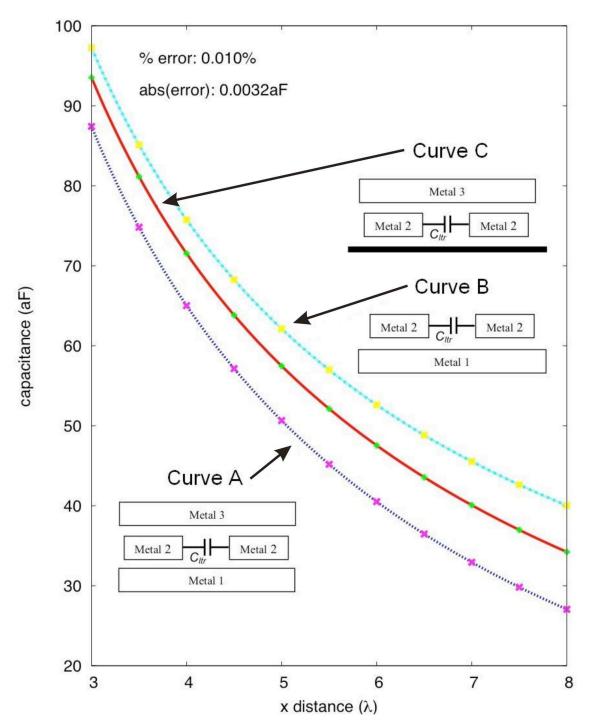

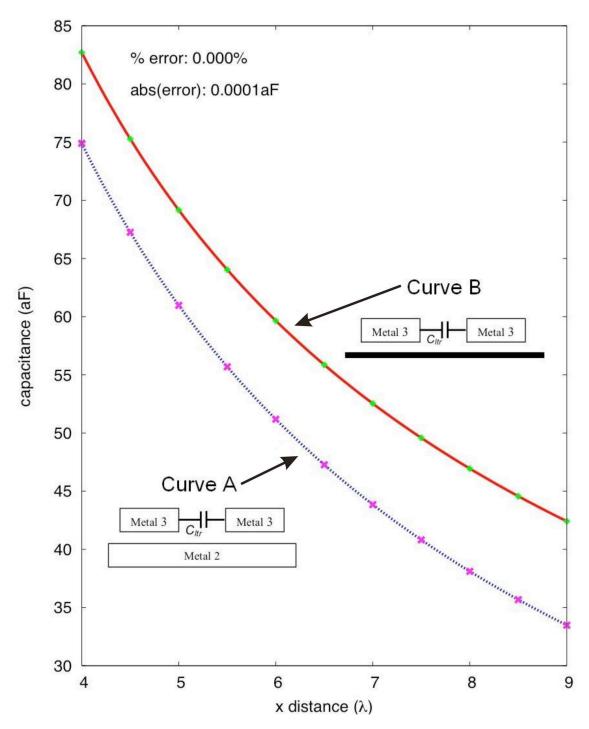

| F.3  | Lateral capacitance on metal 3 per $\lambda$                           | 3 |

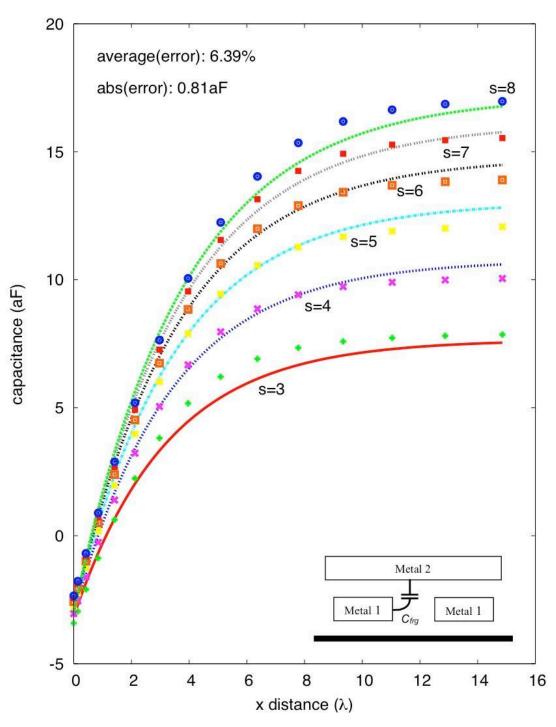

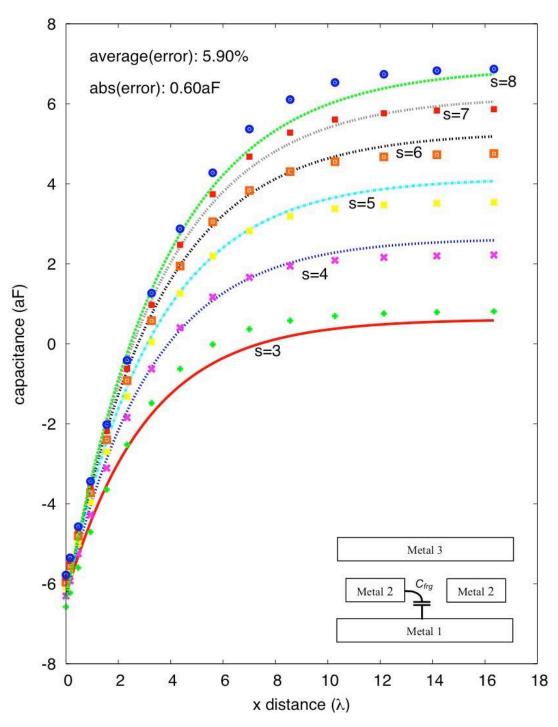

| F.4  | Fringe capacitance metal 1 to metal 2 with substrate per $\lambda$     | 4 |

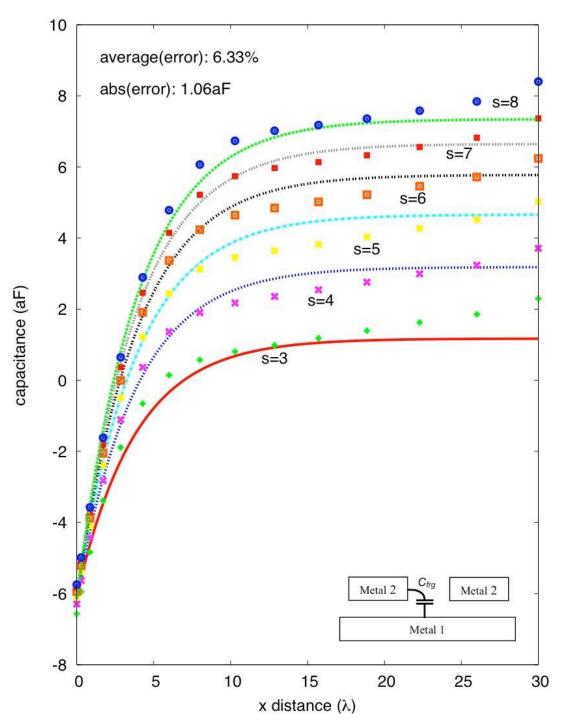

| F.5  | Fringe capacitance metal 1 to metal 3 with substrate per $\lambda$     | 5 |

| F.6  | Fringe capacitance metal 2 to metal 1 with metal 3 above per $\lambda$ | ĵ |

| F.7  | Fringe capacitance metal 2 to metal 1 with space above per $\lambda$   | 7 |

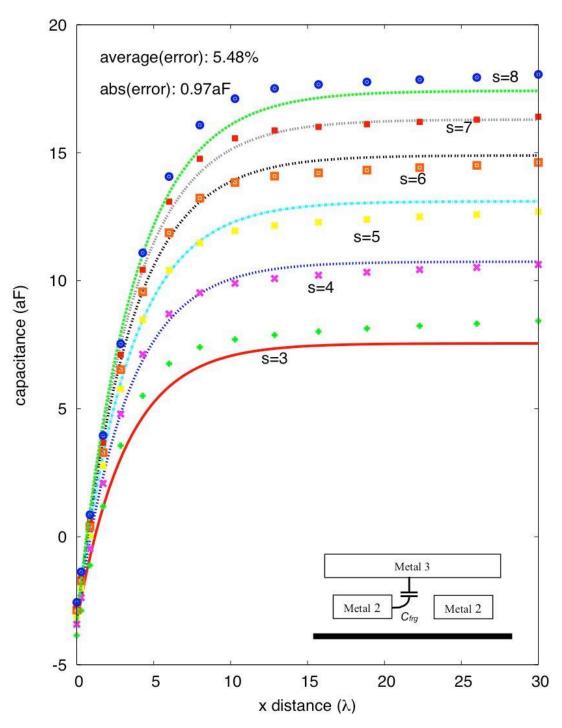

| F.8  | Fringe capacitance metal 2 to metal 3 with substrate per $\lambda$     | 3 |

| F.9  | Fringe capacitance metal 2 to metal 3 with metal 1 below per $\lambda$ | 9 |

| F.10 | Fringe capacitance metal 3 to metal 1 with space above per $\lambda$   | ) |

| F.11 | Fringe capacitance metal 3 to metal 2 with space above per $\lambda$   | 1 |

# List of Acronyms

| 3D                     | $\mathbf{T}$ hree- $\mathbf{D}$ imensional                                                                                                                                                                         |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AMS                    | $\mathbf{A}\mathrm{nalog}/\mathbf{M}\mathrm{ixed}\text{-}\mathbf{S}\mathrm{ignal}$                                                                                                                                 |

| ASIC                   | ${\bf A} {\rm pplication}{\textbf{-s}} {\rm pecific} \ {\bf Integration} \ {\bf C} {\rm ircuit}$                                                                                                                   |

| BEM                    | $\mathbf{B} \mathbf{oundary}\textbf{-} \mathbf{E} \mathbf{lement} \ \mathbf{M} \mathbf{e} \mathbf{thod}$                                                                                                           |

| CAD                    | $\mathbf{C} \mathbf{o} \mathbf{n} \mathbf{p} \mathbf{u} \mathbf{t} \mathbf{r} \mathbf{-} \mathbf{a} \mathbf{i} \mathbf{d} \mathbf{e} \mathbf{d} \mathbf{D} \mathbf{e} \mathbf{s} \mathbf{i} \mathbf{g} \mathbf{n}$ |

| $\operatorname{CMP}$   | $ {\bf Chemical \ Mechanical \ Polishing } $                                                                                                                                                                       |

| CPLD                   | $\mathbf{C} \mathbf{omplex} \ \mathbf{P} \mathbf{r} \mathbf{ogrammable} \ \mathbf{L} \mathbf{ogic} \ \mathbf{D} \mathbf{evice}$                                                                                    |

| $\mathbf{CPU}$         | Central Processing Unit                                                                                                                                                                                            |

| DRC                    | Design-Rule Check                                                                                                                                                                                                  |

| $\mathbf{DSM}$         | $\mathbf{D}$ eep $\mathbf{S}$ ub $\mathbf{m}$ icron                                                                                                                                                                |

| EDA                    | Electronic Design Automation                                                                                                                                                                                       |

| $\mathbf{FD}$          | Finite-Difference                                                                                                                                                                                                  |

| $\mathbf{FE}$          | Finite-Element                                                                                                                                                                                                     |

| $\mathbf{FFT}$         | ${\bf Fast} \ {\bf Fourier} \ {\bf T}ansform$                                                                                                                                                                      |

| FMM                    | ${\bf F} {\rm ast} \ {\bf M} {\rm ultipole} \ {\bf M} {\rm ethod}$                                                                                                                                                 |

| FHM                    | ${\bf F} ast {\bf H} ierarchical {\bf M} ethod$                                                                                                                                                                    |

| HILEX                  | $\mathbf{HI}$ erarchical Layout $\mathbf{EX}$ traction                                                                                                                                                             |

| IC                     | Integrated Circuit                                                                                                                                                                                                 |

| $\mathbf{LER}$         | line $\mathbf{e}$ dge $\mathbf{r}$ oughness                                                                                                                                                                        |

| $\mathbf{LFD}$         | $\mathbf{L}$ itho- $\mathbf{F}$ riendly $\mathbf{D}$ esign                                                                                                                                                         |

| $\mathbf{L}\mathbf{M}$ | $\mathbf{L} even berg\textbf{-} \mathbf{M} arquardt$                                                                                                                                                               |

| LSI                    | Large-Scale Integration                                                                                                                                                                                            |

| MOS                              | $\mathbf{M} etal\textbf{-} \mathbf{O} xide\textbf{-} \mathbf{S} emiconductor$                                                                                                                                                                       |

|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MSI                              | $\mathbf{M} \mathbf{e} \mathbf{d} \mathbf{i} \mathbf{u} \mathbf{m} \textbf{-} \mathbf{S} \mathbf{c} \mathbf{a} \mathbf{l} \mathbf{e} \mathbf{I} \mathbf{n} \mathbf{t} \mathbf{e} \mathbf{g} \mathbf{r} \mathbf{a} \mathbf{t} \mathbf{o} \mathbf{n}$ |

| nm                               | $\mathbf{n}$ ano- $\mathbf{m}$ eter                                                                                                                                                                                                                 |

| OPC                              | $\mathbf{O} \mathrm{ptical} \ \mathbf{P} \mathrm{roximity} \ \mathbf{C} \mathrm{orrection}$                                                                                                                                                         |

| $\mathbf{Q}\mathbf{M}\mathbf{M}$ | $\mathbf{Q}$ uasi- $\mathbf{M}$ ultiple $\mathbf{M}$ edium                                                                                                                                                                                          |

| $\mathbf{RF}$                    | $\mathbf{R}$ adio- $\mathbf{F}$ requency                                                                                                                                                                                                            |

| RWM                              | ${\bf R} {\rm andom} \ {\bf W} {\rm alk} \ {\bf M} {\rm ethod}$                                                                                                                                                                                     |

| SI                               | $\mathbf{S}$ ignal $\mathbf{I}$ ntegrity                                                                                                                                                                                                            |

| SoC                              | $\mathbf{S}$ ystem-on-Chip                                                                                                                                                                                                                          |

| SSI                              | $\mathbf{S} \text{mall-} \mathbf{S} \text{cale Integration}$                                                                                                                                                                                        |

| SVD                              | ${\bf S} {\rm ingular} \ {\bf V} {\rm alue} \ {\bf D} {\rm ecomposition}$                                                                                                                                                                           |

| UDSM                             | Ultra-Deep Submicron                                                                                                                                                                                                                                |

| VLSI                             | $\mathbf{V} ery\text{-}\mathbf{L} arge\text{-}\mathbf{S} cale \ \mathbf{I} ntegration$                                                                                                                                                              |

# Acknowledgements

I would first like to thank my academic supervisor, Dr. Andrew Labun, for the guidance, technical advice, support, dedication, and patience. This work would not have been possible without his help.

I would then like to express my thanks to Dr. Roberto Musedere from the University of Windsor for his willingness to serve as my external examiner and Dr. Peter Hallschmid and Dr. Jonathan Holzman for serving on the committee. I really appreciate their valuable time and constructive comments on my thesis.

I would also like to thank my friends and colleagues in School of Engineering for making my graduate life enjoyable at UBC Okanagan and providing a friendly work environment in the office. In particular, thank you to Xian Jin, Chiun-Shen Liao, Xuegui Song, Ning Wang, Junfeng Zhao, James Sun, Yeyuan Xiao, Mingbo Niu, and a short-time colleague, Carl Wong.

Special thanks are owed to my family, especially my parents, for their unwavering love and continual support throughout my years of education.

# Chapter 1

# Introduction

### 1.1 Motivation

Nowadays, as integrated circuit (IC) manufacturing technology improves into the deep submicron (DSM) regime, interconnect has been identified as one of the most critical challenges for IC designers [1]. In the past, chip performance was determined by the transistor performance. However, as the technology continues to scale down, interconnect behavior becomes indispensable in the DSM domain and will dominate the overall chip performance, reliability, and cost eventually. Accuracy in predicting the performance of a design becomes the first step in this interconnect-dominated technology [2–4].

The 2007 International Technology Roadmap for Semiconductor addresses "three dimensional (3D) control of interconnect features" among the five "interconnect difficult challenges" both for technology generation greater or equal and less than 22 nano-meters (nm), and it is the only challenge in near term (2007-2013) and distinct future (2014-2022). Contributions to dimensional variation include "line edge roughness (LER), trench depth and profile, via shape, etch bias, thinning due to cleaning, and chemical mechanical polishing (CMP) effects" [5, 6].

As the shrinking of geometric dimension and change of physical properties affect the sensitivity and increase the variability of resistance and capacitance, the accuracy of estimates of interconnect parasitics due to resistances and capacitances variability can have significant impacts on the performance and reliability in very-large-scale integration (VLSI) circuits of semiconductor technology development [7–9].

### **1.2** Research Goals

There are several key challenging problems associated with the scaling technology. One such challenge is the increasing effects of process variation. The typical variations in the interconnect geometries take account of linewidth, thickness, height, and inter-layer dielectric thickness, and these variations may lead to significant disagreement between the conceptual design and real fabricated chip [10]. These discrepancies are collectively referred to as *process variations* [11]. The management of variation is playing an important role in shrinking fundamental dimensions. The continuing increase in operating frequency is also another challenge in chip power density and within-die temperature fluctuations [12, 13].

Both devices and interconnects have become increasingly susceptible to variations during manufacturing processes with the scaled technology. In the past, designers were principally concerned with device variations, which can be captured by worst/best case corner points techniques [14, 15]. In today's VLSI products, however, process variations are not restricted to device variations. Interconnect variations become more pronounced and dominate over device variations in future technologies [16]. As a result, designers need more accurate parasitic capacitance and resistance values to minimize design margins and cost. Accuracy of capacitance sensitivity extraction is increasingly essential to account for process effects and is a challenging issue [7, 12, 17, 18].

Magic is an open source layout editor. It not only provides user friendly operations, but it is also flexible for users to modify its internal structures. As a result, the idea to implement capacitance process variation into Magic was brought up. Magic contains approximately 9,000 lines of C languages in extraction part [19], which caused the initial understanding of Magic's internal structure to be more difficult than expected. As Magic has been widely in use for lots of universities in education purpose since it was first published, it is certainly a good idea to implement more capabilities to make Magic a more sophisticated layout tool without much cost, and it would be a benefit for education purposes in the future.

In this thesis, the focus is on the improvement of capacitance extraction in Magic and the capacitance sensitivity on the linewidth process variation in interconnect. The demonstration of this method for the first time is done by extracting capacitance sensitivity to linewidth variation from layout.

The goals for this thesis are two-fold: First, CUP capacitance models, a capacitance extraction, are presented and implemented in the Magic VLSI layout tool. Second the derivative of capacitance models are computed for process variation effects on linewidth. The approach to implement CUP models is to understand Magic's internal structures and apply better formulae to calculate capacitances. To compute the derivatives, it is first necessary to find the real edge of a conductor, which leads to an invented type of edge, the "coincident edge" explained in Chapter 4. New metal search algorithms are created along with a new extraction output format.

The contributions of this thesis are summarized as follows:

- 1. Implementation of CUP models to improve Magic's capacitance extraction accuracy.

- 2. Implementation of capacitance derivatives to account for process variation sensitivity.

- 3. Comparison and evaluation of proposed algorithms.

### **1.3** Thesis Organization

This thesis is composed of six chapters. Chapter Two starts with the background of interconnect design problems in the DSM regime, and then discusses relevant work done on capacitance extraction and process variation in industrial tools. In Chapter Three, a detailed description of how Magic extracts capacitances is presented that includes a description of Magic's internal structure and behavior. Chapter Four then discusses the implementation of CUP models for capacitance and interconnect capacitance sensitivity into Magic. Real and coincident edges and pixel-based search algorithms are introduced and described. Evaluation is performed in Chapter Five, including simulations with spice tool and comparisons with a commercial capacitance extraction tool. In the end, Chapter Six concludes with the summary, suggestions, and areas for future work.

# Chapter 2

# **Background and Relevant Work**

In this chapter, background information and relevant work for this thesis are presented. The first part of this chapter emphasizes interconnect design theory. Before investigating further, a brief historical perspective is introduced. The evolution of ICs began with Small-Scale Integration (SSI) containing only a few transistors, Medium-Scale Integration (MSI) containing hundreds of transistors, Large-Scale Integration (LSI) containing tens of thousands of transistors. In the final stage, VLSI was introduced containing hundreds of thousands to several billions transistors nowadays in a single chip. VLSI technology is divided into several regimes from micron, submicron, deep submicron (DSM), and ultra-deep submicron (UDSM). This section focuses on the extraction of interconnect parasitics for high aspect ratio interconnect, typical of the DSM or UDSM regime.

### 2.1 Interconnect Design Theory

It is well known that interconnect design is becoming a more and more significant concern in DSM process technologies, and the influence of shrinking interconnect line width and height size fluctuations becomes more severe in the fabrication processes beyond 45 nm [20]. Therefore, a detailed discussion of interconnect background and design is presented in this section.

#### 2.1.1 Deep-Submicron Interconnect

In DSM technology, interconnect has numerous issues that would affect the performance of circuits. IC designers are facing more challenges, such as coupling parasitics, IR drop, and electromigration. However, one of the most widespread challenges for interconnect design is interconnect delay in a critical path [21]. Reference [22] showed an example of delay components for the 65 nm technology, in which the transistor delay component is 43%, the intra-cell resistance (coming from contact, via, diffusion, poly, and metal resistances) and the capacitance (coming from contact-to-gate, poly, metal, and via capacitances) contributes 22% of the total delay, and the inter-cell (between cells) metal and via resistance and capacitance account for 35% of the total delay. It is observed that RC components are a significant fraction and contribute approximate 57% of overall circuit delay.

In addition, optimal buffer insertion methods were used to reduce delay from quadratic to linear. However, this method becomes difficult as the number of buffers increases at a fast rate in DSM technologies [23]. As size dimensions become smaller, the primary contributor to interconnect delay is wire parasitic. The parasitics of resistance (R) and capacitance (C) are the physics properties of the wire, and the amount of resistance and capacitance is dependent on the physical dimensions of the interconnect and materials used. In next few sections, parasitic resistance and capacitance are introduced.

#### 2.1.2 Parasitic Resistance

The resistance is determined from the cross-sectional area of the interconnect. With the resistance equation given by

$$R = \rho \frac{l}{w \times t} \tag{2.1}$$

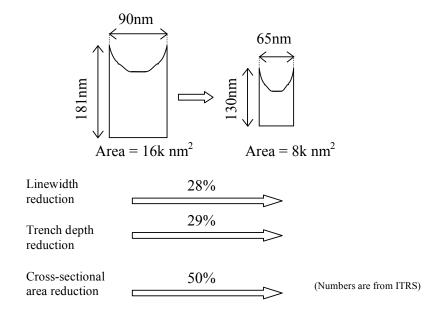

a larger cross-sectional area (width (w) by thickness (t)) means a lower resistance. The conductor resistivity  $\rho$  is in  $\Omega \cdot m$ . As the technology shrinks down to DSM, wires tend to be much thinner than before (see Figure 2.1). This fact leads to an increase in parasitic resistance for a minimum width wire. For instance, interconnect cross-sectional area is reduced by 50% from the 90 nm to the 65 nm technology node, but it results in 100% increase in resistance for a line of the same length.

Improvements have been made by replacing the materials in the interconnect system (from Al and SiO<sub>2</sub> to Cu and so-called low- $\kappa$  dielectric materials) to reduce interconnect resistances. Table 2.1 lists the resistivity for Al and Cu. This approach, however, causes serious delay as integrating new low- $\kappa$  materials is not a straightforward process [24, 25]. Moreover, this is only a one-time improvement; the resistance continues to increase dramatically in further smaller geometries. In the meantime, the simplest solution is to increase the wire width to reduce resistance. Unfortunately, this is not always possible because an increase in wiring density is needed to keep up with the increase in logic density as transistors

FIGURE 2.1: Resistance cross-sectional area reduction from 90 nm to 65 nm technology nodes [5].

are scaled.

### 2.1.3 Parasitic Capacitance

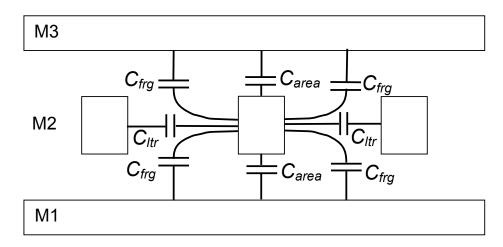

FIGURE 2.2: Capacitance configuration in a typical DSM technology with 1.5 aspect ratio.

Coupling between neighboring conductors gives rise to parasitic capacitance, and to first order the amount of capacitance is proportional to the ratio of the conductive areas facing each other but inversely proportional to the separation of two conductors. Given the charges on both conductors' plates are +Q and -Q with a V voltage between them, the equation for the capacitance is shown with integrals:

$$C = \frac{Q}{V} ; \quad Q = \int_0^V dV \cdot C(V) \tag{2.2}$$

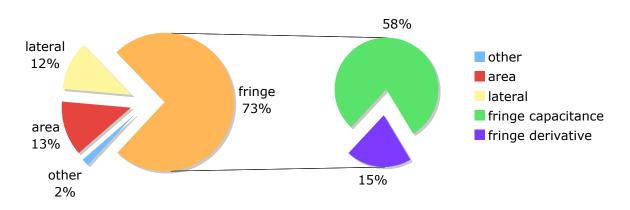

A typical structure of a DSM interconnect with the most dominant parasitic capacitances labeled is shown in Figure 2.2. Metal 2 conductors have lateral capacitance with the adjacent conductors and also have area and fringe capacitances with metal 1 and 3 conductors on the above and below. Area capacitance is caused by two different conductors overlapped, and it was the dominant element in earlier technologies. However, lateral and fringe capacitances have grown dramatically to be the major contribution to the coupling capacitance due to the narrower wires and spacing in DSM technology.

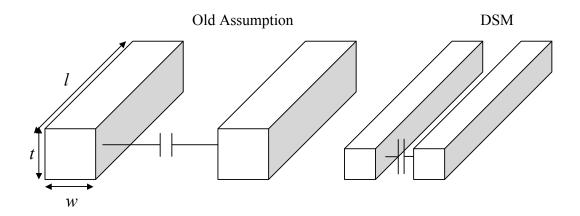

FIGURE 2.3: Capacitance in old assumption and DSM.

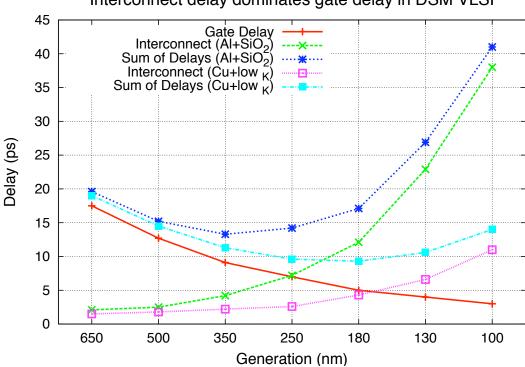

To improve performance, advanced methods, such as low- $\kappa$  dielectric insulators and air gaps, are strongly required to reduce  $\kappa$  to around 1.9 [26], but it is no longer useful in further scaling of technology down to 90 nm and below (see Figure 2.4 and Table 2.1). A comparison between interconnects and device delays by using two different materials, Al and Cu with SiO<sub>2</sub> and low- $\kappa$  from the National Technology Roadmap for Semiconductors SEMATECH [27] is made. By observing the interconnect delay for Al with SiO<sub>2</sub> and Cu with low- $\kappa$ , it is clear that the total delay for a gate with Cu and low- $\kappa$  is definitely lower than Al and SiO<sub>2</sub>, and it solves the delay problem for the 250 nm and 180 nm technology generations. However, the delay started to increase exponentially with further scaling down of the technology. Challenges develop as the delay time starts to increase parabolically beyond 130 nm.

| Aluminum (Al)    | $3.0 \ \mu\Omega/cm$     |

|------------------|--------------------------|

| Copper (Cu)      | $1.7 \ \mu\Omega/cm$     |

| SiO <sub>2</sub> | $\kappa = 4.0$           |

| Low- <i>k</i>    | $\kappa = 2.0$           |

| Al & Cu          | $0.8 \ \mu$ Thick        |

| Al & Cu Line     | $43 \ \mu \ \text{Long}$ |

TABLE 2.1: Information of Figure 2.4 (adapted from [27]).

The easiest solution for circuit designers to obtain a lower capacitance is to increase the spacing between wires, but at the cost of more area in the design. The benefits of increasing the wire spacing are limited by diminishing returns and can only be used at the cost of losing interconnect density.

Interconnect delay dominates gate delay in DSM VLSI

FIGURE 2.4: Interconnect vs gate delay (adapted from [27]).

#### 2.1.4 Inductance

Inductance is another critical parasitic effect. A severe inductive effect includes overshoots, undershoots and oscillation in signal waveform, and aggravates crosstalk and power grid noises [28, 29]. These signal integrity faults can potentially manifest themselves as glitches or worse, as false transitions at the end of wires. Inductance is the ratio of the magnetic flux  $\Phi$  generated by the electric current *i* and passing through a closed loop with N turns, and the equation is shown:

$$L = \frac{N\Phi}{i} \tag{2.3}$$

In the past, inductance was not a critical concern because RC effects dominated at low frequencies. However, the increasing inductance effect arises not only from the result of higher switching frequency, but also from other factors: resistance and capacitance reductions by Cu and low- $\kappa$  dielectric respectively, denser and smaller geometries, and growing complexity of interconnect design [30–32]. The promotional literature for one of the leading industrial tools, Synopsys Star RCXT, claims that modeling global interconnects of RC circuits is no longer adequate, and the inductance effect must be included to avoid underestimating the signal integrity problem [33].

In this thesis, inductance was neglected for a few reasons. The first reason is that it is very difficult to predict and capture on-chip inductance effect because it depends strongly on the overall construction of the integrated circuit [34]. The uncertainty of the current return path, prior to parasitic extraction and circuit model simulation, has challenged inductance modeling and analysis in the DSM era [35, 36]. Unlike capacitance, which is based strongly on neighboring features, inductive effects have a much larger spatial range. The second reason is that inductance does not cause severe signal or propagation delay of interconnects problems. It is shown that the worst-case inductance would cause an 8% reduction in the delay [28]. The third, and most significant, reason is that Magic does not include an inductance extraction system. Such a modification would have required more human resources, which is beyond the scope of the work intended for this thesis. The scope of this Master's thesis was mainly about implementing the sensitivity analysis in capacitance extraction.

### 2.2 Capacitance Extraction

In the DSM regime, interconnect behavior dominates the overall chip performance. Therefore, accurate estimates of interconnect due to resistance-capacitance are significant for predicting performance and reliability in VLSI circuits [4, 7]. There are many different approaches to capacitance extraction. In this section, a number of previous approaches are presented, and one of them is chosen for investigation and implementation in the Magic layout tool.

#### 2.2.1 Analytical Formulae

Capacitance values are estimated by analytical formulae in many cases because there is a compelling need for simple and fast approximation formulae, and these formulae are especially useful for hand calculations.

The basic capacitance calculation is the parallel plate formula given by

$$C = \epsilon \frac{A}{d} \tag{2.4}$$

where A is the area of two parallel planar conductors separated by distance d and  $\epsilon$  is the dielectric constant. As the IC technology advances, the interconnect widths become narrower than their vertical thickness, which means fringe capacitance is comparable to overlap area capacitance, and the need to model the capacitance more accurately becomes important as shown in Figure 2.2.

Two accurate formulae were proposed using approximate conformal mapping techniques in [37], and both formulae are more accurate, within 1% error, for a metal line of width greater than the dielectric thickness.

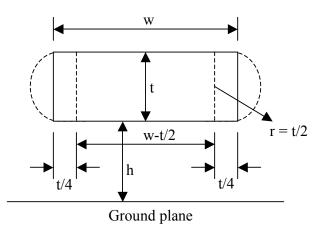

Later a simple analytical formula was presented to include a direct physical interpretation in [38]. The replacement of rectangular wire cross-section with an "oval" one is made, and the final cross-section is composed of a rectangle and two half-cylinders as shown in Figure 2.5. The formula is shown:

$$C = \epsilon \left[ \frac{w - t/2}{h} + \frac{2\pi}{\ln\left(1 + \frac{2h}{t} + \sqrt{\frac{2h}{t}\left(\frac{2h}{t} + 2\right)}\right)} \right]$$

(2.5)

It is shown that this formula is simpler and more accurate than the proposed approximation

FIGURE 2.5: Conductor with a rectangular cross-section (adapted from [38]).

in [37].

A purely empirical formula based on evaluating numerical solutions was proposed in [39], and it was later improved by extending the empirical expression and simultaneously reducing the range of validity in [40]. The formula is shown:

$$C = \epsilon \left[ \frac{w}{h} + 0.77 + 1.06 \left( \frac{w}{h} \right)^{0.25} + 1.06 \left( \frac{t}{h} \right)^{0.5} \right]$$

(2.6)

where the first term describes the parallel plate capacitor and the other three terms represent side effects.

Reference [41] includes a complete comparison of these analytical formulae, and it is shown that Meijs and Fokkema [40] is the best choice in every respect, both most accurate and fastest in runtime.

#### 2.2.2 Field Solver

Electric field solvers produce accurate results for multi-conductor systems in capacitance extraction. In [4], several reasons to use field solver for parasitic extraction were discussed: field solvers deliver accurate distributed self- and coupling capcaitances, and it handles general, non-Manhattan geometries and scales to DSM domain. Three major field solver approaches are discussed below.

#### 2.2.2.1 Random Walk Method

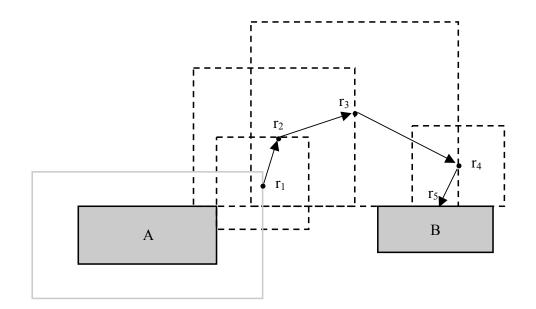

The random walk method (RWM), also known as a stochastic algorithm, used for highspeed capacitance extraction in multi-level VLSI interconnects, was introduced by LeCoz and Iverson [42, 43]. The basic idea is to present boundary-integral solutions to compute electric potential and electric field at a cube center. The capacitance  $C_{AB}$  between two electrical conductors A and B can be shown by Monte Carlo integration:

$$C_{AB} = \oint \oint \frac{d^2 r_1 \varepsilon(r_1) E(r_1)}{V_B} \tag{2.7}$$

Each random walk consists of a series of steps onto cube boundaries. Figure 2.6 shows the random walk starting on an integration surface around conductor A and terminating on a conductor B, and the estimated capacitance between both electrodes is associated with Eq. 2.7. Reference [44] addresses that the random-walk method performs with excellent computational efficiency because it requires no numerical mesh. Random walk methods have been successfully implemented in some commercial tools, such as Magma QuickCap [45] and Synopsys Raphael NXT [46].

FIGURE 2.6: Sample random walk method (adapted from [44]).

#### 2.2.2.2 Volume-Based Method

In volume-based analysis methods, Laplace's equation is solved outside the conductors (see Eq. 2.8).

$$\nabla \cdot \epsilon \nabla \Phi = 0 \tag{2.8}$$

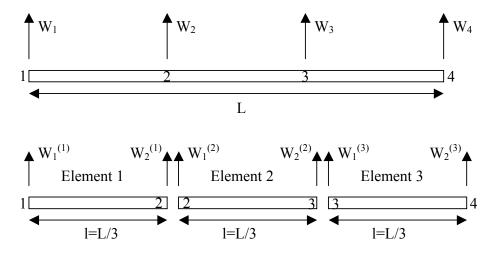

One common way to solve 3D Laplace's equation numerically is to use Finite-Difference (FD) [47, 48] or Finite-Element (FE) [49–51] Methods, in which FD's main idea is to approximate the derivatives in the equations. The basic idea in FE method is to find an approximate solution to simplifying a complicated problem. For instance, suppose a structure (beam) is given, with FE method. It is then divided into several elements in a suitable solution in each element (see Figure 2.7). Volume-based methods are computationally expensive with very

FIGURE 2.7: Sample finite element method (idealization of a beam).

large sparse matrices and require numerical techniques to improve the run time efficiency and memory storage. FD and FE methods have been used in some commercial tools, such as Ansoft Maxwell [52] and Synopsys Raphael [53].

#### 2.2.2.3 Surface-Based Method

The surface-based method, also known as Integral Equation Formulation Method, is a wellknown method in VLSI capacitance extraction, and many proposed algorithms are based on it. The following describes a set of different techniques for parasitic extraction over the past two decades, and they are all based and extended on the integral equation formulation method.

**BEM.** Boundary-Element Methods (BEM) are commonly used to perform electrostatic analysis [54], and a technique is shown in [55]. Many of the following techniques are based on BEM.

The purpose of BEM is to find the short-circuit capacitance matrix in a domain V containing M conductors (see Eq. 2.9).

$$Q = C_s \Phi \tag{2.9}$$

where Q is conductor charge  $Q^T = [Q_1, Q_2, \cdots, Q_M]$  and conductor potentials  $\Phi^T = [\Phi_1, \Phi_2, \cdots, \Phi_M]$

$$\phi(p) = \int_{V} G(p,q) \ \rho(q) \ dq, \qquad (2.10)$$

where  $\rho(q)$  is the charge distribution and G(p,q) is the Greens function for V. BEM subdivides the conductors' surfaces and approximates inverse matrix to eventually compute capacitance matrix  $C_s$ . One of the commercial tools, Space 3D, uses this method in capacitance extraction [56]. **FMM.** In 1991, a 3-D capacitance extraction program based on the multipole expansions was published: FastCap [57]. The algorithms, based on fast multipole method (FMM), accelerates the boundary-element solution with conjugate residual method for reducing order of computations and complexity. It is noticed that for problems with as few as 12 conductors the multiple accelerated boundary element method can be nearly 500 times faster than Gaussian elimination based algorithms, and five to ten times faster than the iterative method alone, depending on the required accuracy [57]. FastCap has become very practical, popular, widely used in industry and academia, and has initiated an extensive amount of research in the area of the development of fast integral equation solution techniques [58, 59].

**FFT.** Several years later, a new algorithm, "precorrected-fast Fourier transform (FFT)", was presented for accelerating the potential calculation and solving electromagnetic boundary integral equations arising in the extraction of coupling capacitances in 3-D geometries [54]. The comparison shows that for a wide variety of geometries in IC packages, the new algorithm is superior to the fast multipole algorithm used in FastCap in terms of execution time and memory use by more than an order of magnitude [54].

**SVD.** Another integral equation 3-D solver is  $IES^3$  ("ice cube"), which uses singular value decomposition (SVD) algorithm, an extremely effective tool for compression of rank-deficient matrices. The result shows that  $IES^3$  is dramatically faster than the multipole-based approaches [60].

Hierarchical. Shi and *et al.* presented a fast hierarchical algorithm for computing3-D capacitance extraction, and it is significantly faster with less memory used than the

previous famous algorithm used in FastCap. It is noticed that the this hierarchy-based algorithm is 60 times faster than FastCap and uses 1/80 of the memory used by FastCap with accuracy of 2.5%. Also, this algorithm is 5 to 150 times faster than commercial software QuickCap with the same accuracy [61, 62].

**FMM+Hierarchical.** Beattie and Pileggi combined FMM with the hierarchical refinement methods to propose solutions that use both windowing and shift-truncate bounds to get an error value for the extracted capacitances to improve the speed further, called adaptive window sizing methodology. This methodology is of use in identifying crosstalk problem zones for interconnect optimization and noise reduction [63].

**Nebula.** Nebula was presented for accurate large-scale capacitance calculations with a charge distribution that decouples charge variation from conductor geometry. This separation significantly reduces the discretization size, the time and memory requirements compared to the previous approaches, and Nebula, based on FMM, is efficient enough to compute full capacitance matrix of typical interconnect problems [64].

**QMM.** The quasi-multiple medium (QMM) method greatly reduces the central processing unit (CPU) time and memory usage of large-scale direct BEM computations by transferring the coefficient matrix into a highly sparse block matrix and iterative equation solver [58]. Later, an enhanced QMM-BEM solver for 3-D multiple-dielectric capacitance extraction was proposed to achieve much higher speed and adaptability. With two enhancements, an automatic determination of QMM cutting pair number and preconditioning technique, the results showed over 10X speed-up and memory saving over the multipole approach [65].

**FHM.** Fast hierarchical method (FHM) is an efficient acceleration algorithm for 3-D capacitance extraction. A preconditioning technique is proposed by virtue of inherent properties of hierarchical data structures, and experiments show a remarkable improvement on coverage of the iterative procedure [66].

#### 2.2.2.4 Field Solver Summary

The random-walk method is practically beneficial for suitability to rectilinear geometries, statistical-error cancellation, selective integration over Gaussian surfaces, and direct capacitance matrix evaluation [43]. The surface-based method is robust and has advantages over volume based method, including a better conditioning, smaller dimensionality, and the ability to treat arbitrary regions [60].

In general, the random walk method is the best for calculating self-capacitance for a complicated net; the surface based method is most suitable for calculating small coupling capacitances, and the volume-based method is good at dealing with multiple dielectrics.

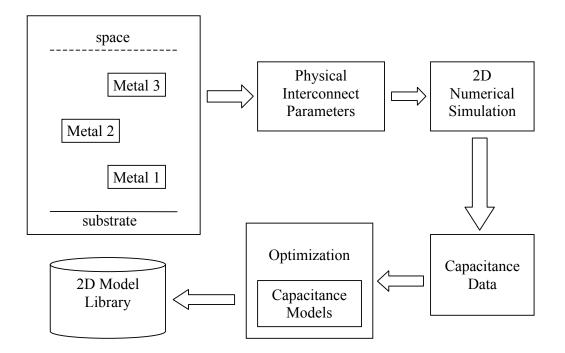

#### 2.2.3 Library Look-Up Based Method

Library look-up based method is a practical approach to estimate capacitance efficiently in layout. The analytical or the table-look-up models are automatically generated based on numerical simulations, and this method is often used to extract parasitics directly from the given mask layout in a chip and fabrication processes. A couple of techniques have been proposed in [67–69], and [67] has been chosen to be implemented in the project because Magic is a VLSI layout tool, parasitics values are obtained in the extraction. Figure 2.8 shows the block diagram of the library model procedure as implemented in this project. The details will be discussed in a later section of this chapter.

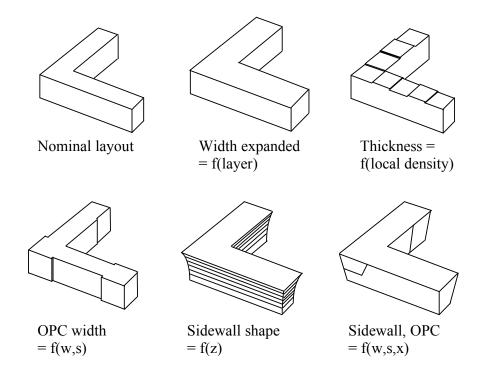

FIGURE 2.8: Overall flow of interconnect library model (adapted from [67]).

### 2.3 Commercial Parasitic Extraction

This section describes several industry parasitic extraction tools from some of the largest electronic design automation (EDA) companies, such as Synopsys, Cadence Design Systems, Mentor Graphics, Zuken, and Magma Design Automation, to demonstrate that this thesis research is important.

#### 2.3.1 Synopsys - Star-RCXT

Synopsys Star-RCXT is a standard for parasitic extraction in EDA industry. It provides a parasitic extraction solution for application-specific integrated circuit (ASIC), System-on-Chip (SoC), custom digital, analog/mixed-signal (AMS), radio-frequency (RF) and memory design. Synopsys claims that "the offered capabilities include variation-aware parasitic extraction, chemical-mechanical polishing (CMP) based and litho-aware extraction, inductance extraction, and analog mixed signal design flow" [33].

In addition, Star-RCXT could be integrated into industry standard design flows, layout verification and simulation tools easily, and its incorporated flow with Raphael NXT, a 3D field solver capacitance extractor providing silicon-accurate and coupling capacitances for circuit design, makes it an accurate extraction [33].

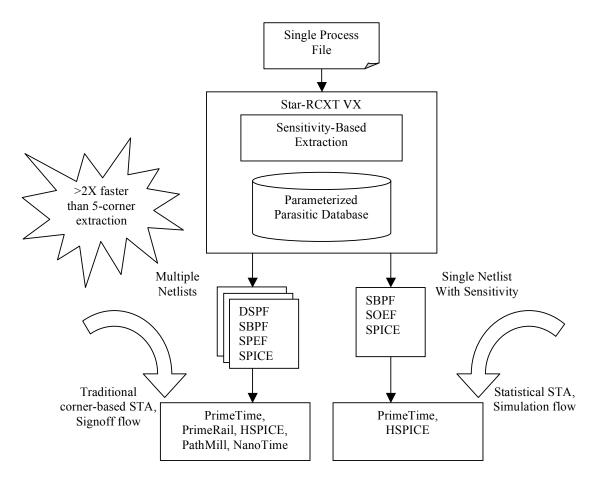

Star-RCXT uses a statistical technique to model interconnect process variation effects accurately at advanced process nodes. This solution eliminates the need to run traditional multi-corner extractions and provides multiple netlists and a single netlist with sensitivity (see Figure 2.9) to enhance the productivity and performance. The variation of each process parameter, including conductor, dielectric thickness, is available and used based on the process variations [33]. The focus is on the linewidth parameter variation in this thesis.

#### 2.3.2 Cadence QRC Extraction

As advanced process technologies become more critical, parasitic extraction becomes a key factor not only during the validation phase but also during design implementation. Cadence claims that "QRC Extraction is a 3D full-chip parasitic extractor in industry, and

FIGURE 2.9: Star-RCXT's sensitivity-based extraction solution (adapted from [33]).

the fast and accurate RLCK extraction make it an integrated extraction solution for design implementation and validation at 90 nm and below" [70].

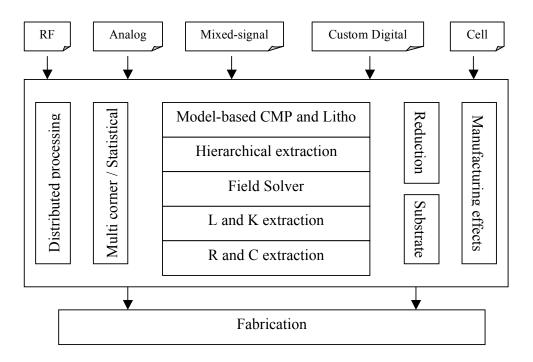

Figure 2.10 shows the key components of Cadence QRC Extraction, and multi-corner and statistical extraction are briefly discussed here. Multi-corner extraction is required to predict parasitic effects, and the number of corners and the process geometry grow inversely proportionally to each other. It extracts multi-corners at once to efficiently reduce extraction runtimes at advanced process nodes. QRC also takes random parameter variations into account to provide accurate results in statistical extraction [70].

FIGURE 2.10: Cadence QRC extraction's advanced capabilities (adapted from [70]).

## 2.3.3 Mentor Graphics - Calibre LFD

The key benefit of Mentor Graphics Litho-Friendly Design (LFD) is "the capability to capture process variations in the design flow." It captures information on process window effects in order for designers to improve the layout and make a design more robust and less sensitive to process window variations [71].

## 2.3.4 Magma - QuickCap

QuickCap NX is a 3D parasitic extractor for critical circuit analysis. As with Star-RCXT, Magma claims that "QuickCap NX is for parasitic extraction and in production use in the top 10 semiconductor companies" [72]. Magma's QuickCap NX is an accurate 3D extractor that precisely models advanced process effects. It is used in process studies with performance on accurate noise and timing analysis, proved to deliver capacitance value that are within 1 percent silicon measurements. Magma claims that "the average difference between QuickCap NX capacitance values and actual silicon measurements have been reduced from 9.79 percent to 0.11 percent by taking process effects into account" [72]. In addition, QuickCap NX's multiple techniques reduce runtime and makes it memory efficient. Figure 2.11 shows how QuickCap NX accurately models advanced process effects. This thesis concentrated on the width variation.

FIGURE 2.11: QuickCap NX's process variation solution (adapted from [72]).

#### 2.3.5 Space 3D

Space 3D is a layout-to-circuit extractor from OptEM Corporation, and it uses BEM to accurately and efficiently compute 3D interconnect capacitances of ICs based upon the layout description, which implies a lower number of discretization elements is used for 3D situations. Moreover, the implementation of a new matrix inversion technique that computes only coupling effect between "nearby" elements makes itself capable of quick extraction and memory efficiency [56].

## 2.3.6 Industry Parasitic Extraction Summary

It is noticed that parasitic extraction for process variation is the key challenge for these industry extraction tools as the real fabrication is not exactly the same as the layout in the design. Table 2.2 shows a summary of commercials tools with different types of extraction methods. FEM and RWM extractors are broadly used in industries for parasitic extraction. As a result, the research of process variation is a necessity in modern technologies.

| Commercial Tools       | Extraction Methods |              |     |                          |  |

|------------------------|--------------------|--------------|-----|--------------------------|--|

|                        | BEM                | FEM          | RWM | other                    |  |

| Synopsys-Star-RCXT     |                    |              |     | multi-corner/statistical |  |

| Synopsys-Raphael       |                    |              |     |                          |  |

| Synopsys-Raphael NXT   |                    |              |     |                          |  |

| Cadence-QRC Extraction |                    |              |     | multi-corner/statistical |  |

| Mentor-Calibre         |                    |              |     | design for manufacturing |  |

| Magma-QuickCap NX      |                    |              |     |                          |  |

| Ansoft-Maxwell         |                    | $\checkmark$ |     |                          |  |

| OptEM-Space 3D         |                    |              |     |                          |  |

TABLE 2.2: Commercial extraction methods.

## 2.4 Magic Technology Files for Look Up-Based Method

In this section, a capacitance library model procedure for Magic is presented similar to that shown in Figure 2.8. This extractor consists of a file reader, a stack file, conductor looping, 2D field solver from [73], and Techgen to read in an input data, which includes anisotropic dielectric layers and multiple types of material properties, and generate a technology file with specified sets of capacitance coefficients. The procedure is used to compute the coefficients for CUP models, which will be introduced in Chapter 4, and a comparison will be made between Magic using CUP models and Space 3D, a commercial capacitance extraction tool from OptEM Engineering Inc., in Chapter 5.

#### 2.4.1 Stack File

A stack file is composed of name, conductor, dielectric and some other sections, but only the important sections are discussed in this thesis. The name identifies the name of the stack. The conductor identifies that data about the conducting layers as follows. In each layer, layer order, layer name, minimum spacing, maximum spacing, width, thickness, and max\_dist are listed. The dielectric identifies that data about the dielectric layers, and each layer contains the information of layer order, dielectric name, corresponding conductor layer, thickness, and dielectric constant. The stack file used in this thesis and a diagram illustrating its metal configuration is provided and presented in Appendix A.

#### 2.4.2 Techgen

Techgen is the program that implements the capacitance library model procedure that reads in a Magic template technology file and generates a new one with the new model parameters. Techgen then reads in a standard Magic technology file line by line, echoes each line, and adds or modifies the capacitance model information that needs to be changed. Below is a more in-depth description of each function in techgen.

Checkdimensions: This function checks for the first word "width" or "spacing" in the technology file, and it changes the distance to agree with the stack file. A deeper explanation on width and spacing dimensions can be found in the Technology File section of Chapter 3.

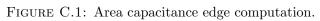

Area and Overlap: Magic's area model is specified in lines beginning with "areacap" or "overlap" in the technology file. This function checks for the first word "areacap" or "overlap". Instead of replacing the Magic capacitance model value, it *adds* a similar line that specifies CUP models.

Sidewall and Sideoverlap: Magic's lateral model is specified by in lines beginning with "sidewall" and its fringe model is specified in lines beginning with "sideoverlap". These functions are similar to Area and Overlap, and they just check the first word "sidewall" and "sideoverlap" and add another similar line that includes CUP models with parameters.

When techgen is completed, a new technology file is ready to be used in Magic, with the original Magic capacitance models and new CUP models, both of which are read by Magic. Techgen and the revisions to Magic to read the enhanced technology file were written by undergraduate students Josh Schlenker and Travis Skippon. Some minor changes and corrections have been made.

# Chapter 3

# Existing Capacitance Extraction Model of Magic

This chapter begins with a brief overview of Magic VLSI internal structures and then follows the technology file section and explanations of its extraction algorithms, which includes overlap, sidewall, and sidewall overlap coupling capacitances. After capacitance extraction, a brief explanation of extraction output is presented. Finally, a summary of the Magic VLSI layout tool is presented in the end of the chapter.

Magic is an interactive layout editing system for creating and modifying VLSI circuit layouts. Magic is not only a color painting tool, but it also provides the user with powerful operations. These include the feature of design-rule checking to avoid layout violation at any time to enhance performance [74]. In addition, Magic contains approximately 90,000 lines of code written in the C language. Magic's extractor occupies one-tenth of Magic's C code [19, 75].

## 3.1 Magic Database

As mentioned to in Chapter 1, Magic is an interactive layout editing system for large-scale MOS custom ICs. As in most layout editors, Magic layout consists of cells, and each cell contains two types of things: geometrical shapes and subcells. In this section, the principle database in Magic is illustrated.

#### 3.1.1 Geometry

Geometry is the basic database of a software, and a number of structures apart from the basic cell, plane, and tile definitions, are used frequently throughout the Magic source. Most of these basic structures have to do with geometry and can be found in the geometry header file under the Magic directory.

#### 3.1.1.1 Point

A point in 2-dimensional integer space is referred to coordinates  $p_x$  and  $p_y$ . Figure 3.1 shows the basic point structure.

#### (p\_x, p\_y)

FIGURE 3.1: Point structure.

#### 3.1.1.2 Rectangle

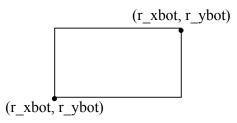

A rectangle, with area specified by lower-left and upper-right corners (points), is referred to point structures  $r_{ll}$  and  $r_{ur}$  for the lower left-hand corner and upper right-hand corner, respectively. Note that while the four coordinates of a rectangle are, as defined, r\_ll.p\_x, r\_ll.p\_y, r\_ur.p\_x, and r\_ur.p\_y, the magic source code almost always refers to these points by macro shorthand, which are r\_xbot, r\_ybot, r\_xtop, and r\_ytop respectively. Figure 3.2 illustrates the basic rectangle structure.

FIGURE 3.2: Rectangle structure.

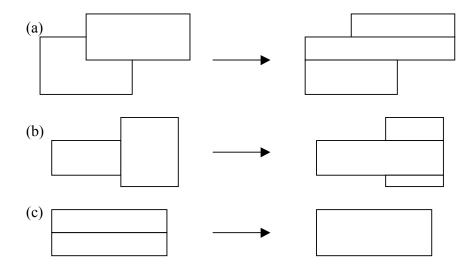

#### 3.1.2 Corner Stitched Tile

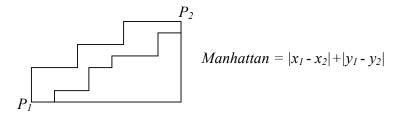

Magic uses a corner-stitched structure to present the substances of cells, that is a geometrical data structure for representing rectangular two-dimensional objects [76], or called Manhattan shapes (those whose boundaries contains only horizontal and vertical segments, see Figure 3.3) Moreover, corner-stitching structure is the reason for fast extraction speed in Magic.

FIGURE 3.3: Corner-stitching (Manhattan shape).

A tile is a basic unit in a simple rectangular shape that corresponds to a length of interconnects. Each tile has the following structure

```

typedef struct tile

```

{

```

ClientData

ti_body; /* Body of tile */

/* Left bottom corner stitch */

struct tile *ti_lb;

struct tile *ti_bl;

/* Bottom left corner stitch */

/* Top right corner stitch */

struct tile *ti_tr;

/* Right top corner stitch */

struct tile *ti_rt;

/* Lower left coordinate */

Point

ti_ll;

ClientData

/* This space for hire. Warning: the default

ti_client;

* value for this field, to which all users

* should return it when done, is MINFINITY

* instead of NULL.

*/

```

} Tile;

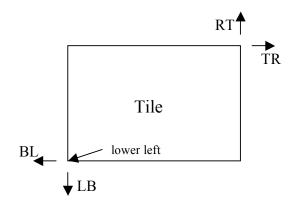

This is the fundamental data structure in Magic. ti\_body describes which layer the tile is, and \*ti\_lb, \*ti\_bl, \*ti\_tr, and \*ti\_rt represent different corner stitched tiles respectively. Ti\_ll is the lower left coordinate, so the position of the any specific tile is recognized. The following figure illustrates the tile structures in details. The corner-stitched image connects each tile to four sides of its neighbors.

The heavily used macros on (Tile \*)tiles in Magic are listed below.

- TOP(tile)

- BOTTOM(tile)

- LEFT(tile)

FIGURE 3.4: Basic tile structure.

- RIGHT(tile)

- RT(tile)

- LB(tile)

- BL(tile)

- TR(tile)

The first four macros return a position in Magic's internal coordinates, and the last four macros return a pointer to the appropriate neighboring tile (see Figure 3.4). This use has made the programmer easier to implement and reduce the confusion of tile definition.

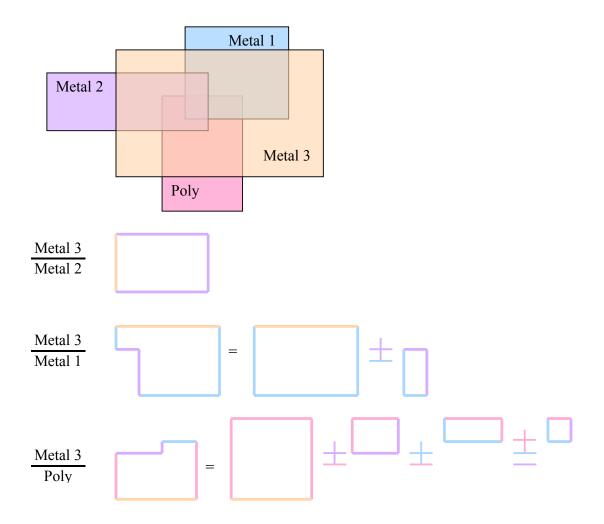

#### 3.1.3 Plane

In Magic, all geometries are split into partially independent planes. In general, these planes correspond roughly to the mask layers from which an IC is built. Typically, one defines a new plane for each set of layer types that are largely non-interacting with other types. This works especially well for metal routing layers, since the metal layers are completely non-interacting (excluding capacitance extraction, which is separate from the database representation), and only interact where cuts (vias) are defined. This works much less well for layers close to the original wafer surface. Polysilicon, diffusion regions, and wells are all heavily interacting, and therefore tend to work best when they are defined all on a single plane.

Even though it would be possible to define everything in the layout on one plane, the corner-stitched tile structures are broken up into pieces for the types overlap in the same plane. For instance, if type1 and type2 are overlapped in a single plane, Magic requires separate types type1, type2, and an additional type type1-plus-type2, and the corner-stitched structures will be subdivided until each tile can be represented by one of these three types. This is highly effective in some cases when, for example, type1 is n-diffusion, type2 is polysilicon, and thus type1-plus-type2 works out "naturally" to be layer type n-transistor.

The plane structure holds a corner-stitched tile representation and looks like:

#### typedef struct

{

| Tile | <pre>*pl_left;</pre> | /* | Left pseudo-tile */             |

|------|----------------------|----|---------------------------------|

| Tile | <pre>*pl_top;</pre>  | /* | Top pseudo-tile */              |

| Tile | *pl_right;           | /* | Right pseudo-tile */            |

| Tile | *pl_bottom;          | /* | Bottom pseudo-tile */           |

| Tile | *pl_hint;            | /* | Pointer to a "hint" at which to |

|      |                      | *  | begin searching.                |

|      |                      | *, | /                               |

#### } Plane;

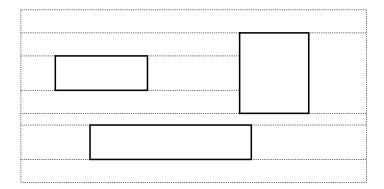

Each cell contains several corner-stitched planed to represent the cell's geometries and subcells, and each plane consists of rectangular tiles of different types. There are three important properties in a corner-stitched plane: coverage, strips, and stitches.

#### 3.1.3.1 Coverage

Every point in a corner-stitched plane is contained in exactly one tile. Empty space is represented, as well as the area covered with material.

FIGURE 3.5: Coverage tile.

In the case shown in Figure 3.5, there are three solid tiles and space tiles (dotted lines) cover the rest of the plane. The space tiles on the sides extend to infinity. In general, a plane can contain many different types of tiles.

#### 3.1.3.2 Strips

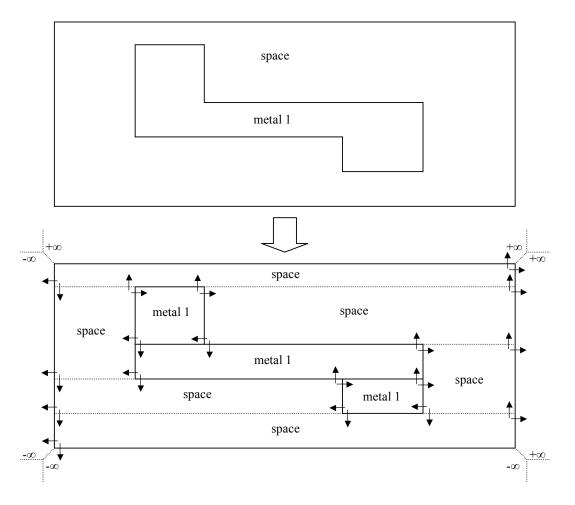

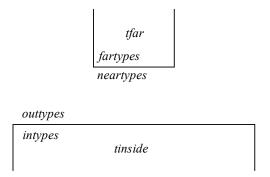

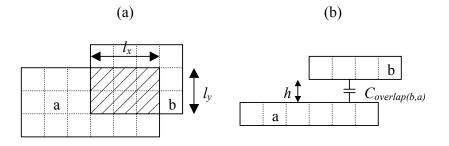

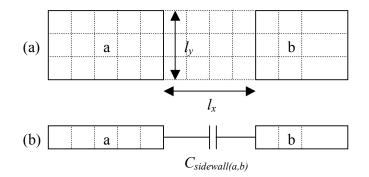

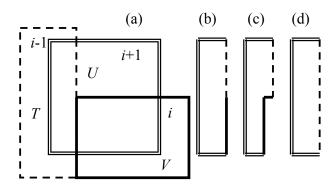

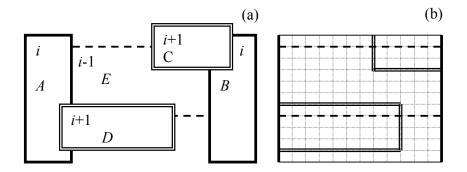

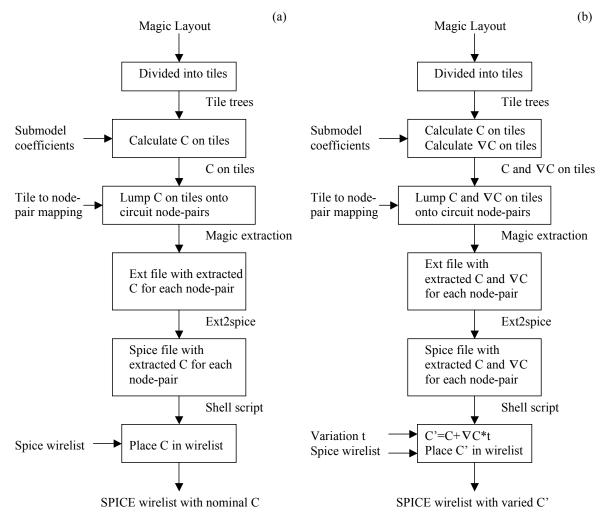

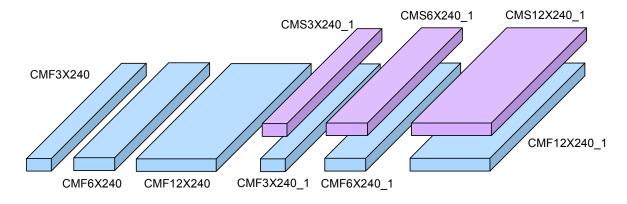

Horizontal strips represent material of the same type. The strip structure provides a canonical form for the database and prevents it from fracturing into a number of small tiles.