## ULTRA-PRECISE ON-AXIS ENCODER SELF-CALIBRATION FOR FAST ROTARY PLATFORMS

by

Darya Amin-Shahidi

B.A.Sc., University of British Columbia, 2006

## A THESIS SUBMITTED IN PARTIAL FULFILMENT OF THE REQUIREMENTS FOR THE DEGREE OF

## MASTER OF APPLIED SCIENCE

in

The Faculty of Graduate Studies

(Mechanical Engineering)

The University of British Columbia (Vancouver)

April 2009

© Darya Amin-Shahidi, 2009

## Abstract

This thesis presents the design, implementation, and experimental testing of a rotary platform and its use for encoder calibration research. So far, the experimental results have demonstrated a calibration repeatability of better than 200 nano-radians (0.04 arc-second), which is much better than the state of the art precision angular encoder error of about 1 arc-second. The major contributions of this thesis include achieving ultra-accurate encoder calibration results as well as the design of an ultra-precise rotary table and a set of high-speed electronics.

Others have developed many encoder calibration techniques. This thesis aims to identify, improve, and experimentally demonstrate the accuracy limit of an encoder self-calibration method developed at UBC. The work can be categorized into the following three parts:

1) Ultra Precise Rotary Platform Design, Manufacturing, and Assembly:

A precision rotary platform was designed for encoder calibration and other spindle metrology research. The rotary platform uses a precision airbearing. Two different rotary encoders are included for rotation measurement. Three displacement probes monitor the motion of a target ball to identify and compensate for rotor vibrations. The platform is driven by an ultra-low cogging torque motor for minimum velocity ripple. The setup's versatility makes it an excellent spindle metrology research tool.

#### 2) High-Speed Electronics for Signal Processing:

Fast processing is required for encoder calibration and precise stage control. Since no commercial controller met our fast signal detection and processing requirements, a set of electronics was designed: an FPGA-based high-speed digital controller (Avalanche) and a precision analog processing board (NanoRAD). Avalanche incorporates a fast-Virtex4 FPGA chip, a novel 1.2-GHz timer, five fast ADCs, four fast DACs, Gigabit Ethernet, High-Speed USB, and DDR RAM. NanoRAD incorporates fast comparators and precision buffers for analog processing and filtering.

#### 3) Self-Calibration Algorithm Development and Experiments:

After integration of the electronics with the mechanical assembly, the encoder calibration technique was examined. The method was adapted for the new setup, the damping estimation portion of the algorithm was improved, and the whole method was tested experimentally and in simulation. The encoder accuracy has been experimentally enhanced by 25-times from 5,000 (1 arc-second) to 200 (0.04 arc-second) nano-radians.

# **Table of Contents**

| <b>Table of Co</b> | ntents                                                            | . iii |

|--------------------|-------------------------------------------------------------------|-------|

| List of Tabl       | es                                                                | . vi  |

| List of Figure     | res                                                               | vii   |

| Acknowledg         | gements                                                           | . xi  |

| CHAPTER            | 1                                                                 | 1     |

| 1.1 Hig            | h Accuracy Angular Encoder Applications in Semiconductor Industry | 2     |

|                    | or Art Rotary Metrology Calibration Methods                       |       |

| 1.2.1              | Comparison Calibration Methods                                    |       |

| 1.2.2              | Cross-Calibration Methods                                         | 8     |

| 1.2.3              | Direct Calibration Methods                                        | 9     |

| 1.2.4              | Temporal Calibration Methods                                      | 10    |

| 1.3 The            | esis Overview                                                     | 13    |

| 1.3.1              | Precise Rotary Table Design                                       | 13    |

| 1.3.2              | High-Speed Electronic Design                                      | 15    |

| 1.3.3              | Encoder Calibration                                               | 16    |

| CHAPTER            | 2                                                                 | 17    |

| 2.1 Des            | sign Objective                                                    | 17    |

| 2.1 Con            | 1figurations                                                      | 19    |

| 2.1.1              | Two-Encoder Mode                                                  |       |

| 2.1.2              | Encoder and 3D Displacement Sensor Mode                           | 23    |

| 2.1.3              | Horizontal Mounting Mode                                          | 24    |

|                    | coders Assembly                                                   |       |

| 2.2.1              | Encoder without Integral Bearing                                  | 26    |

| 2.2.2              | Encoder with Integral Bearing                                     | 32    |

| 2.3 Bal            | I-Probe Assembly                                                  | 34    |

| 2.3.1              | Capacitive Probes                                                 | 35    |

| 2.3.2              | Precision Target Ball                                             |       |

|                    | tor Assembly                                                      |       |

|                    | nmary                                                             |       |

|                    | 3                                                                 |       |

|                    | sign Objective                                                    | 48    |

|                    | Time Resolution Requirement                                       |       |

| 3.1.2              | Voltage Precision Requirement                                     |       |

| 3.1.3              | Data Acquisition Speed                                            |       |

| 3.1.4              | Algorithm Execution Speed                                         |       |

| 3.1.5              | Communication Data Rate                                           |       |

|                    | hitecture Design                                                  |       |

| 3.2.1              | Motherboard Architecture Design                                   |       |

| 3.2.2              | Daughterboard Architecture Design                                 |       |

| 3.2.3              | Powerboard Architecture Design                                    |       |

|                    | therboard Detailed Design                                         |       |

| 3.3.1              | Virtex4-fx12 FPGA Component                                       | 58    |

| 3.3.2                | FPGA Configuration Loading System            | 66  |  |  |  |

|----------------------|----------------------------------------------|-----|--|--|--|

| 3.3.3 DDR RAM Module |                                              |     |  |  |  |

| 3.3.4                | Analog-to-Digital Converter                  | 75  |  |  |  |

| 3.3.5                | Digital to Analog Converter                  | 81  |  |  |  |

| 3.3.6                | Gigabit Ethernet Communication               | 84  |  |  |  |

| 3.3.7                | High-Speed Universal Serial Bus              | 85  |  |  |  |

| 3.3.8                | RS232 Serial Bus                             | 86  |  |  |  |

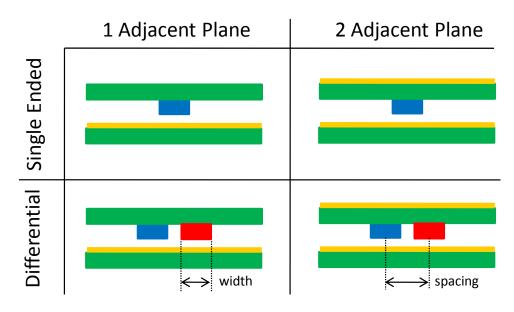

| 3.3.9                | Printed Circuit Board Design                 | 86  |  |  |  |

| 3.4 Dau              | Ighterboard Detailed Design                  | 93  |  |  |  |

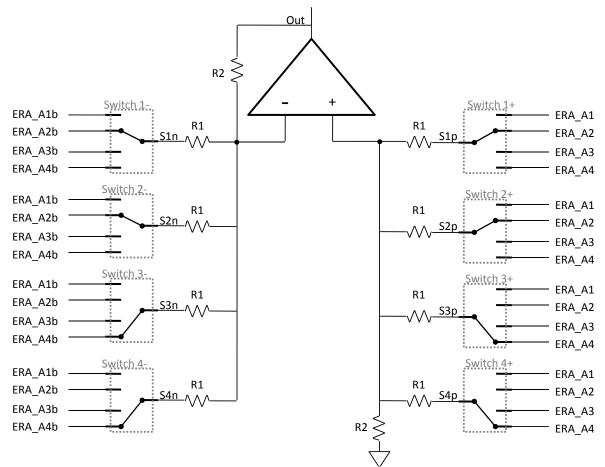

| 3.4.1                | Universal Buffers                            | 94  |  |  |  |

| 3.4.2                | High-Speed Comparators                       | 98  |  |  |  |

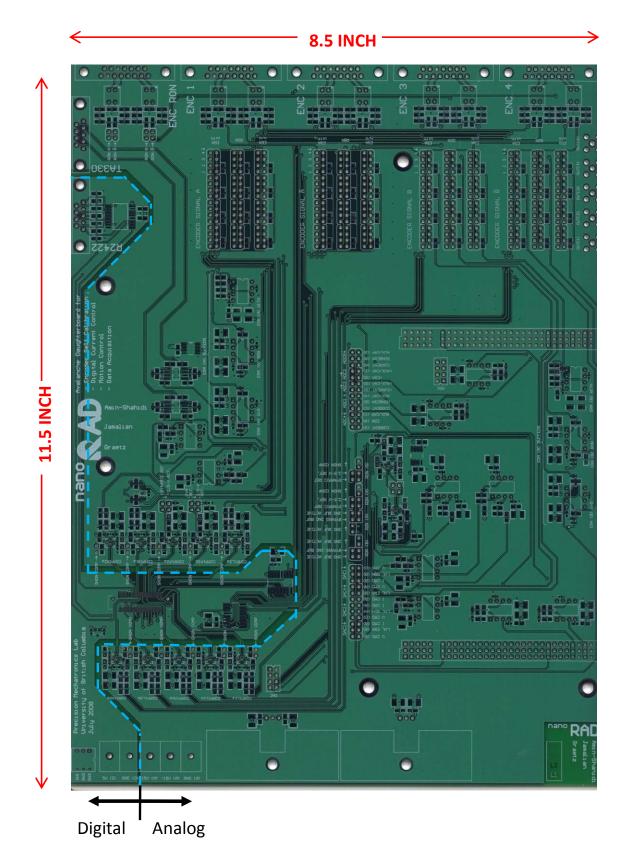

| 3.4.3                | Printed Circuit Board Design                 | 100 |  |  |  |

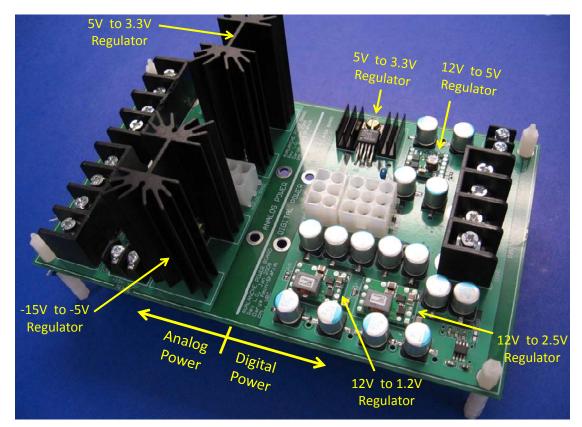

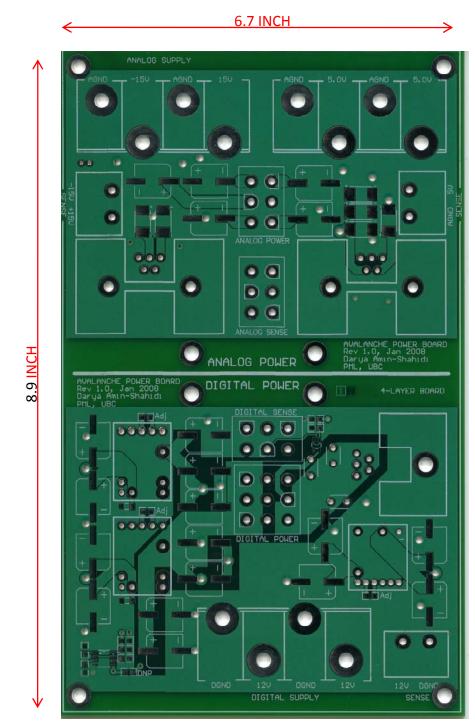

| 3.5 Pov              | verboard Detailed Design                     | 103 |  |  |  |

| 3.5.1                | Linear Regulators' Design Consideration      | 105 |  |  |  |

| 3.5.2                | Switching Regulators' Design Considerations  | 108 |  |  |  |

| 3.5.3                | Printed Circuit Board Design:                |     |  |  |  |

| 3.6 Sof              | tware Design                                 | 112 |  |  |  |

| 3.7 Mu               | lti-Phase Timer Design                       | 116 |  |  |  |

| 3.7.1                | Multi-Phase Timer Design                     |     |  |  |  |

| 3.7.2                | Performance Test and Calibration             | 118 |  |  |  |

| 3.7.3                | Experimental Results                         | 119 |  |  |  |

| 3.8 Sun              | nmary                                        | 121 |  |  |  |

|                      | 4                                            |     |  |  |  |

| 4.1 Cal              | ibration Algorithm                           |     |  |  |  |

| 4.1.1                | Original Algorithm – Second Order Method [1] |     |  |  |  |

| 4.1.2                | Modified Calibration Algorithm               |     |  |  |  |

|                      | certainty Analysis                           |     |  |  |  |

| 4.2.1                | Time Discretization                          |     |  |  |  |

| 4.2.2                | Encoder Signal Noise                         |     |  |  |  |

| 4.2.3                | Spindle Radial Error Motion                  |     |  |  |  |

| 4.2.4                | Stator Vibrations                            |     |  |  |  |

| 4.2.5                | Spindle Dynamics                             |     |  |  |  |

| -                    | ar Encoder Selection                         |     |  |  |  |

| 4.3.1                | Encoder Types                                |     |  |  |  |

| 4.3.2                | Overview of High-Precision Optical Encoders  |     |  |  |  |

| 4.3.3                | Guide Lines for Encoder Sizing               |     |  |  |  |

| 4.3.4                | Selected Encoders                            |     |  |  |  |

|                      | ulation Work                                 |     |  |  |  |

| 4.4.1                | Simulation Method.                           |     |  |  |  |

| 4.4.2                | Second Order Method in Simulation            |     |  |  |  |

| 4.4.3                | Second Order Integral Method in Simulation   |     |  |  |  |

| 1                    | perimental Work                              |     |  |  |  |

| 4.5.1                | Experimental Setup                           |     |  |  |  |

| 4.5.2                | Uncertainty from Time Discretization         |     |  |  |  |

| 4.5.3                | Uncertainty from Signal Noise                |     |  |  |  |

| 4.5.4                | Uncertainty from Vibrations                  | 178 |  |  |  |

| 4.5.5   | Uncertainty from Pressure Fluctuations        |  |

|---------|-----------------------------------------------|--|

| 4.5.6   | Experimental Results                          |  |

| 4.6 Su  | ımmary                                        |  |

| СНАРТЕЕ | 8 5                                           |  |

| 5.1 Co  | onclusion                                     |  |

| 5.2 Fu  | ture Work                                     |  |

| 5.2.1   | Understanding the Discrepancies at Low Speeds |  |

| 5.2.2   | Reducing Experimental Uncertainties           |  |

| 5.2.3   | Multiple Read-Head Configuration              |  |

| REFEREN | ICES                                          |  |

# **List of Tables**

| Table 1-1: ITRS roadmap for expected reduction in DRAM 1/2 pitch size and cost/bit [           | 3] 3 |

|------------------------------------------------------------------------------------------------|------|

| Table 2-1: Specifications for Professional Instrument's 10R Block-Head <sup>®</sup> airbearing |      |

| with 150-psi operating pressure [16]                                                           | . 19 |

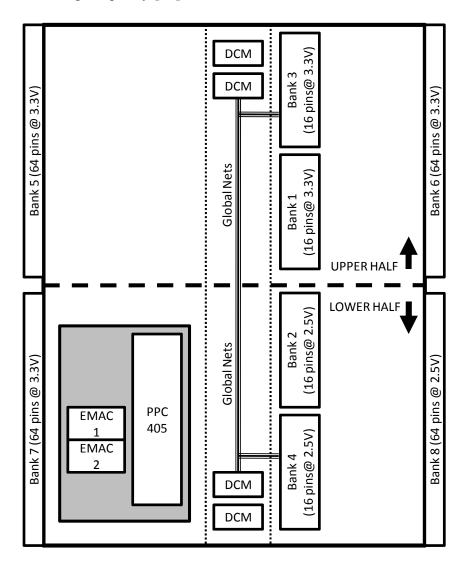

| Table 3-1: Virtex-4 FX12 FPGA main resources                                                   | . 58 |

| Table 3-2: Virtex4-fx12 pin assignment summary                                                 | . 62 |

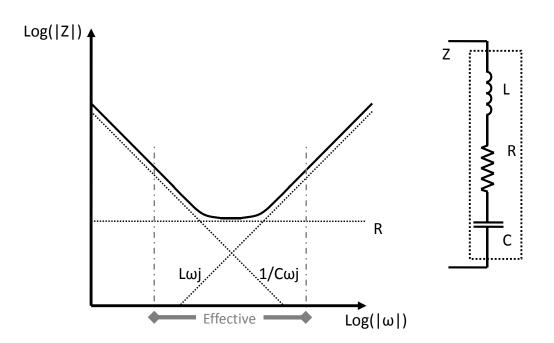

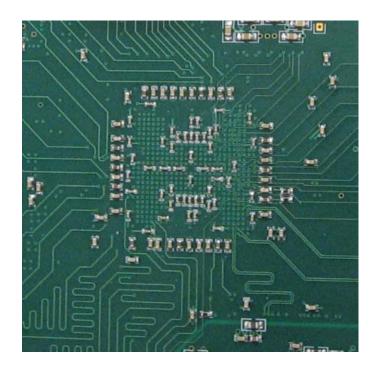

| Table 3-3: Supply decoupling capacitor selection rule [22]                                     | . 65 |

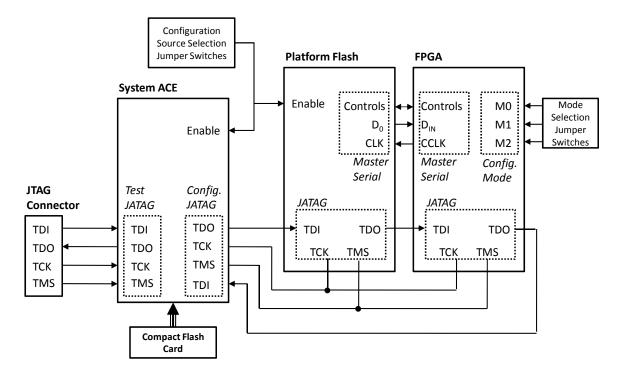

| Table 3-4: Virtex4 configuration interfaces [21]                                               | . 67 |

| Table 3-5: Trace design for 50- $\Omega$ impedance matching with 0.005" layer spacing          | . 89 |

| Table 3-6: Summary of motherboard power requirement and power supply solution                  | 104  |

| Table 4-1: Overview of high-precision optical encoder products                                 | 155  |

| Table 4-2: A summary and comparison of the natural vibration frequencies of the gran           | iite |

| table obtained experimentally and analytically                                                 | 182  |

|                                                                                                |      |

# **List of Figures**

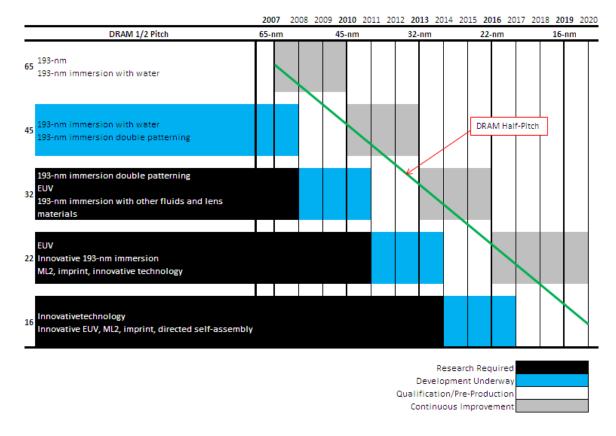

| Figure 1-1: Potential semiconductor manufacturing solutions at each stage of ITRS roadmap [4] | 5    |

|-----------------------------------------------------------------------------------------------|------|

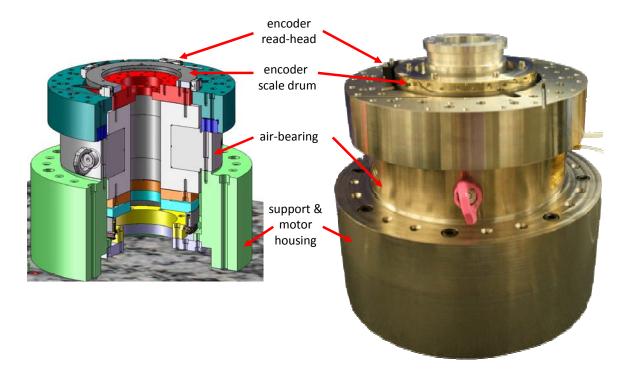

| Figure 1-2: Ultra precise rotary table designed for spindle metrology and control resea       | rch  |

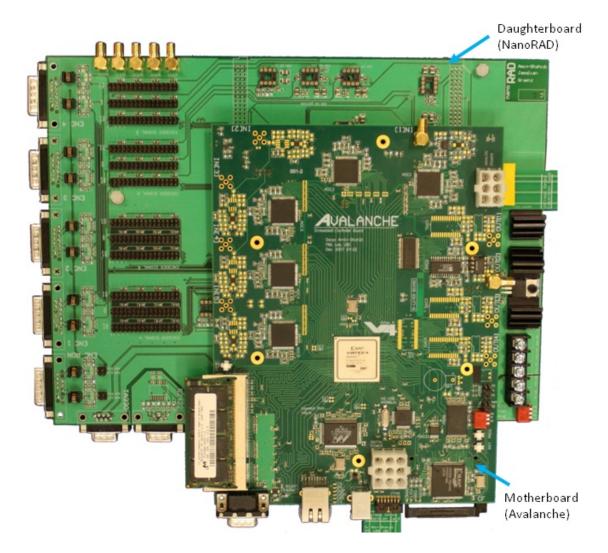

| Figure 1-3: Ultra-fast motherboard (Avalanche) and daughterboard (NanoRAD) stack-             |      |

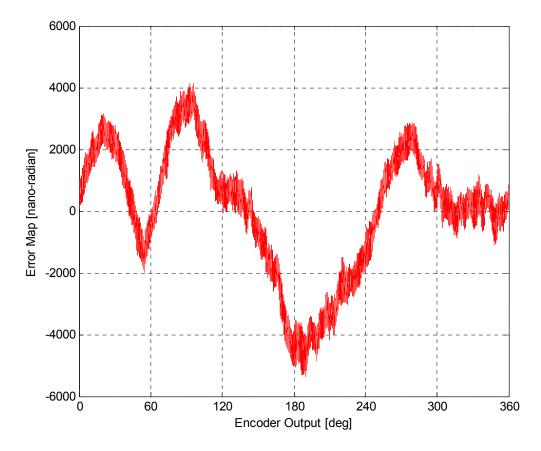

| Figure 1-4: Error map obtained experimentally at 220 RPM Using a 200MHz Timer for             |      |

| the Heidenhain ERA4282C (serial# 23-502-234) encoder used in our rotary table desig           |      |

|                                                                                               | . 16 |

| Figure 2-1: Schematic view of mechanical configuration design - sensors on two sides          | . 21 |

| Figure 2-2: Schematic view of mechanical configuration design - sensors on top                | . 21 |

| Figure 2-3: Cross-section view of the two-encoder operating mode                              | . 22 |

| Figure 2-4: Cross-section view of the encoder and 3D displacement sensor mode                 | . 23 |

| Figure 2-5: Cross-section view of the horizontal mounting mode                                | . 24 |

| Figure 2-6: ERA4282C encoder from Heidenhain [courtesy of Heidenhain] [17]                    |      |

| Figure 2-7: ERA4282C read heads arrangement in the PRT design                                 |      |

| Figure 2-8: Section-view of the ERA4282C encoder's mounting onto the airbearing               | . 27 |

| Figure 2-9: Section-view of the encoder drum adjustment mechanism                             | . 28 |

| Figure 2-10: ERA4282C read-head                                                               |      |

| Figure 2-11: Radial adjustment of the read-head for the ERA4282C encoder [17]                 | . 29 |

| Figure 2-12: Tangential adjustment of the read-head for the ERA4282C encoder –                |      |

| flexural bearing method                                                                       |      |

| Figure 2-13: Tangential adjustment of the read-head for the ERA4282C encoder - rigi           |      |

| removable fixture method                                                                      |      |

| Figure 2-14: RON905 encoder from Heidenhain [courtesy of Heidenhain] [17]                     |      |

| Figure 2-15: Section-view showing the mounting of RON605                                      |      |

| Figure 2-16: Section-view showing the fits used for centering the RON905 encoder              |      |

| Figure 2-17: Section-view of the ball-probe setup                                             |      |

| Figure 2-18: Vertical (top) and horizontal (bottom) Lion Precision capacitive probes          |      |

| Figure 2-19: Section view showing the probe alignment mechanisms                              |      |

| Figure 2-20: Section-view showing the centering mechanism for the target ball                 |      |

| Figure 2-21: Section-view of the TG8263 brushless motor                                       |      |

| Figure 2-22: Section-view showing the mounting of the TG8263 motor                            |      |

| Figure 2-23: Section view showing initial centering of motor parts                            |      |

| Figure 3-1: High-speed electronics – motherboard attached onto the daughterboard              |      |

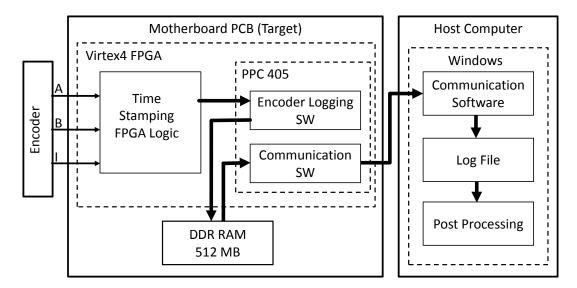

| Figure 3-2: The overall layout of custom electronics                                          |      |

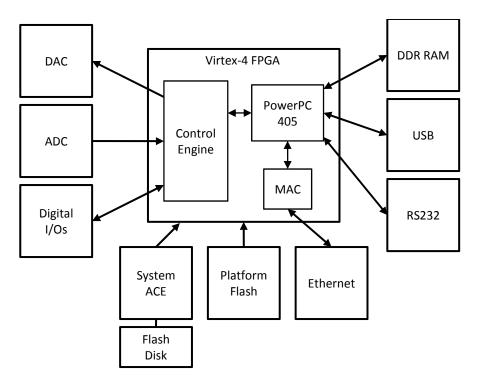

| Figure 3-3: Motherboard architecture design                                                   |      |

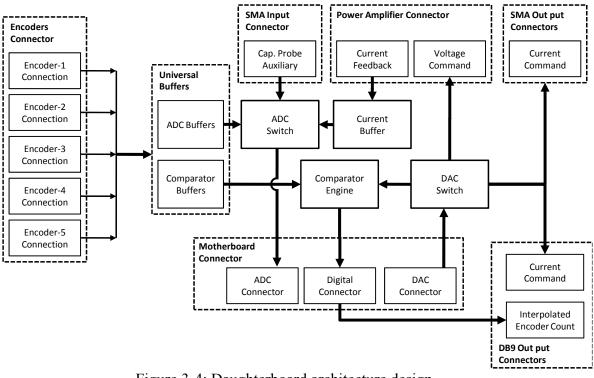

| Figure 3-4: Daughterboard architecture design                                                 |      |

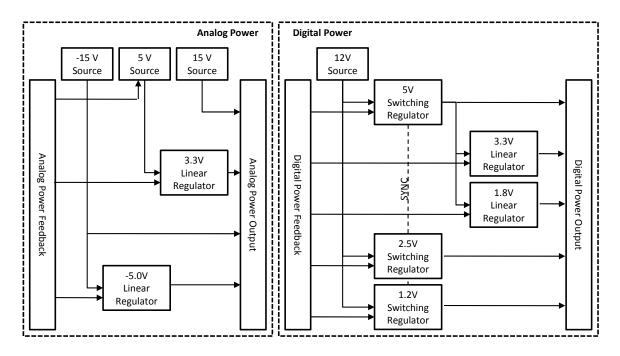

| Figure 3-5: Powerboard architecture design                                                    |      |

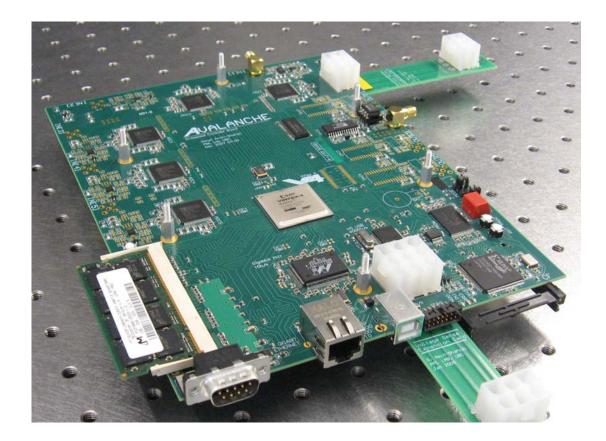

| Figure 3-6: The <i>Avalanche</i> motherboard                                                  |      |

| Figure 3-7: Simplified representation of the Virtex4-fx12 chip's architecture                 |      |

| Figure 3-8: Impedance model of a non-ideal capacitor                                          | . 64 |

| Figure 3-9: Picture of the FPGA decoupling capacitors soldered directly on the back of     |    |

|--------------------------------------------------------------------------------------------|----|

| the FPGA chip. For scale, the spacing between the dots is 1mm.                             | 65 |

| Figure 3-10: Schematic representation of Avalanche's FPGA configuration solution           | 68 |

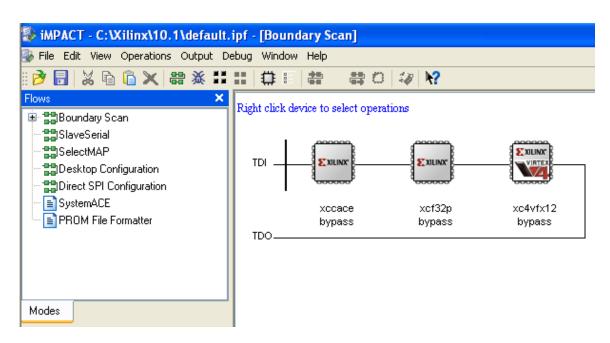

| Figure 3-11: Avalanche board's JTAG chain detected by iMPACT, Xilinx ISE software          |    |

| programming interface                                                                      |    |

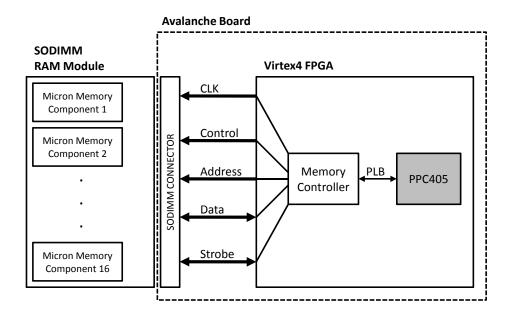

| Figure 3-12: Schematic representation of the DDR connection                                |    |

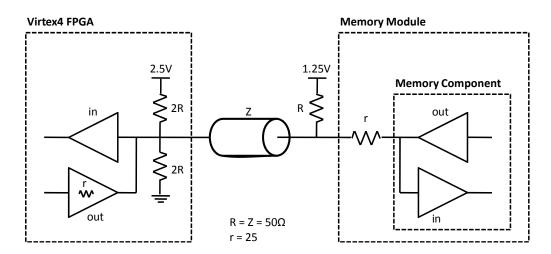

| Figure 3-13: FPGA to DDR bi-directional signal termination design                          |    |

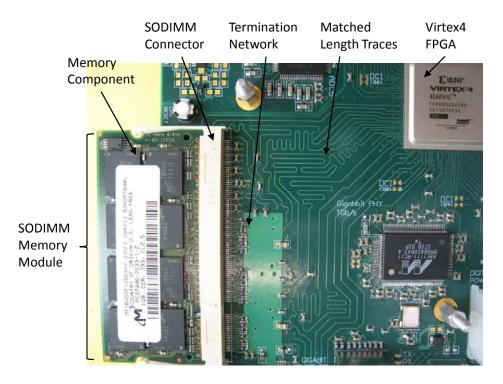

| Figure 3-14: Avalanche board's DDR memory module solution                                  |    |

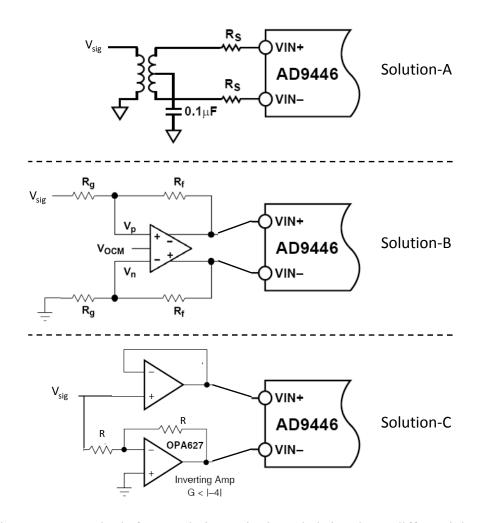

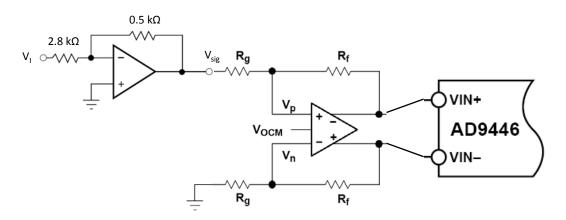

| Figure 3-15: Methods for translating a single ended signal to a differential pair          |    |

| Figure 3-16: Schematic representation view of the ADC input buffer                         |    |

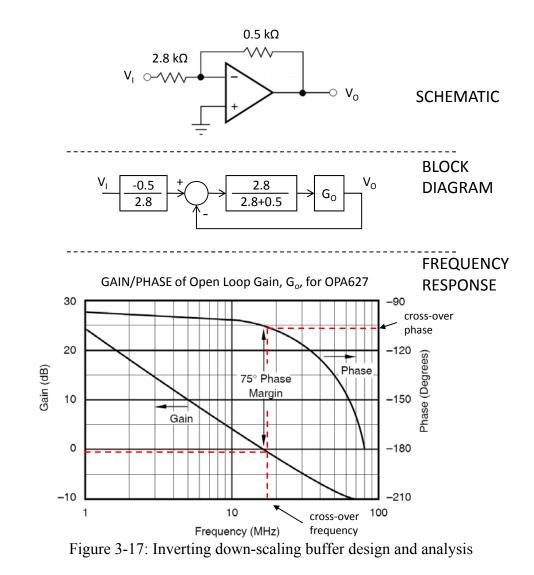

| Figure 3-17: Inverting down-scaling buffer design and analysis                             |    |

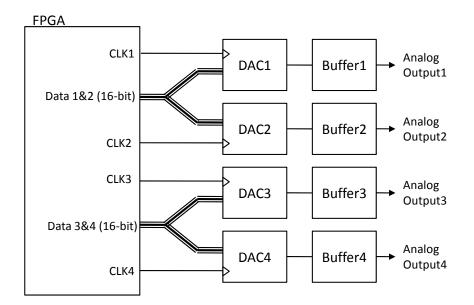

| Figure 3-18: Avalanche's analog output stage                                               |    |

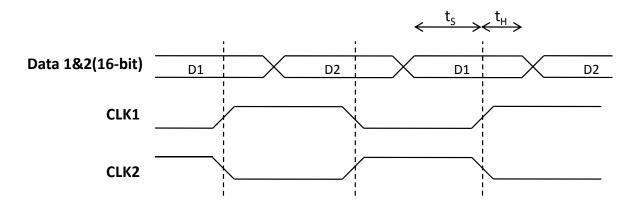

| Figure 3-19: Data and clock timing for the DAC1 and DAC2 pair                              | 83 |

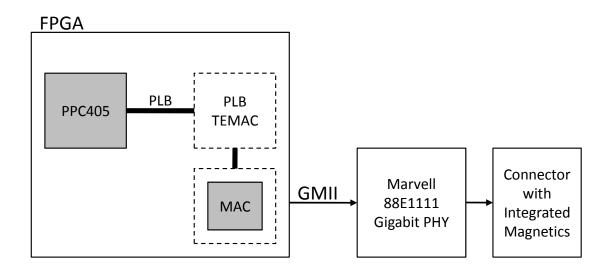

| Figure 3-20: Avalanche board's Ethernet communication media design                         |    |

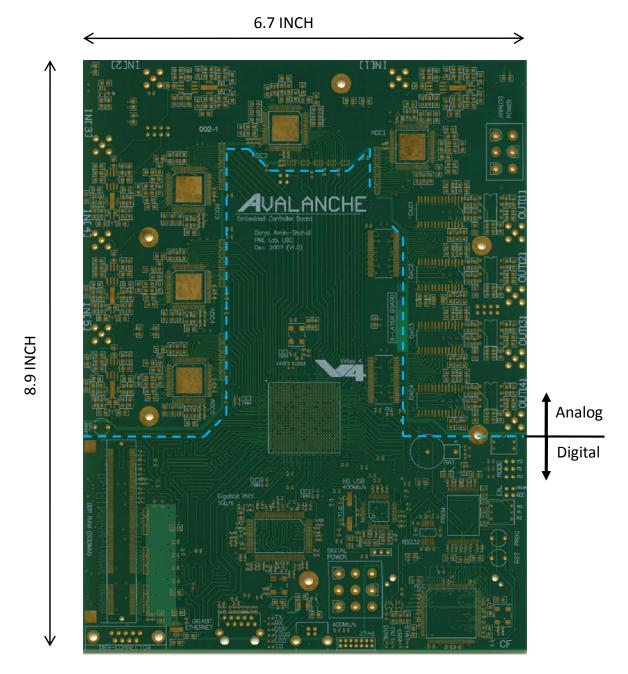

| Figure 3-21: Top view of the motherboard's printed circuit board (PCB)                     | 87 |

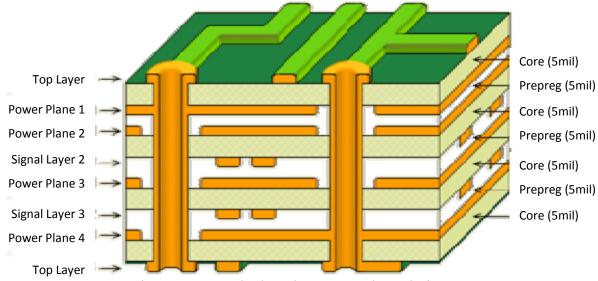

| Figure 3-22: motherboard's PCB stack-up design                                             | 88 |

| Figure 3-23: Schematic representation of the four signaling standards                      |    |

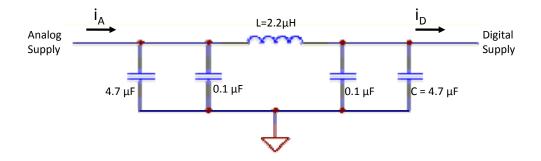

| Figure 3-24: Isolating the analog power plane from the ADC digital power pin               |    |

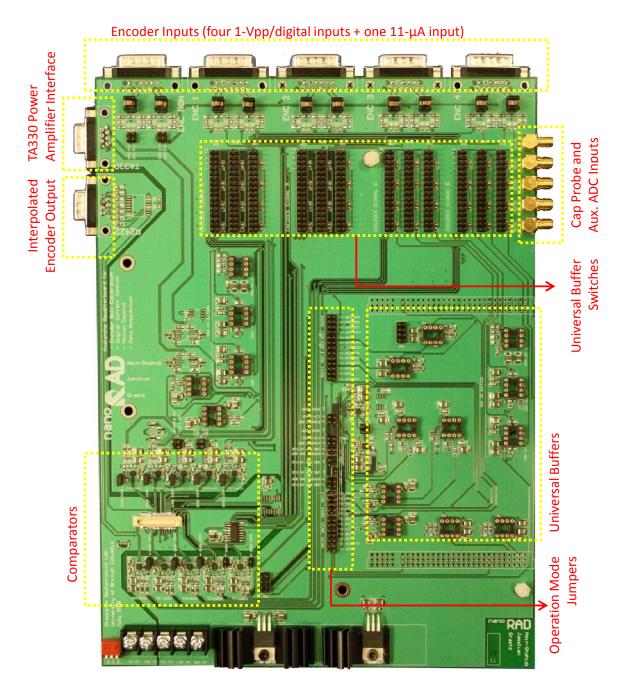

| Figure 3-25: NanoRAD daughterboard design                                                  | 94 |

| Figure 3-26: Universal buffer schematic design                                             |    |

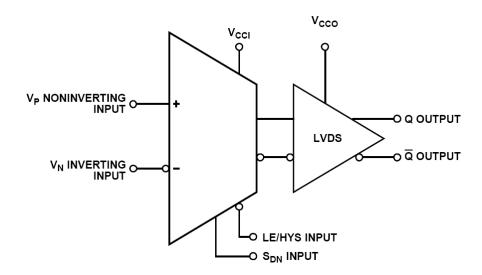

| Figure 3-27: ADCMP605 comparator's functional block diagram                                |    |

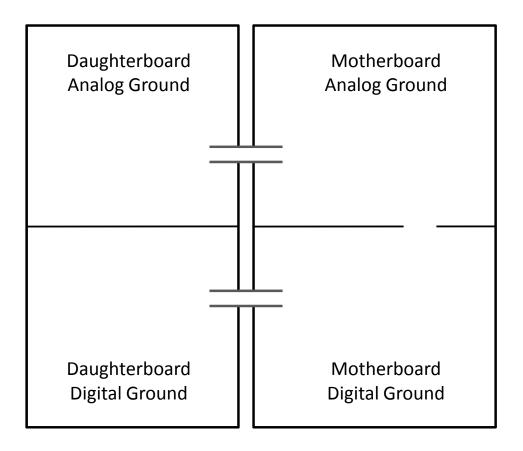

| Figure 3-28: Schematic representation of motherboard-daughterboard ground plane            |    |

| partitioning                                                                               | 01 |

| Figure 3-29: Daughterboard's printed circuit board (PCB) showing the ground partition      |    |

|                                                                                            |    |

| Figure 3-30: Powerboard used as the motherboard's power supply                             | 03 |

| Figure 3-31: Power regulation network implemented on powerboard 10                         | 04 |

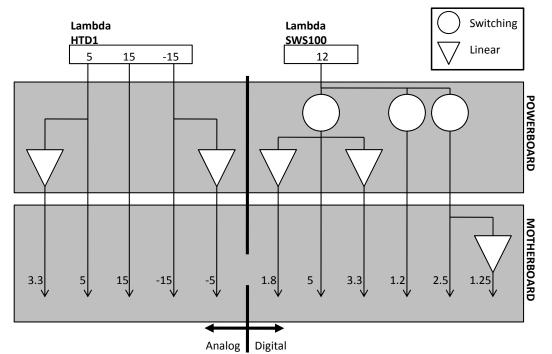

| Figure 3-32: Lumped parameter heat transfer model for linear regulator                     | 05 |

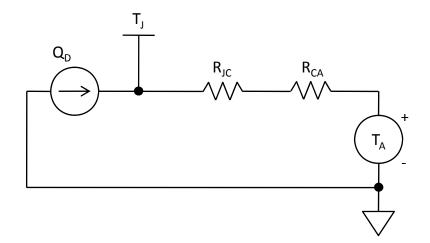

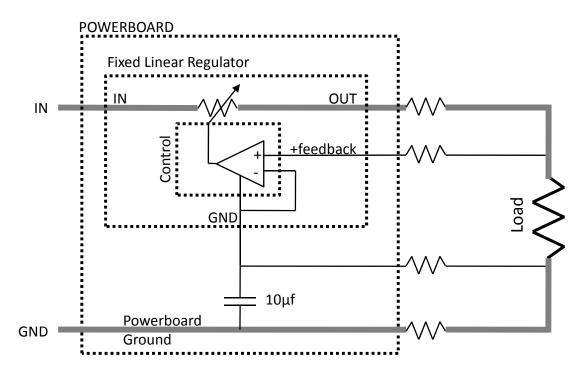

| Figure 3-33: Linear regulator's feedback design 10                                         |    |

| Figure 3-34: Power-up sequence of 1.2-V, 2.5-V, 3.3-V, and 5-V digital supplies 11         | 10 |

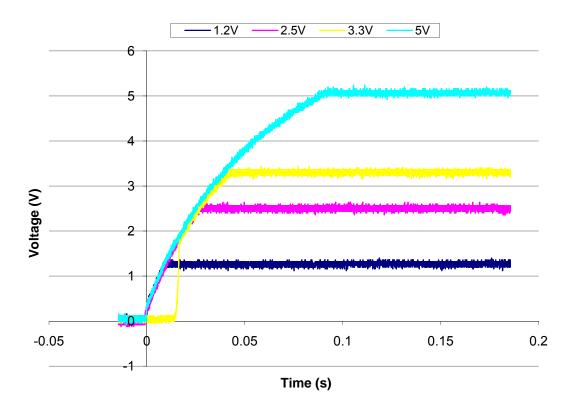

| Figure 3-35: Top view of the powerboard's manufactured printed circuit board (PCB) 11      | 11 |

| Figure 3-36: Software architecture for encoder calibration                                 | 12 |

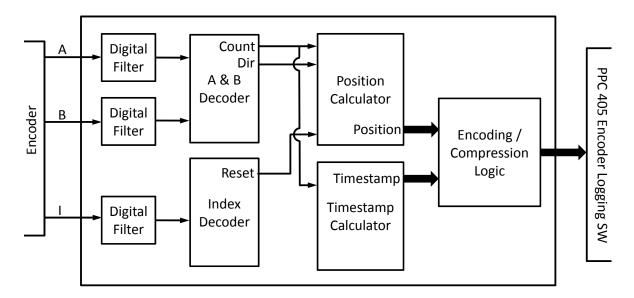

| Figure 3-37: Schematic representation of the time stamping block implemented using th      | ne |

| FPGA logic fabric                                                                          | 14 |

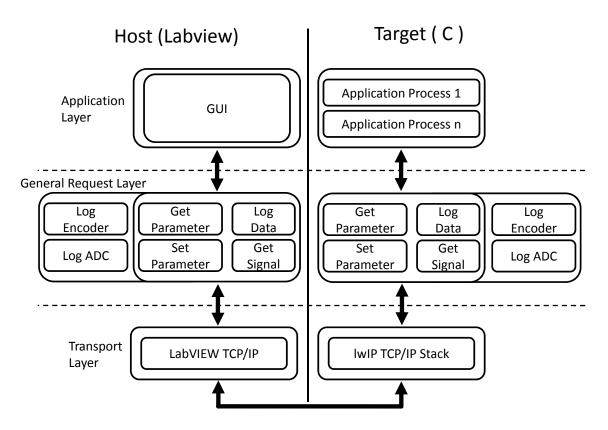

| Figure 3-38: Communication Interface Design                                                | 15 |

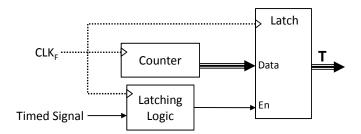

| Figure 3-39: Simple digital timer design counting at CLK <sub>f</sub> frequency            | 16 |

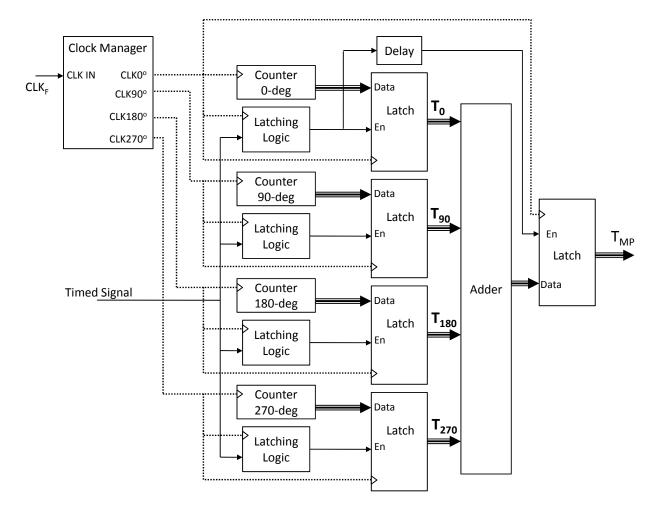

| Figure 3-40: Multi-phase digital timer design, with four 90-deg phase shifted clock,       |    |

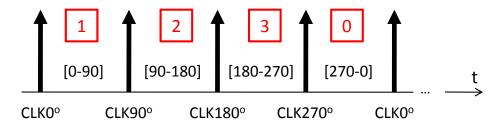

| counting at four times the CLK <sub>f</sub> frequency11                                    | 17 |

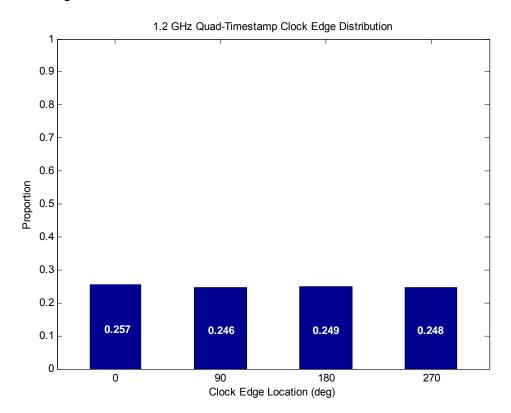

| Figure 3-41: Division of the time axis by the 4 phase shifted clocks                       | 18 |

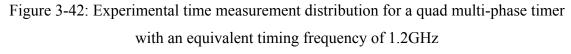

| Figure 3-42: Experimental time measurement distribution for a quad multi-phase timer       |    |

| with an equivalent timing frequency of 1.2GHz                                              |    |

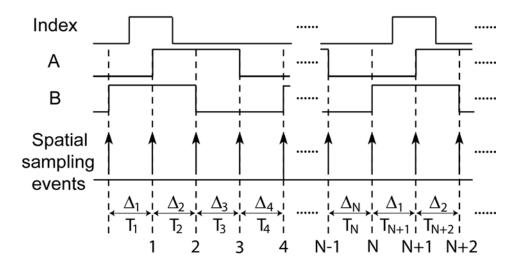

| Figure 4-1: Spatial sampling events in rotary encoders [1]                                 | 24 |

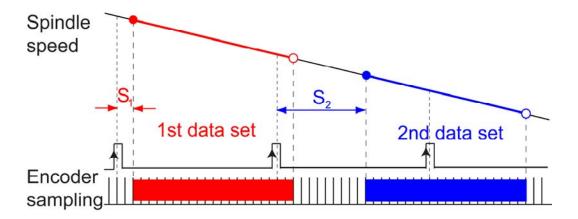

| Figure 4-2: Two data sets used for self-calibration [1]                                    | 28 |

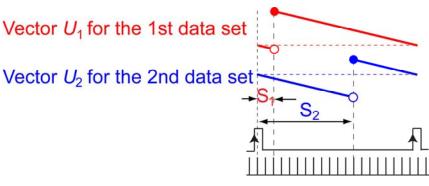

| Figure 4-3: Vectors $U_1$ and $U_2$ of the two data sets $\begin{bmatrix} 1 \end{bmatrix}$ |    |

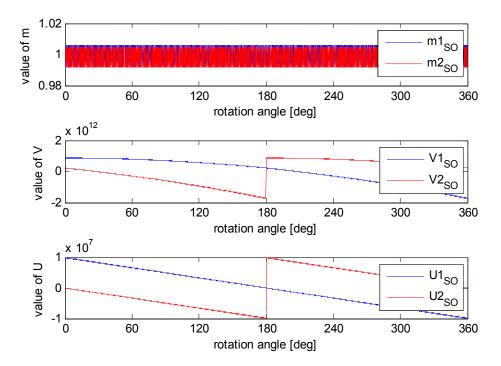

| Figure 4-4: Measurement vectors m, V, and U for second order (SO) method at 600-RPI        |    |

| with a 100-MHz clock                                                                       | 36 |

| Figure 4-5: Measurement vectors m, V, and U for second order (SO) method at 600-RPM                                |

|--------------------------------------------------------------------------------------------------------------------|

| with a continuous clock                                                                                            |

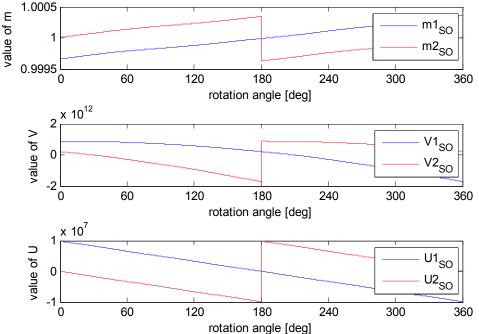

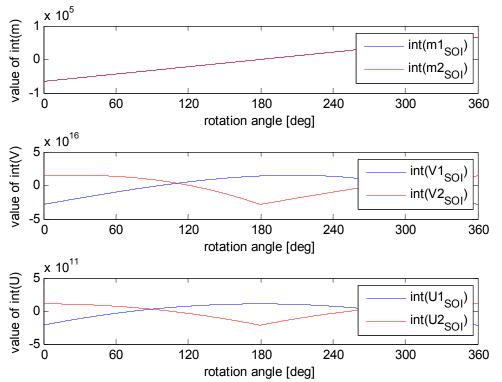

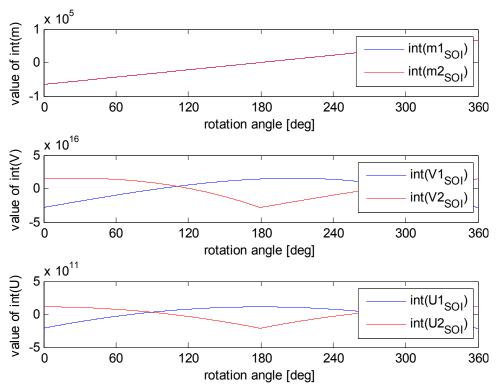

| Figure 4-6: Measurement vectors m, V, and U for second order integral (SOI) method at 600-RPM with a 100-MHz clock |

| Figure 4-7: Measurement vectors m, V, and U for second order integral (SOI) method at                              |

| 600-RPM with a continuous clock                                                                                    |

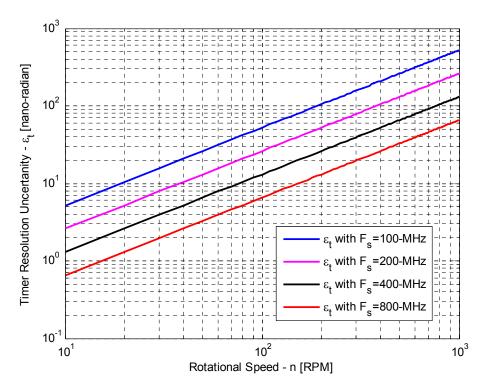

| Figure 4-8: Expected encoder calibration uncertainty <i>Et</i> caused by limited time measurement resolution       |

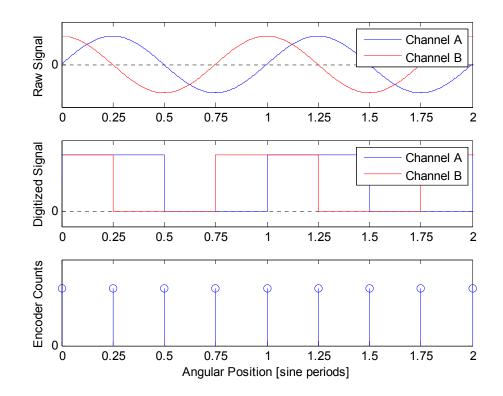

| Figure 4-9: Analog encoder signals transformed into digitized signals and encoder counts                           |

| 140                                                                                                                |

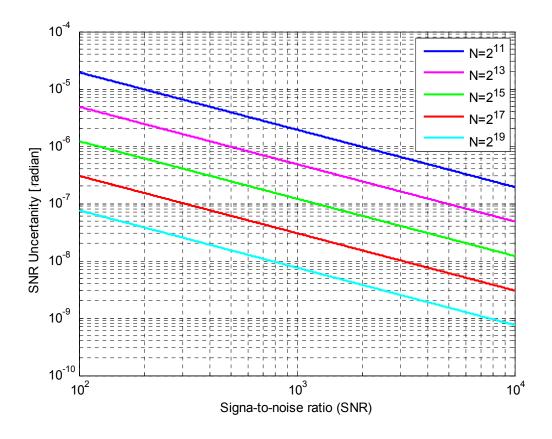

| Figure 4-10: Uncertainty due to signal noise versus signal to noise ratio (SNR) for                                |

| different number of encoder sine waves per revolution (N) 142                                                      |

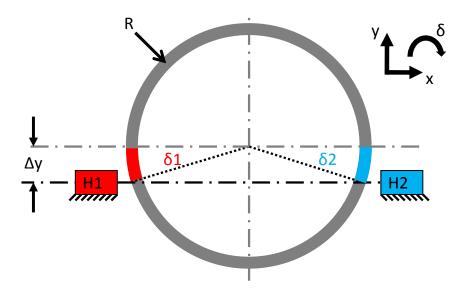

| Figure 4-11: Angle measurement error due to lateral error motion                                                   |

| Figure 4-12: Mechanical angle misalignment of multiple read-heads used for lateral rotor                           |

| vibration reversal                                                                                                 |

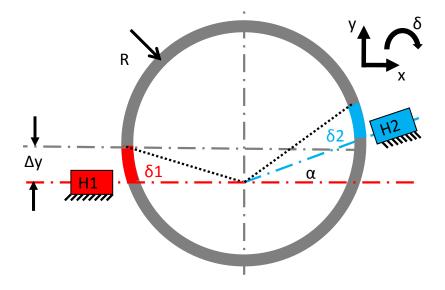

| Figure 4-13: Schematic view showing the rotor and the stator frames and the vibration                              |

| isolation system                                                                                                   |

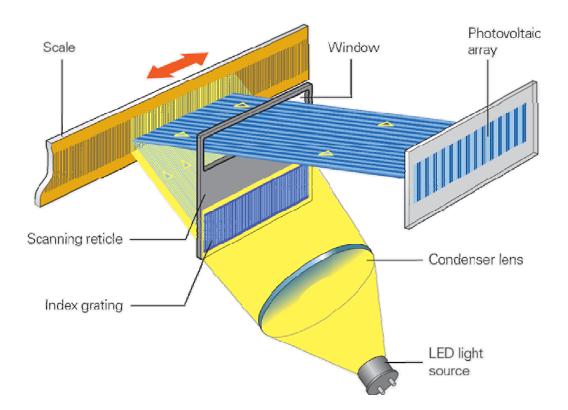

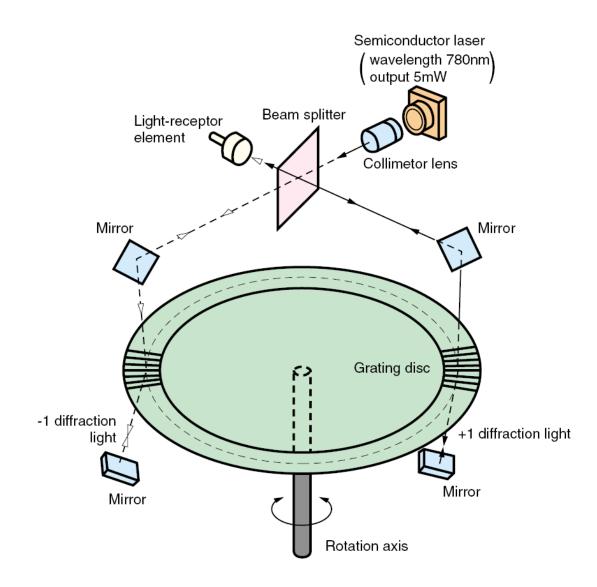

| Figure 4-14: Typical configuration of the imaging method for optical encoder sensing                               |

| [courtesy of Heidenhain] [17]                                                                                      |

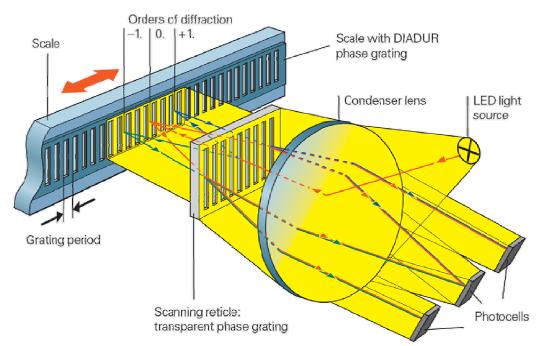

| Figure 4-15: Typical configuration of the interferential method for optical encoder                                |

| sensing [courtesy of Heidenhain] [17]                                                                              |

| Figure 4-16: Implementation of the interferential method in Canon encoders [courtesy of                            |

| Canon] [19]                                                                                                        |

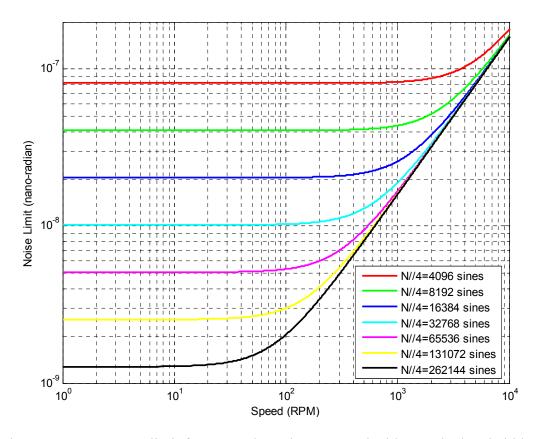

| Figure 4-17: Accuracy limit from encoder noise vs. speed with encoder bandwidth of                                 |

| 350-kHz, SNR of 3000, and for different number of encoder sines per revolution (N/4),                              |

| assuming the same $f_{3dB}$ and $SNR_0$                                                                            |

| Figure 4-18: ERA4282C encoder from Heidenhain [courtesy of Heidenhain] [17] 158                                    |

| Figure 4-19: RON905 encoder from Heidenhain [courtesy of Heidenhain] [5]                                           |

| Figure 4-20: Reference encoder error map used for simulation                                                       |

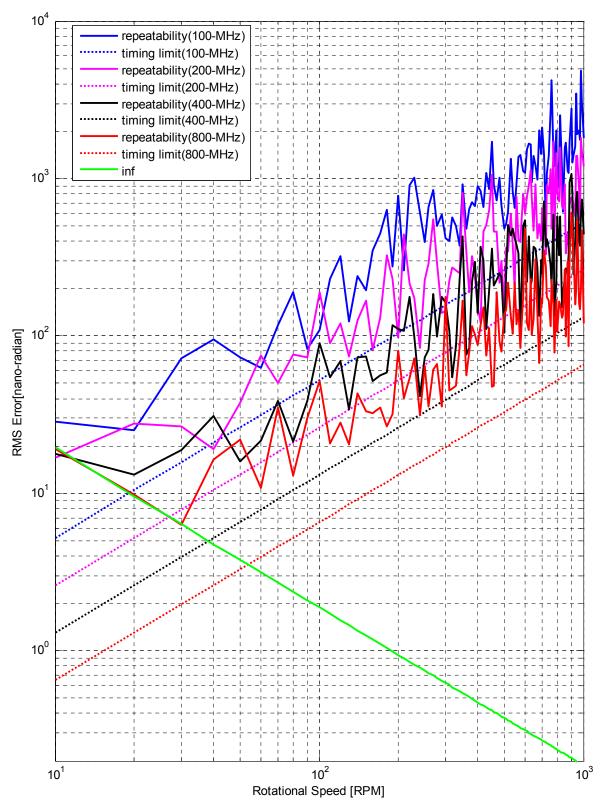

| Figure 4-21: Accuracy plot of the second order method results in simulation for 10-1000                            |

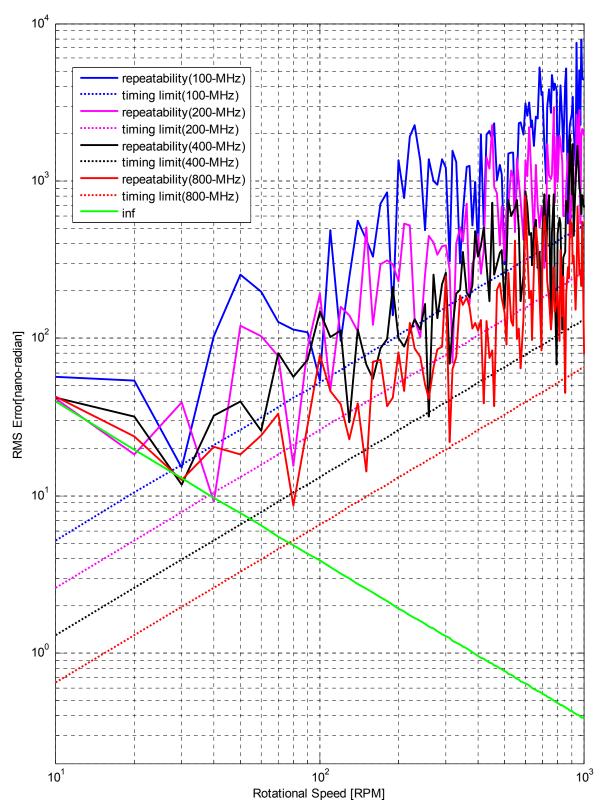

| RPM and with continuous, 100, 200, 400, and 800 MHz timers                                                         |

| Figure 4-22: Repeatability plot of the second order method results in simulation for 10-                           |

| 1000 RPM and with continuous, 100, 200, 400, and 800 MHz timers                                                    |

| Figure 4-23: Calibration result of second order method at 200-RPM and with a 100-MHz                               |

| timer                                                                                                              |

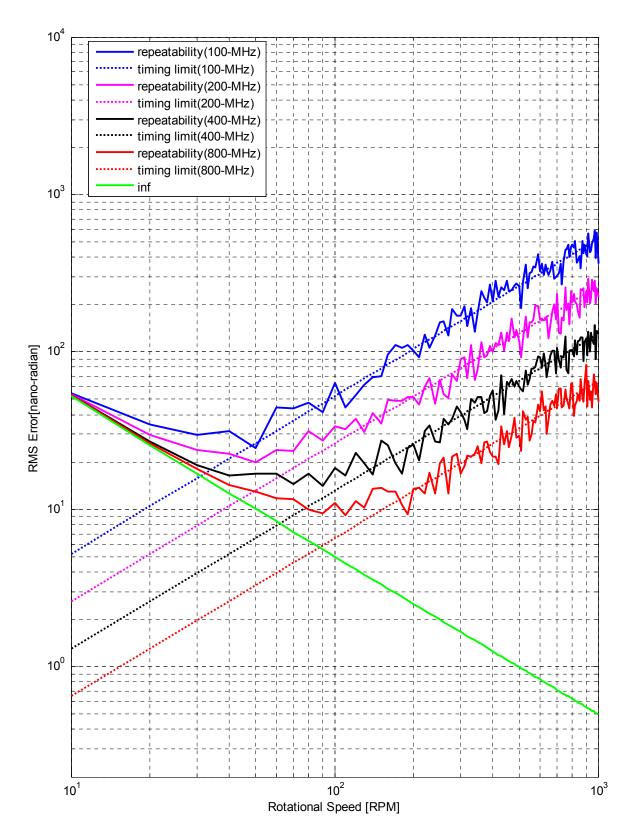

| Figure 4-24: Accuracy plot of the second order integral method results in simulation for                           |

| 10-1000 RPM and with continuous, 100, 200, 400, and 800 MHz timers                                                 |

| Figure 4-25: Repeatability plot of the second order integral method results in simulation                          |

| for 10-1000 RPM and with continuous, 100, 200, 400, and 800 MHz timers                                             |

| Figure 4-26: Calibration result of second order integral method at 200-RPM and with a                              |

| 100-MHz timer                                                                                                      |

| Figure 4-27: The experimental setup used for encoder calibration                                                   |

|                                                                                                                    |

| Figure 4-28: Overview of the experimental procedure                                                                |

| Figure 4-29: Ultra precise rotary table designed and built as a part of the experimental                           |

| setup                                                                                                              |

| Figure 4-30: Set of electronics designed and built as a part of the experimental setup 175                         |

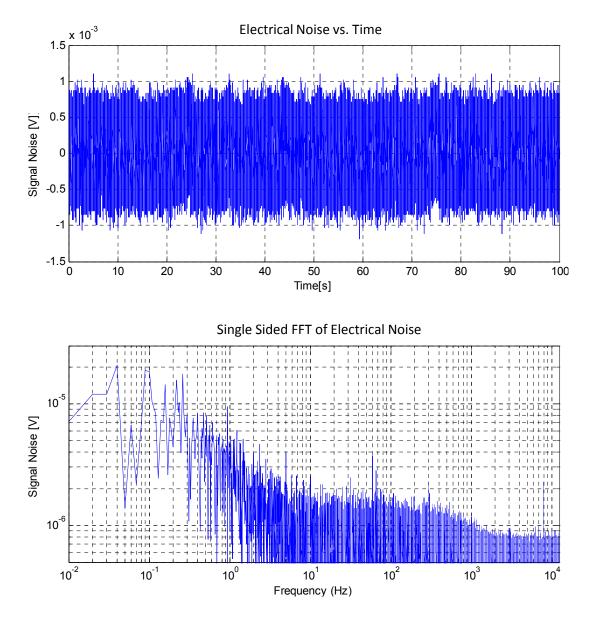

| Figure 4-31: Time (top) and frequency (bottom) plots of read-head's positive side                                          |

|----------------------------------------------------------------------------------------------------------------------------|

| channel-A noise captured at 25-kHz. 177                                                                                    |

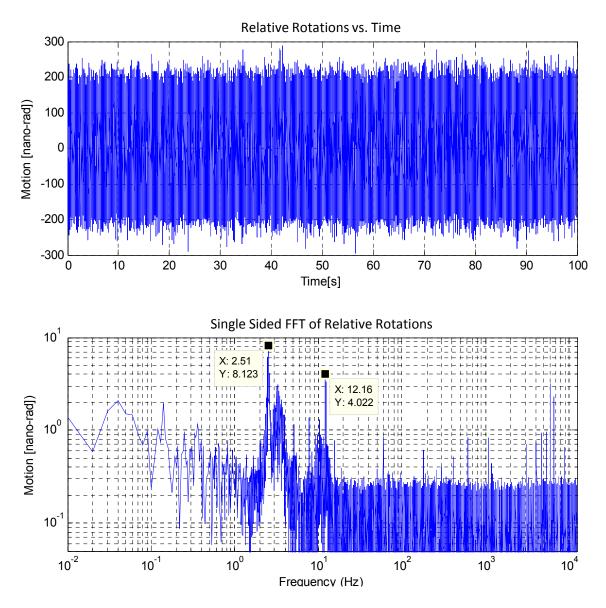

| Figure 4-32: Time (top) and frequency (bottom) plots of relative rotations between stator                                  |

| and rotor as seen by the encoder                                                                                           |

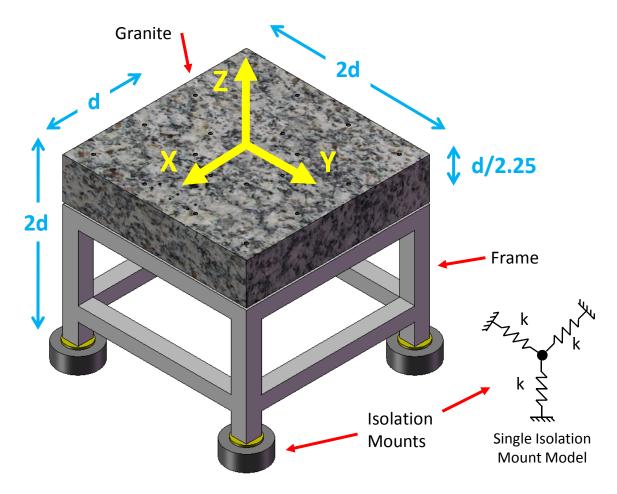

| Figure 4-33: Schematic representation of the granite vibration isolation table (d= 18 inch)<br>180                         |

| Figure 4-34: Free-body-diagrams used for derivation of the table's four vibration modes                                    |

|                                                                                                                            |

| Figure 4-35: Synchronized time plot of relative rotations (top) and supply pressure                                        |

| fluctuations (bottom) for the spindle while left stationary with no active supply regulators over 1-hour sampled at 500-Hz |

| Figure 4-36: Frequency content of the rotation (top) and pressure (bottom) measurements displayed in Figure 4-35           |

| Figure 4-37: Synchronized time plot of relative rotations (top) and pressure fluctuations                                  |

| (bottom) with two active regulators over 1-hour sampled at 500-Hz                                                          |

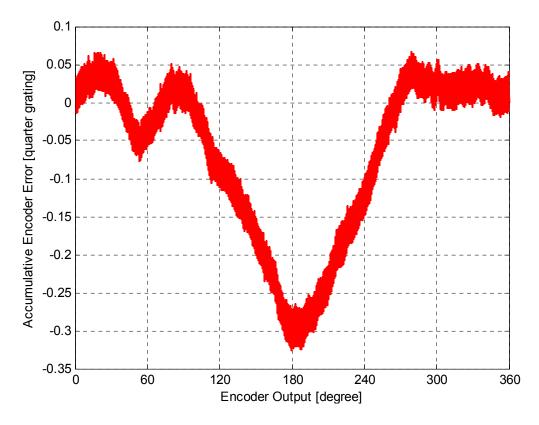

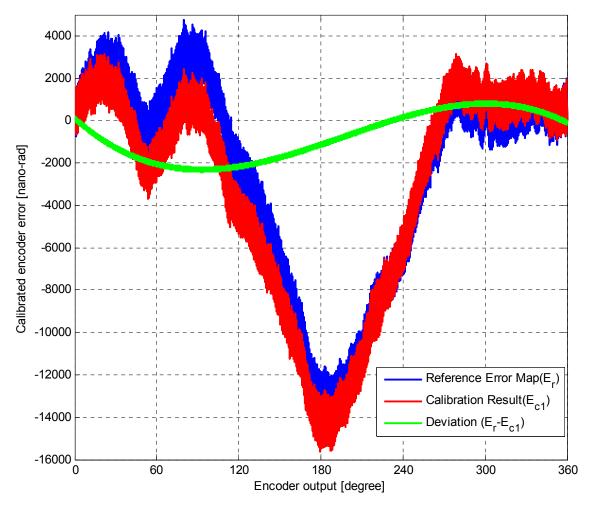

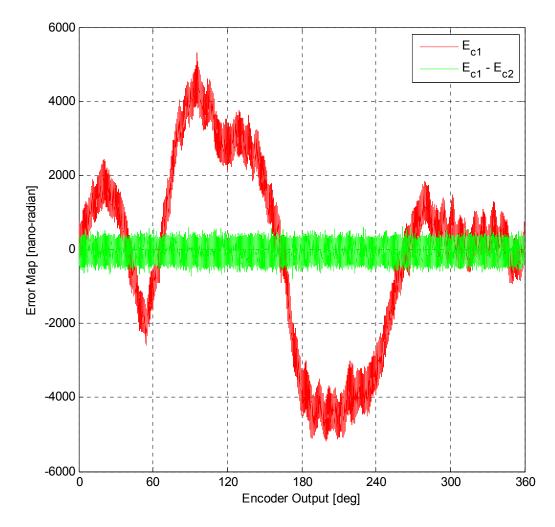

| Figure 4-38: Error-Map obtained experimentally $(E_{cl})$ and the deviations between the two                               |

| sets $(E_{c1} - E_{c2})$ generated by a single execution of the algorithm. The error-map was                               |

| obtained at 220 RPM using the SOI method with $S_1=0$ and $S_2=1.5$                                                        |

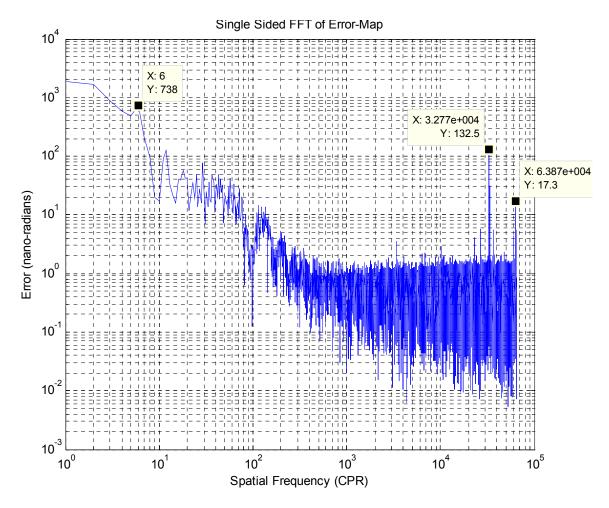

| Figure 4-39: Frequency content of the representative error-map shown in figure 4-38. 188                                   |

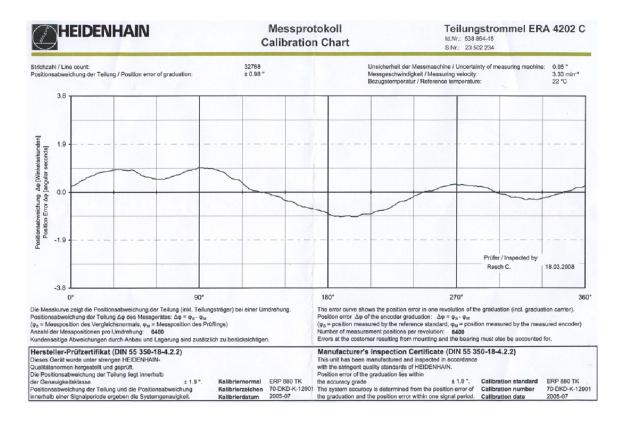

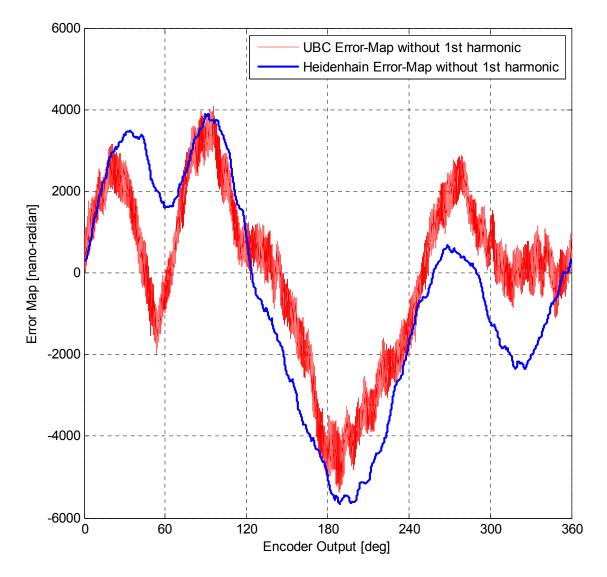

| Figure 4-40: Error-map supplied by Heidenhain with our ERA4282C encoder drum                                               |

| obtained at 3.33 RPM (serial number 23-502-234)                                                                            |

| Figure 4-41: Comparison between Heidenhain's and our error map for the ERA4282C                                            |

| drum with the serial number of 23-502-234                                                                                  |

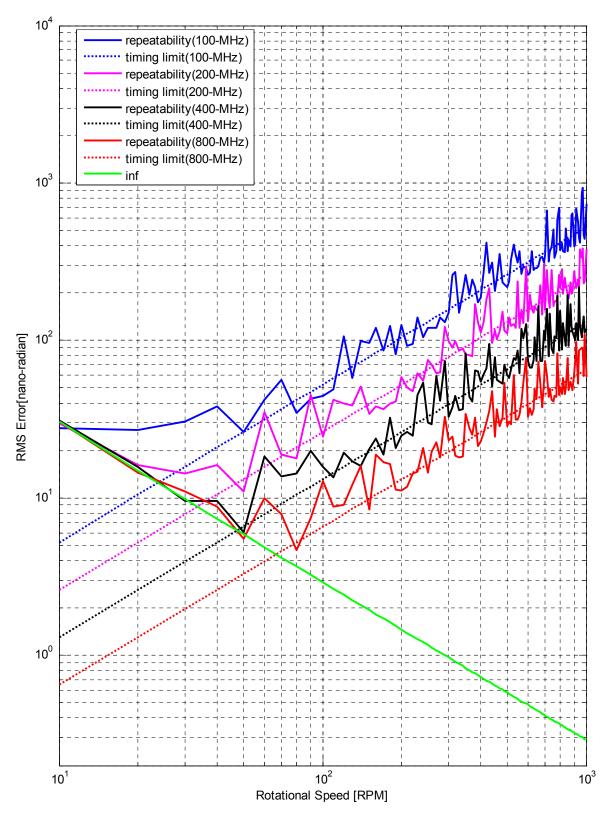

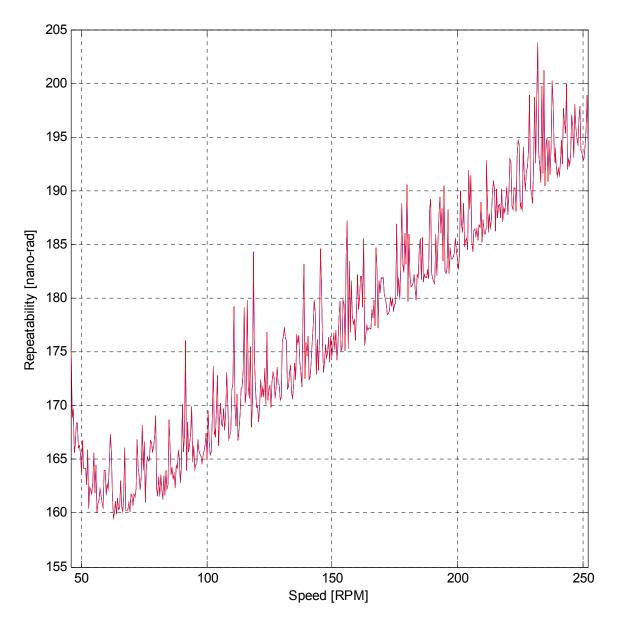

| Figure 4-42: Continuous encoder calibration repeatability (R) plot with the second order                                   |

| integral method                                                                                                            |

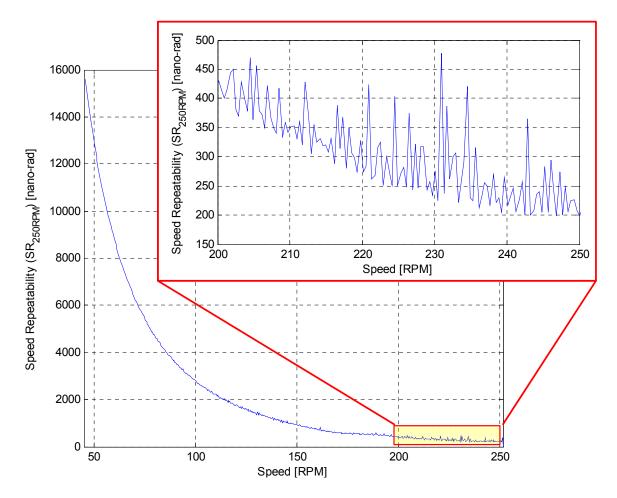

| Figure 4-43: Continuous calibration speed-repeatability (SR250RPMn) plot with second                                       |

| order integral method, using reference speed of $n_0=250$ RPM, and for $n \in 50 - 250$ . 195                              |

### Acknowledgements

First, I would like to thank my thesis supervisor, Professor Xiaodong Lu, for introducing me to the area of precision engineering and creating the opportunity for me to work on very exciting research. He helped me learn many interesting topics, such as circuit design, control, and mechanical design. More than anything else, I am grateful to him for being such a great inspiration and helping me develop and believe in my abilities. He trusted me with tasks which seemed next to impossible to me at first; however, he was patient and followed and directed my progress. I find his analytical skills, work standard, and personality inspirational. It has been a privilege to work with Professor Lu. It is an honor for me to be his first student.

I am thankful to Professor Yusuf Altintas and Professor Juri Jastkevich for being in my thesis committee. They have always been very supportive and I have learned so much from their courses in the UBC mechatronics program.

KLA Tencor financially supported this research project. Collaboration with KLA Tencor was an excellent professional experience for me. I would like to thank Marek Zywno, Upendra Ummethala, Joshua Clyne, and Tao Zhang. Their feedback and critical questions were very helpful to deriving my research in the right direction.

I have been very lucky to have lab mates, who are great friends and colleagues. I have enjoyed working with them and have had great times together inside and outside the lab. Their help has been very important to my research. Kris Smeds designed the software for interfacing to my electronics. Richard Graetz and I worked very closely on the encoder calibration testing and development as well as the daughterboard design. Arash Jamalian helped me with the mechanical drawings and the daughterboard design. Thank you for all your help.

I am indebted to my parents; with their support, they have made many of the opportunities in my life possible. I want to thank my sister, Yalda, for helping me with her photography skills. I would like to thank my Mashad FC team mates, particularly Arash, for the championship and the exciting times we had together. I am grateful to Sophiya for making my life so much more beautiful. I feel very confident having a dependable friend like her.

For my grandmas,

# **CHAPTER 1**

## Introduction

Rotary encoders are widely used for rotation angle sensing. High precision encoders are desired for better rotation angle and velocity measurement. Among other areas, semiconductor industry, precision manufacturing, and astronomy are some sectors that can benefit from high-precision encoders. Encoder calibration is commonly used to enhance the encoder accuracy. In this thesis, a precision rotary table and enabling high-speed electronics are implemented and are used to improve and experimentally demonstrate better encoder calibration results.

The encoder calibration method originally developed in [1] is used for this research. So far, an encoder calibration repeatability of 150 nano-radians<sup>1</sup> has been experimentally demonstrated which is significantly better than the previous results achieved using this method. Our simulations and analysis shows that this method can potentially reach an accuracy level of 10 nano-radians.

Next, we discuss in details an example application of precision angular encoders in the semiconductor industry.

<sup>&</sup>lt;sup>1</sup> This thesis uses nano-radians as angular measurement unit (1nano-radian = 0.0002 arc-second).

## 1.1 High Accuracy Angular Encoder Applications in Semiconductor Industry

The semiconductor industry manufactures electronics chips which are the basic blocks of all the electronic devices. The Semiconductor Industry Association (SIA) estimates an annual worth of about \$257-billion in 2008 and predicts that 234,000 people are employed by this industry in United States alone in 2005 [2]. This industry is very important to economic growth as it supplies the core resource of many important sectors such as telecommunications, internet, and media.

The semiconductor industry's fast rate of advancement differentiates it from other industries. Smaller semiconductor devices with more performance and less cost are being offered every year. In 1965, Gordon E. Moore predicted that the number of transistors in an electronic device was doubling every two years [3]. The industry has kept up with this prediction since then. This industry's fast advancing nature has created a very competitive atmosphere and a great need for new and innovative technologies to push the manufacturing limits and to enable creating smaller and faster devices.

The International Technology Roadmap for Semiconductors (ITRS) is an association which helps the advancement of the semiconductor industry by directing the efforts of the industry, national, and university research labs working in this field. ITRS publishes a roadmap for advancement of the semiconductor industry and outlines the challenges and difficulties to be addressed. The roadmap is created based on the opinion of more than 800 experts working in the field around the world. To create a unified practical advancement criterion, ITRS defines the roadmap based on the distance between

the metal lines connecting to the DRAM bit cells. The distance is termed as half-pitch and refers to the average of the metal line width and the distance between two adjacent lines. The roadmap for the DRAM devices generated by ITRS is shown in Table 1-1. The expected simultaneous reduction in size and cost, shown in the ITRS estimate, provides a strong incentive for advancement of the semiconductor industry.

|               | Year |      |      |      |      |      |      |      |      |

|---------------|------|------|------|------|------|------|------|------|------|

|               | 2007 | 2008 | 2009 | 2010 | 2011 | 2012 | 2013 | 2014 | 2015 |

| DRAM 1/2      |      |      |      |      |      |      |      |      |      |

| Pitch         | 65   | 57   | 50   | 45   | 40   | 36   | 32   | 28   | 25   |

| (nm)          |      |      |      |      |      |      |      |      |      |

| Cost/Bit @    |      |      |      |      |      |      |      |      |      |

| Production    | 0.96 | 0.68 | 0.48 | 0.34 | 0.24 | 0.17 | 0.12 | 0.08 | 0.06 |

| (micro-cents) |      |      |      |      |      |      |      |      |      |

Table 1-1: ITRS roadmap for expected reduction in DRAM <sup>1</sup>/<sub>2</sub> pitch size and cost/bit [3]

Until now, the industry has used 193-nm optical lithography for mass manufacturing of the semiconductor devices; however, this method has reached its optical diffraction limit. In the optical lithography process, a light source with 193-nm wavelength is used to replicate the patterns on a master mask onto a wafer coated with photo-sensitive materials. The wavelength of the light source limits the minimum feature size which can be clearly transferred and focused from the mask onto the wafer. ITRS finds the optical lithography process to be limited to 65-nm DRAM half pitch.

To continue the trend of decreasing half pitch other lithography methods such as Immersion, Double Patterning, Extreme Ultra Violet (EUVL), Mask-less (ML), and Imprint lithography methods are being researched and developed [4]. Immersion lithography operates in the water medium where due to high refraction index of water the wavelengths become smaller. Double patterning uses two masks, each with twice the critical dimension, creating a single image. Extreme ultra violet light with only 14-nm wavelength is used in EUVL to perform lithography. Mask-less methods use an electron beam to etch features into the wafer. The imprint lithography method replicates a master pattern using means similar to mechanical molding.

ITRS outlines the potential manufacturing processes for different generations of DRAM half pitch. ITRS's predictions are summarized in the chart in Figure 1-1, where potential solutions at each DRAM half pitch stage are listed in the same order as their probability of being the dominant solution. ITRS finds 193-nm optical lithography to be limited to 65-nm DRAM half pitch. ITRS predicts that water immersion lithography can be used to extent optical lithography to 32-nm and double patterning has the potential to extent immersion optical lithography to below 32-nm DRAM half pitch. ITRS terms EUVL, ML, and Imprint as post-optical alternatives and expects them to be the dominant manufacturing solution at DRAM half pitch of 32-nm and below. Currently, ML methods have a limited throughput, and hence, are used for prototyping and low volume manufacturing only. ITRS finds EUVL to be the most probable post-optical alternative; however, it mentions that breakthroughs with ML processes can be very significant and can create paradigm shifts. If adapted for mass manufacturing, ML methods will eliminate the need for master-masks, and hence, will reduce cost and cycle times.

Figure 1-1: Potential semiconductor manufacturing solutions at each stage of ITRS roadmap [4]

KLA Tencor, a leader in semiconductor manufacturing and inspection equipment development, is developing a mask-less electron-beam lithography technique which can significantly increase the throughput of the ML methods. Such a system will enable cheaper and more efficient ML production and will bring the semiconductor industry a step closer to mass manufacturing using ML techniques. A key component to increasing the throughput of their e-beam lithography machine is an angular encoder with accuracy of 10 nano-radians at speeds up to 600-rpm. Currently, there are no rotation measurement solutions which have approached such high accuracy requirements at such high speeds.

The state of the art encoder technology is only accurate to 2000 nano-radians at speeds only as high as 60-rpm. The available encoder calibration methods have enabled

enhancing an encoder's effective accuracy to levels as low as 200 nano-radians at low speeds. Dr. Xiaodong Lu, at the University of British Columbia, has invented a novel encoder calibration method which can potentially meet the accuracy requirements of KLA Tencor's next generation e-beam machines. The research in this thesis is aimed to improve and experimentally demonstrated the accuracy limit of the calibration technique. An overview of the previous encoder calibration work is provided in the next section.

### **1.2 Prior Art Rotary Metrology Calibration Methods**

Angle encoders are widely used for large rotation angle sensing. The state-of-the-art rotary encoder technology can only reach accuracy levels up to 2,000 nano-radians due to error in the scale's grating lines spacing, mounting misalignments, and other imperfections[5]. Attempts have been made to calibrate rotary encoders and improve their accuracy. An ideal calibration method would identify and compensate the repeatable portion of the encoder error. So far, the best stable calibration repeatability is 50 nano-radians which has been achieved at *National Institute of Advanced Industrial and Science Technology (AIST)* [6]and *Physikalisch-Technische Bundesanstalt (PTB)* [7]. All developed encoder calibration methods can be divided into four categories: comparison-calibration-methods, cross-calibration-methods, direct-calibration-methods, and temporal self-calibration methods. Some of the major prior art calibration methods are discussed under these categories in the next four sub-sections.

#### **1.2.1** Comparison Calibration Methods

The calibration methods which rely on a more accurate measurement reference to calibrate a less accurate sensor are termed as comparison-methods. Precision polygons along with photo-electric autocollimator can be used as a calibration reference. As an alternative, Renishaw has integrated a precision indexed rotary table along with a laser interferometer to create an angle reference accurate to 4000 nano-radians [8]. Ring lasers have also been used as an accurate angle reference in [9-11], where accuracies as low as 500 nano-radians have been demonstrated. Finally, other calibration methods have been used to develop accurate angle references which can now be used for comparison

calibration of rotary sensors. The work done by AIST in [6] and PTB in [7] are the most accurate examples of such work where 50 nano-radians reference angle repeatability has been achieved.

The comparison-calibration methods are limited to their reference angle's accuracy. Most angle references only cover a small portion of a single rotation, so the calibration needs to be performed in multi steps. As a result, the process will be time-consuming and less accurate. Furthermore, the comparison-calibration methods require connecting the reference sensor and the sensor being calibrated on a single axis. Large uncertainties are introduced due to misalignments associated with this connection. Finally, recalibration of the encoder in the final product is not possible using this method, or in other words, this is an off-axis calibration method. As a result, the comparison calibration methods cannot capture the variations due to changes in mounting and operating conditions, such as speed and temperature.

#### **1.2.2 Cross-Calibration Methods**

In the cross-calibration methods, a second artefact using an auxiliary non-calibrated rotation sensor is introduced. Opposed to the comparison-calibration methods, the auxiliary sensor does not require a higher accuracy as this method calibrates both sensors together. In this method, the difference in measurements of the primary sensor and the auxiliary sensor is termed as relative error and can be measured. The primary sensor is fixed at different relative angular positions to the secondary sensor, and at each relative position, the relative error is measured along a full rotation. The measured relative error combined with circular closure equations of each sensor can provide the error map for both of the sensors. [7, 12] are examples of this technique. PTB has attempted cross-

calibration using their setup in [7] and has demonstrated 50 nano-radians long-term and 10 nano-radians short-term repeatability.

The cross-calibration method can produce higher accuracy. However, it is very time consuming and difficult as the relative error needs to be measured for different relative angular positions of the primary and the secondary sensors. This method can be applied at very low rotation speed so it cannot capture the variations in the error resulting from the changes in speed. Also, it is not practical to recalibrate an encoder during a machine's operation using this method, and as a result, the variations due to changes in temperature and other operating conditions cannot be identified. In addition, for a limited number of relative positions of the sensors, some harmonics of the error will not be calibrated. As a result, the effectiveness of the method depends on how many relative positions are used. Furthermore, the estimate of the higher harmonic error components is very sensitive to the relative angle between the two sensors. Finally, this method would require an additional rotation sensor plus extra features for precise relative positioning of the two sensors; therefore, it is impractical to implement this method on every setup. However, the results can be used as a reference for comparison-calibration.

#### **1.2.3 Direct Calibration Methods**

Direct calibration methods can be seen as a modification of the cross-calibration method where no manual adjustment of the setup is required during the calibration process. In such systems, multiple read heads are utilized to provide the secondary artefact at different relative angular positions. As a result, there is no need for manual movement of the auxiliary sensor relative to the primary sensor, and hence, the sensor can be automatically calibrated. Such methods are termed as direct methods because, opposed to

cross-calibration, the calibration is performed directly on a single system without the need for manual adjustments to the system. [6, 7, 13] have applied the direct-calibration method. AIST [6] has demonstrated 0.01 arc-second uncertainty, aside from the shaft eccentricity, using this method. PTB has performed both cross-calibration and direct-calibration using their setup in [7], but has obtained more accurate results using the cross-calibration method.

This type of calibration method can provide reasonably good calibration results and is much easier to apply compared to the cross-calibration methods. However, the method still requires multiple read-heads that are accurately spaced. The effectiveness of the method depends on the number of the heads and the accuracy of their spacing. For a limited number of read-heads, certain components of the error will remain uncalibrated. The accuracy of the spacing of the heads will affect the precision of the high frequency components of the generated error-map. Finally, because the read head is varying for each artefact, the calibration method fails to capture the error specific to the read-heads.

#### **1.2.4 Temporal Calibration Methods**

Temporal calibration methods rely on time measurements of the signals to identify the encoder error map. Such methods assume a specific relation between the angular position and time, which allows them to convert time measurement to an angular position reference for encoder calibration. Some examples of temporal calibration methods are [1, 14, 15]. The main limitation of this method is that it requires good and consistent system dynamics; however, this is the case for most precision setups. If implemented effectively, temporal calibration methods will have numerous advantages: they will require no additional components for referencing to, such as a second encoder or multiple read-

heads; they can perform automatically; they can calibrate the encoder on the application axis, and hence, will eliminate all error including mounting and read-head error; and, they can calibrate all the components of the error down to the single count level.

In [14], a hyperbolic function is fitted, using the least square method, to the trail of the encoder readings which are captured as a function of time. The identified encoder is compensated using a delay circuitry and as result is only effective for constant speeds. In this work, the encoder error is not separated before applying the fit. Finally, the assumed hyperbolic relation may not be the most suitable expression of the system dynamics.

In [15], the angular velocity of the rotor, which has a fly-wheel attached to it, is assumed to be constant. Then, time measurements are directly transferred to a position reference using a constant gain. The platform velocity was estimated as the average velocity during one revolution. Due to the unrealistic constant velocity assumption, the results of this method have limited accuracy.

In [1], a dynamic model with first order damping is assumed. The dynamic model is used to create a set of spatially discrete equations for one revolution which can be solved to obtain an inertial reference frame for encoder calibration. The method finds the platform's initial velocity by combining circular closure equation and the set of dynamic equations. The dynamic model parameters, which include the damping parameters and the inertia, are estimated using the least square method. To prevent encoder error from biasing the least square fit, a novel dynamic reversal method is used to eliminate the error from the least square estimates by looking at the difference of two revolutions rather than

a single revolution. Lu in [1], has experimentally demonstrated a repeatability of 5000 nano-radians which is 30 times smaller than the original encoder error. The accuracy obtained in [1] was limited due to the precision of the encoder, the mechanical setup, and the processing electronics.

Our research identifies the temporal calibration methods to be the most practical method with a potential accuracy beyond any other method. The method developed in [1] is found to be the most complete among temporal calibration methods. As a result, the work in thesis is based on the temporal calibration method developed by Lu in [1]. More details on the workings of this method and the modifications made to it are provided in chapter-4.

### **1.3 Thesis Overview**

The thesis goal is to enhance the state of the art rotation metrology technology to meet electron beam lithography requirement of 10 nano-radians RMS accuracy at 180-RPM. Since the state of the art encoder technology is only accurate to 2000 nano-radians, encoder calibration is required to enhance accuracy. Although two of the available encoder calibration techniques [6, 7] have been able to achieve an angle reference accuracy of 50 nano-radians, their methods work only at speeds below 10-RPM. As a result, they fail to capture the variations due to the changes in speed, and hence, their calibration results in operation are only valid to 200 radians or less. The temporal self-calibration method developed by Lu [1] can work at high-speeds and can capture thermal effects by recalibration during the operation of the device.

We attempt to improve and experimentally demonstrate the accuracy limit of the on-axis encoder self-calibration method developed by Lu[1] To enable achieving the best calibration results, an ultra-precise rotary table and a set of high-speed electronics have been developed in this thesis. The developed setup is then used to carry out encoder calibration research. This thesis is organized into three chapters: ultra precise rotary table design, high-speed electronic design, and encoder calibration algorithm development and experiment. The following sub-sections provide a brief overview of each sub-section.

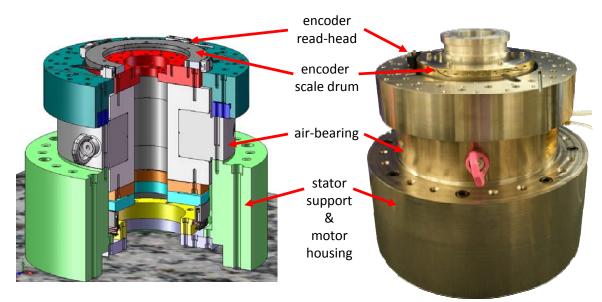

#### **1.3.1** Precise Rotary Table Design

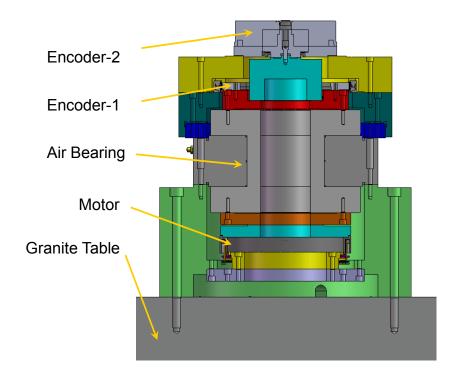

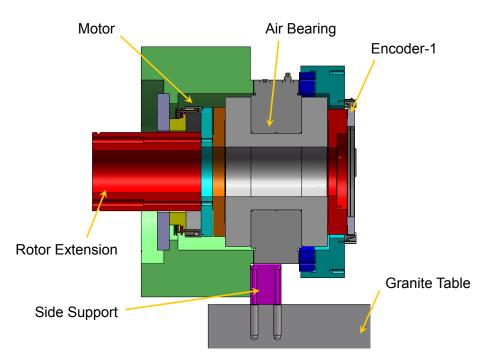

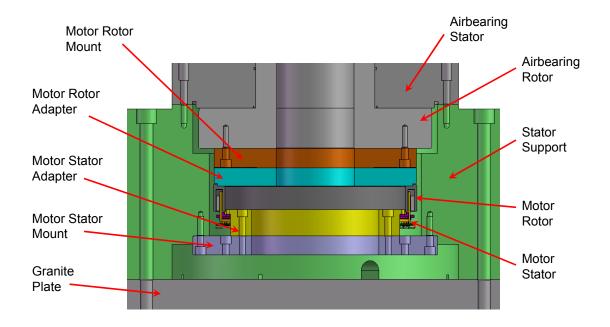

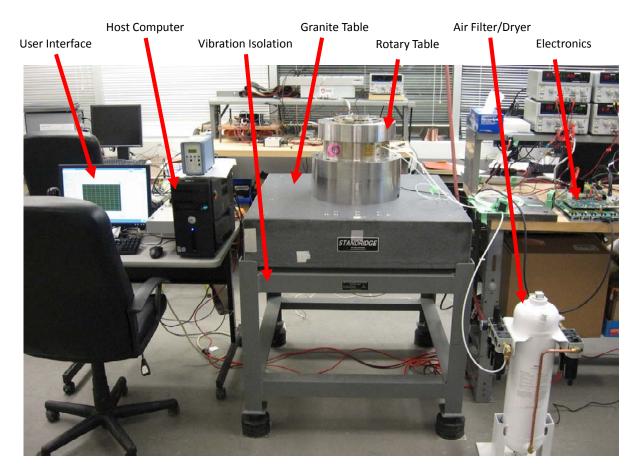

An ultra precise rotary table, shown in Figure 1-2, is designed, manufactured, and assembled as a part of this thesis. For effective encoder calibration, the platform requires to have a repeatable motion and linear dynamics. An airbearing is utilized within the

design for its linear dynamics, high stiffness, and repeatable motion. We have designed the rotary table to include two types of rotary encoders, a 3-D displacement measurement system consisting of a precision ball and three capacitive probes, and a low cogging torque motor. These features are incorporated into the design to enable spindle metrology and control research. More detailed description of the design is provided in Chapter 2, *Mechanical Design*.

Figure 1-2: Ultra precise rotary table designed for spindle metrology and control research

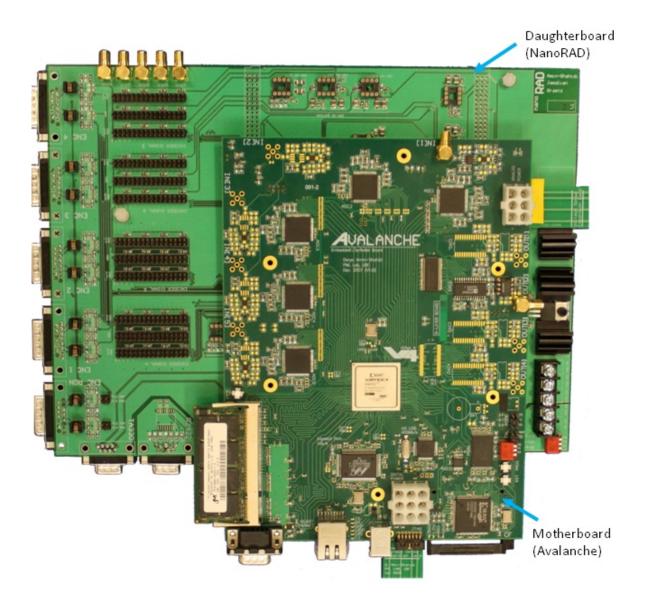

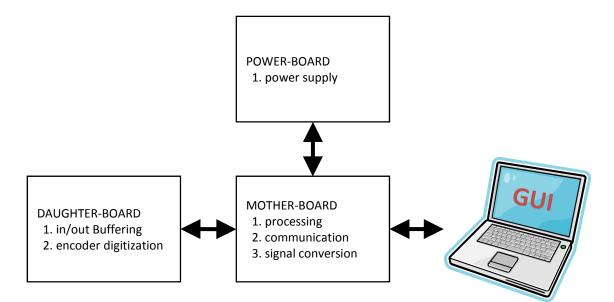

#### 1.3.2 High-Speed Electronic Design

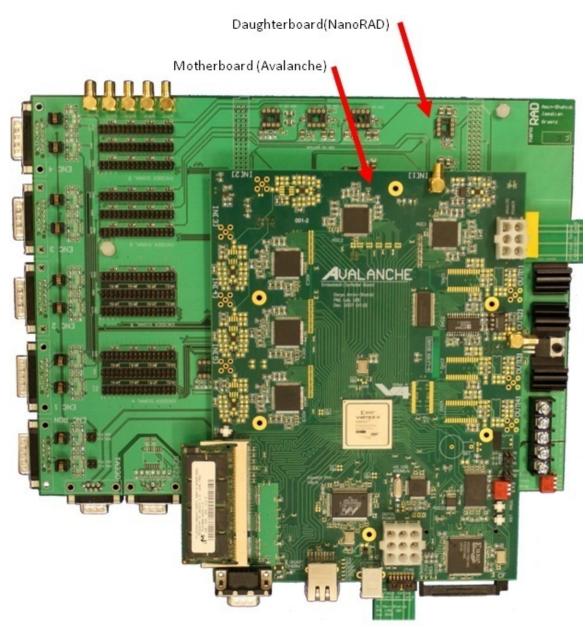

To achieve high metrology and control accuracy, fast real-time signal processing is required. Since no commercial controller met our requirements, I designed and developed our own set of high-speed electronics. A fast FPGA-based motherboard, *Avalanche*, with 300-MHz clocking frequency was built for fast digital processing. A daughterboard, *NanoRAD*, was built to perform application specific analog signal processing, buffering, and routing. Figure 1-3 shows the motherboard and the daughterboard. More details on the electronics design is provided in Chapter 3, *High-Speed Electronics*.

Figure 1-3: Ultra-fast motherboard (Avalanche) and daughterboard (NanoRAD) stack-up

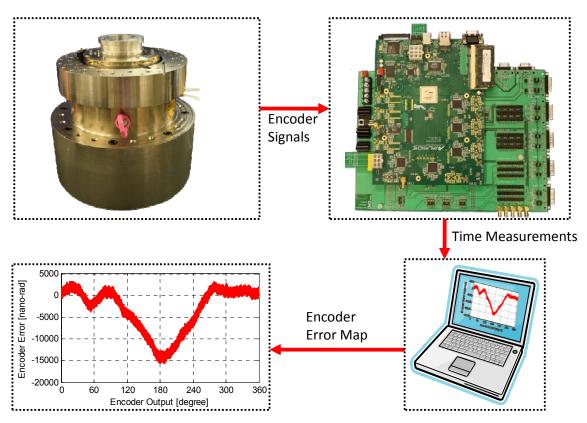

#### **1.3.3 Encoder Calibration**

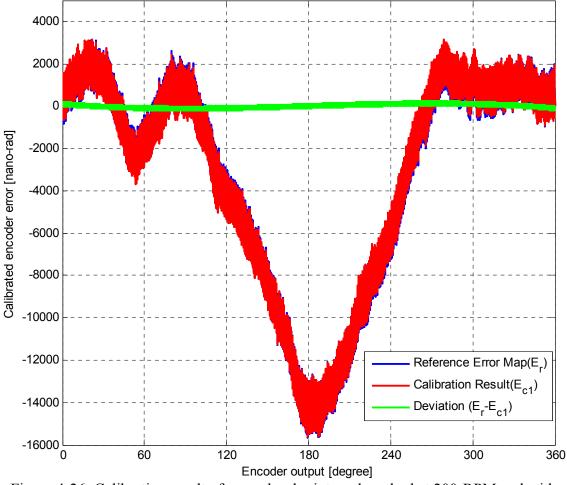

To achieve angular measurement accuracy much better than the angular encoder's accuracy, the encoder included in the setup must be calibrated. The encoder selfcalibration method developed by Lu [1] is used as the basis in this thesis. We try to improve this method to achieve better rotation measurement accuracy. The experimental setup consisting of the mechanical and the electrical design is used to carry out encoder calibration research. The research aims to improve and experimentally demonstrate the accuracy limit of the method in [1]. One encoder error-map obtained experimentally for the ERA4282C encoder utilized in our rotary table is shown in Figure 1-4. More details on the encoder calibration work are provided in Chapter 4, *Encoder Calibration*.

Figure 1-4: Error map obtained experimentally at 220 RPM Using a 200MHz Timer for the Heidenhain ERA4282C (serial# 23-502-234) encoder used in our rotary table design.

## **CHAPTER 2**

## **Precise Rotary Table**

This chapter presents the mechanical design of the precise rotary table (PRT) which is a motorized airbearing-based rotary platform designed to achieve repeatable motion and linear dynamics, both of which are required for effective encoder calibration. The rotary table is equipped with two rotary encoders and a 3D displacement measurement system. The platform is used for testing and development of rotation measurement and control methods.

## 2.1 Design Objective

The main design objective of the mechanical setup is to demonstrate repeatable motion and linear dynamics because the achievable rotation measurement accuracy depends on these two qualities. Encoder calibration will be used to enhance the accuracy of our encoders and achieve better rotation measurement accuracy. Calibration is only effective for removing synchronous (repeatable) error and does not eliminate asynchronous (random) error. Therefore, the mechanical setup is designed to minimize any possible random effect, or in other words, the mechanical setup is designed for repeatability of motion. Moreover, the calibration method finds the error by establishing a linear model of the system dynamics. Non-linear dynamics should be minimized as they cannot be represented by the calibration algorithm's linear model. The PRT is a research tool which will be used for exploring and improving the rotation measurement and control techniques. So, the design includes features, such as two encoders with multiple read-heads and a error motion identification system, which enable investigating different research scenarios.

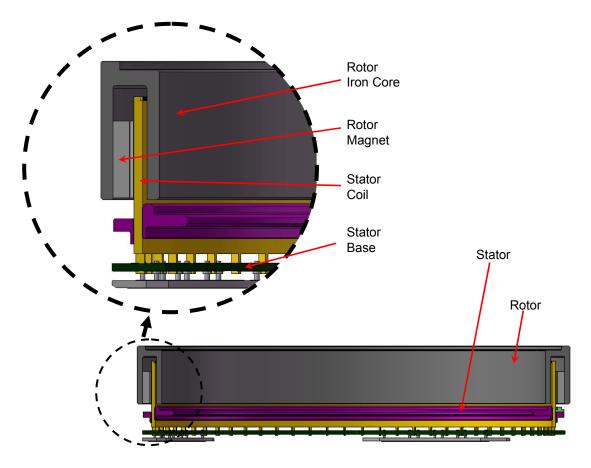

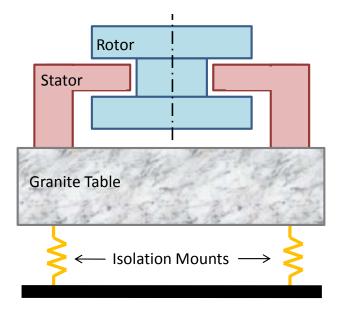

### 2.1 Configurations

The PRT is designed around a Professional Instruments -10R Block-Head<sup>®</sup> airbearing which has low error motion and high stiffness as indicated in table 2-1. The rotary table is motorized using a brushless ThinGap TG8263<sup>®</sup> motor which has minimal torque ripple due to the moving iron-core design. Two different rotary encoders, referred to as Encoder-1 and Encoder-2 from now on, are utilized. Encoder-1 works at all speed ranges and is intended as the final rotation measurement device. Encoder-2 has a stable errormap and is incorporated to compare our results to rotation measurement standards available elsewhere. Also, a displacement measurement system consisting of a precision machined ball and three capacitive probes is incorporated to monitor the spindle error motion. The whole setup is mounted to a granite table top, which is supported by vibration isolation mounts.

|                  |        | Ultimate Working     |         |  |  |

|------------------|--------|----------------------|---------|--|--|

|                  | Radial | 1780 N               | 890 N   |  |  |

| Load<br>Capacity | Axial  | 10700 N              | 5350 N  |  |  |

| Capacity         | Tilt   | 680 N-m              | 340 N-m |  |  |

|                  | Radial | 350 N/micrometer     |         |  |  |

| Stiffness        | Axial  | 1750 N/micrometer    |         |  |  |

|                  | Tilt   | 11.3 N-m/microradian |         |  |  |

| _                | Radial | < 25 nanometers      |         |  |  |

| Error<br>Motion  | Axial  | < 25 nanometers      |         |  |  |

| WIOTION          | Tilt   | < 0.1 microradian    |         |  |  |

| Maximum Speed    |        | 1800 rpm             |         |  |  |

Table 2-1: Specifications for Professional Instrument's 10R Block-Head <sup>®</sup> airbearing with 150-psi operating pressure [16]

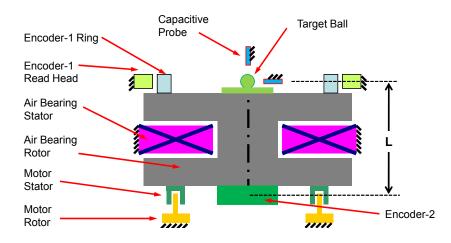

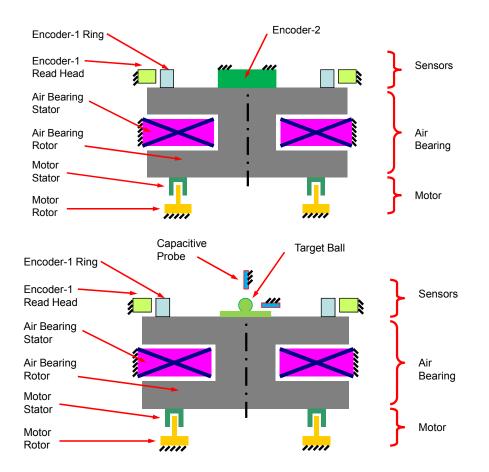

Given the design of Encoder-2 and the displacement measurement system (DMS), they cannot be mounted onto the same side of the airbearing at same time. One way to overcome this issue is to move one of the two to the bottom side. Therefore, a configuration design, shown in Figure 2-1, where Encoder-2 is mounted onto the bottom side was considered. Moving Encoder-2 to the bottom side creates a long mechanical path, as indicated by L in figure 2-1, and introduces Abby error relative to the Encoder-1 rotation measurement. Because it is unnecessary to operate both Encoder-2 and DMS at the same time, another configuration was selected where the user can select which one of the two to use by dismounting one and mounting the other one. The two settings are shown in Figure 2-2. The advantage of the latter configuration design is that it uses the airbearing to isolate the sensitive sensors from any unbalanced force disturbance from the motor. In addition, the sensors are more accessible and can be more easily and better aligned.

The latter configuration where the sensors are mounted on top is selected as the overall configuration of the mechanical setup. The configuration design in Figure 2-2 only shows the general relative configuration of the major parts of the design: sensors, motor, and airbearing. Typical to all the operating modes, an airbearing in the center separates the motor mounted on the bottom side from the sensors mounted on top side. However as mentioned before, the mechanical setup can be adjusted to operate in several modes, each customized for a certain investigation. For example, the system can incorporate two encoders at the same time or can have one encoder and the DMS. The details of the operating modes will be discussed in the subsections to follow.

Figure 2-1: Schematic view of mechanical configuration design - sensors on two sides

Figure 2-2: Schematic view of mechanical configuration design - sensors on top (top: with two encoders, bottom: one encoder and DMS)

#### 2.1.1 Two-Encoder Mode

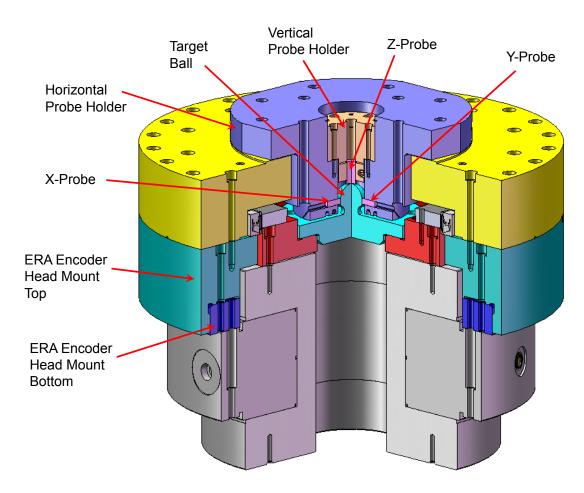

In this operating mode the setup is positioned vertically and incorporates two different encoders at once. This operating mode allows for simultaneous use and calibration of two different encoders under the same conditions. The Encoder-1 is selected to serve as the final rotation measurement device, and Encoder-2, whose error-map is relatively stable, is used to compare our calibration results with encoders calibrated by other methods. The cross-section view of the whole assembly is shown in Figure 2-3. In this mode, both encoders are mounted on the top side and measure the rotation of the airbearing rotor relative to the bearing's stator at the same time. Typical to all the operating modes, the motor is installed on the bottom side and the whole structure is attached to a granite table. The role and features of each encoder and is discussed in more details in section 4.3.4.

Figure 2-3: Cross-section view of the two-encoder operating mode

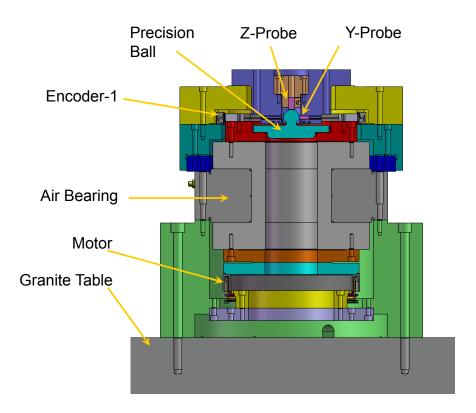

#### 2.1.2 Encoder and 3D Displacement Sensor Mode

In this operating mode the setup is positioned vertically and utilizes one encoder and a 3D displacement measurement system (DMS). Figure 2-4 shows the cross-section view of the Single Encoder plus Displacement Sensors. Encoder-1 is left unchanged on the top side; however, Encoder-2 is replaced with the 3-D displacement measurement system.

Figure 2-4: Cross-section view of the encoder and 3D displacement sensor mode

In this operating mode, Encoder-1 measures rotation of the airbearing while the motion of the center of the encoder ring is monitored in the three translational degrees of freedom (DOF) using the 3D displacement sensing system. An ideal bearing would perfectly constrain all DOFs except for one rotational DOF. However, no bearing is ideal and there is unavoidable error motion associated with the bearing. In this operating mode, the error motion is identified, and its effect on rotation measurement can be studied and compensated. In the mechanical design, the ball's center and the midpoint of the encoder drum axis coincide. This ensures that the motion measured by the DMS is the translation of the encoder drum and is not coupled to any other rotational degrees of freedom.

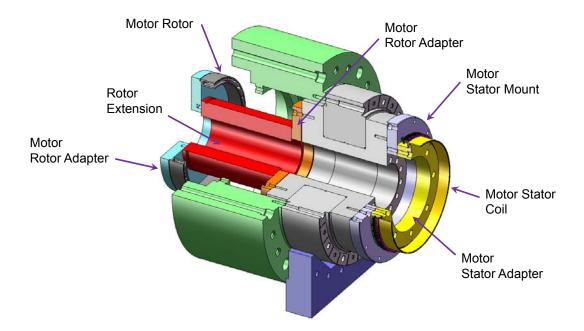

#### 2.1.3 Horizontal Mounting Mode

The two previous operating modes are arranged vertically. It is possible to change the orientation of the whole setup to be horizontal. This configuration is referred to as Horizontal Mounting Mode and its cross-section view is shown in Figure 2-5.

Figure 2-5: Cross-section view of the horizontal mounting mode

The setup is fastened to the granite table using an additional side support piece which uses a V-section to hold the outer diameter of the airbearing's stator. The rotor Extension fixes to the spindle rotor and extends the rotor. This arrangement creates access to the motor as well as the spindle rotor. This operating mode is designed mainly for motor torque constant identification. We propose to use a hanging mass wrapped around the rotor extension to provide a constant torque; then, monitor the current required to act against that constant torque to find the variations in the torque constant as a function of rotation angle.

# 2.2 Encoders Assembly

The encoders are utilized for rotation measurement of the rotary table. The encoders are the central part of the design because the achievable angular motion accuracy is directly dependent on the rotation measurement accuracy from the encoders. To add to the versatility o f this setup as a research tool, two different encoders are incorporated into the design: one encoder without an integral bearing, Encoder-1 in the configuration diagrams, and an encoder with its own built in bearing system, Encoder-2 in the configuration diagrams. Generally speaking, angle encoders with integrated bearings compared to the the encoders without integral bearings have measurements which are less sensitive to mounting variations. On the other hand, they have lower operating speed range, and their integrated bearing can influence and degrade the system dynamics. In PRT, we have integrated both to benefit from the features of each type. This section presents the selected encoders and their mounting design.

### 2.2.1 Encoder without Integral Bearing

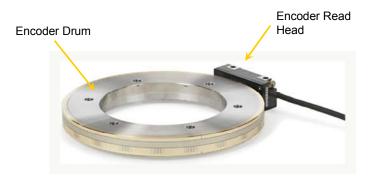

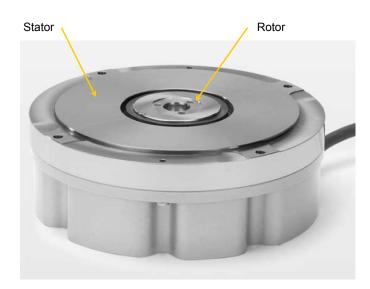

Heidenhain's ERA4282C encoder with 32768-lines is selected as one of the encoders that are used within the setup. The ERA4282C encoder is shown in Figure 2-6. The encoder consists of a line carrier drum which will be mounted and centred to the air bearing rotor, and a read-head to scan the lines, which will be fixed to the stator.

Figure 2-6: ERA4282C encoder from Heidenhain [courtesy of Heidenhain] [17]

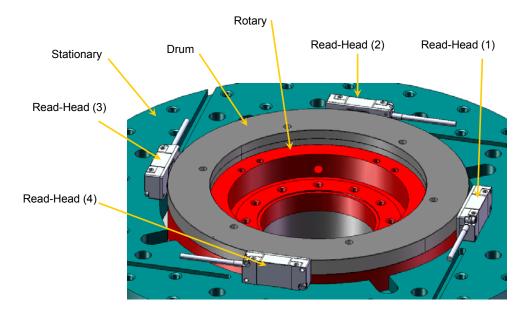

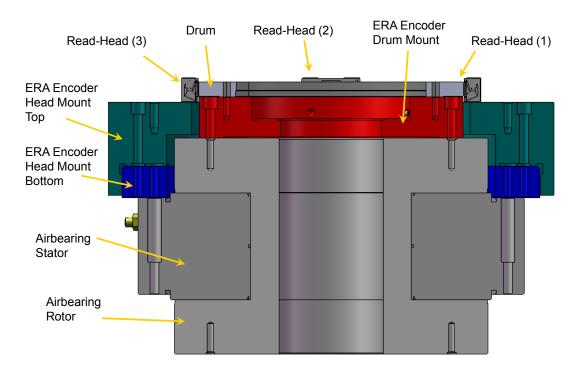

The ERA4282C does not have an integral bearing, meaning that the read-head and the drum are separate parts and need to be constrained with respect to each other using an independent bearing, such as the airbearing. To improve rotation measurement, four read-heads, which are equally spaced around the encoder drum, are used in the PRT design to obtain four simultaneous angle measurements based on a single rotating encoder drum. Figure 2-7 shows the read-heads' arrangement around the encoder ring. The cross-section view in Figure 2-8 shows how the encoder is mounted onto the air bearing. The red piece is used to attach the drum to the airbearing rotor and the green and the blue pieces are used together to fix the read-heads to the airbearing stator and position them around the drum.

Figure 2-7: ERA4282C read heads arrangement in the PRT design

Figure 2-8: Section-view of the ERA4282C encoder's mounting onto the airbearing

Centering and alignment of the encoders in the setup is very important because it directly influences the achievable rotation measurement accuracy. Any eccentricity of the

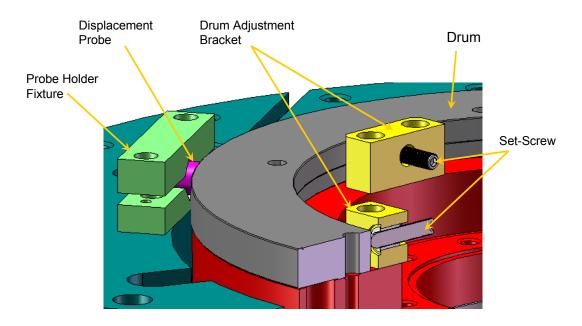

drum with respect to the rotor or any improper alignment of the read-heads to the drum would introduce rotation measurement error. As a result, mechanisms are included in the design to ensure centering and alignment accuracy to less than 0.1 µm. Figure 2-9 shows the centering mechanism used with the ERA encoder Drum. A capacitive displacement sensor looking at the outside of the drum is fixed by two V-groove fixtures. As the rotor rotates, the capacitive sensor measures the eccentricity of the drum. The measured eccentricity is corrected by adjusting the four finely threaded set screws, which push on the inside of the encoder drum through a flexible element. Each pair of opposing set screws constrains the drum in one translation degree of freedom. The flexible element enables finely adjusting the position by tightening one setscrew without the need for loosening its opposing setscrew. The two pairs together can adjust the center of the drum in the horizontal plane. The fine 100 threads/inch setscrews enable adjustment resolution of better than 700-nm per degree.

Figure 2-9: Section-view of the encoder drum adjustment mechanism

However, the experimental centering of the drum showed that tapping could be as effective as using the fine adjustment setscrews. An eccentricity of better than 300 nm was achieved using both the setscrew mechanism and tapping. The achievable centering was found to be limited by the roundness of the encoder drum's outer surface which was used as the centering target.

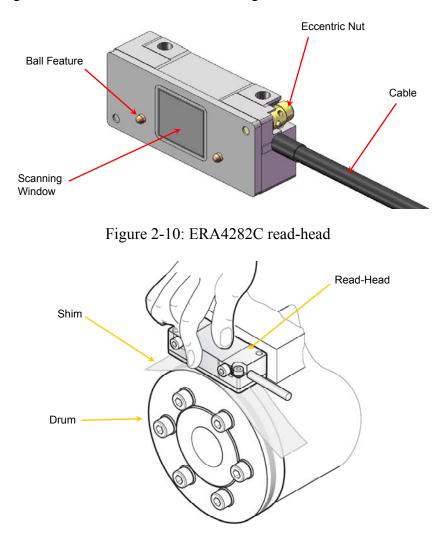

The read-head, shown in Figure 2-10, must be aligned properly to the encoder drum. The two ball features on the read-head are used with a shim to position the read-head at the right radius to the drum as shown in Figure 2-11.

Figure 2-11: Radial adjustment of the read-head for the ERA4282C encoder [17]

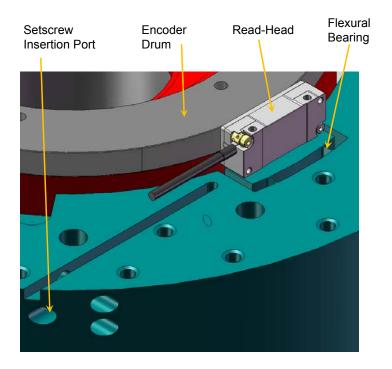

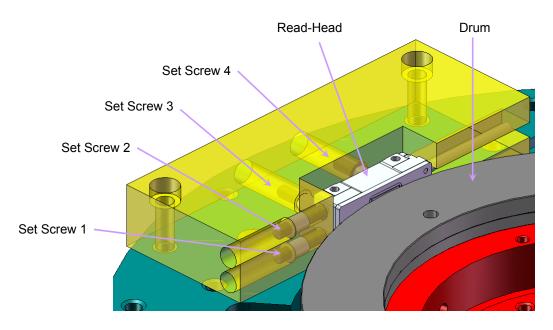

Still, the read-head needs to be adjusted tangent to the drum to match the phase of the output signals from the four read- heads. One method considered for tangential adjustment was to use a flexural bearing along with setscrews as shown in Figure 2-12. The two radial flexure leaves constrain five degrees of freedom of the read-head while allowing free tangential motion. Two setscrews from left and one setscrew from right help adjust and constrain the bearing supporting the read-head. The flexure method inevitably lowers the stiffness of the read-head's support. This is against the design goal to achieve a consistent and precise setup. As an alternative, a temporary fixture can be used to adjust the read-head tangent to the drum while constraining other movements. As shown in Figure 2-13, the fixture uses four set screws which push against the read-head. Using this fixture, the head can be moved tangentially while constrained in other degrees of freedom. To enable smoother adjustment, flexible rubber pads can be used in front of the setscrews and the head can be moved by preloading and compressing those pads. This will create a continuous and levered motion.

Finally, the eccentric nut built into the encoder read-head is used to adjust the sensing window of the read-head. Rotating the eccentric nut will rotate the sensing window around its normal axis and will move it in its plane at the same time. Throughout the adjustment process, the encoder signal is used as the feedback for aligning the read-head. The signal is viewed using an oscilloscope. The alignment adjustment pursues the following goals:

- 1. Maximize the individual read-head signals

- 2. Align the individual read-head incremental signal with its reference signal

- 3. Align the phase of the four read-heads' signals

Due to time constraints, so far, we have aligned one read-head using the two ballfeatures only. Inspecting the results, we found the alignment to be satisfactory.

Figure 2-12: Tangential adjustment of the read-head for the ERA4282C encoder – flexural bearing method

Figure 2-13: Tangential adjustment of the read-head for the ERA4282C encoder – rigid removable fixture method

## 2.2.2 Encoder with Integral Bearing

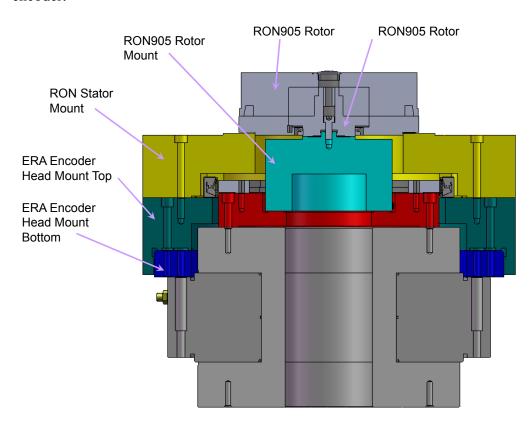

The second encoder selected for this setup is RON905 from Heidenhain which is shown in Figure 2-14. The RON encoder has an integral bearing which constrains the grating carrier to the scanning read-head; therefore, it appears as a single part with rotary and stationary sub-parts. The rotor is centered and fixed to the airbearing rotor, and the stator is centered and fixed to the airbearing stator. Internal flexures of the encoder allow its read-head to move relative to the housing to avoid over-constraint. The cross section view in Figure 2-15 shows the mounting design for the RON905 encoder. The RON Rotor Mount piece extends the rotor further to connect to the rotary part of the RON905 encoder. The Ron Stator Mount fixes the stationary part of the RON905 encoder to the stator trough the ERA encoder head mount pieces.

Figure 2-14: RON905 encoder from Heidenhain [courtesy of Heidenhain] [17]

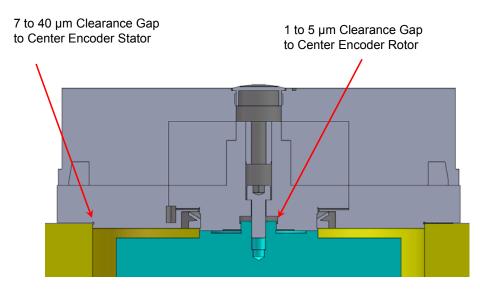

Similar to the ERA4282C encoder, the RON905 has alignment requirements that need to be ensured. In the PRT setup, the mounting pieces are centered to the rotor using a dial indicator. Once the mounting parts are centered to 10µm, clearance positional fits are used to center the RON encoder to the mounting pieces and hence to the airbearing

rotor. Figure 2-16 zooms on the section view to show the fits used for positioning the encoder.

Figure 2-15: Section-view showing the mounting of RON605

Figure 2-16: Section-view showing the fits used for centering the RON905 encoder

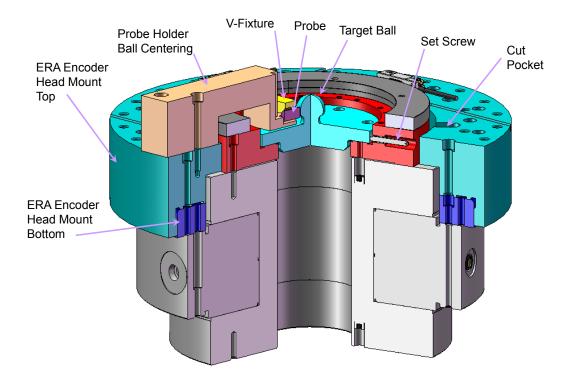

# 2.3 Ball-Probe Assembly

The ball-probe setup can be used to identify the spindle error motion in three translational degrees of freedom (DOF) at the center of the ERA4282C encoder drum. The error motion is significant because it influences the angular measurement accuracy. When a single encoder read-head is used, the airbearing's 25-nm radial error motion translates to 250 nano-radians at the encoder drum read-out. The ball probe setup consists of a precision machined target ball with a roundness of about 10-nm, which is centered onto the rotor, and three displacement sensors which look at the ball in the three orthogonal directions. Figure 2-17 shows the cross section view of the ball probe setup.

Figure 2-17: Section-view of the ball-probe setup

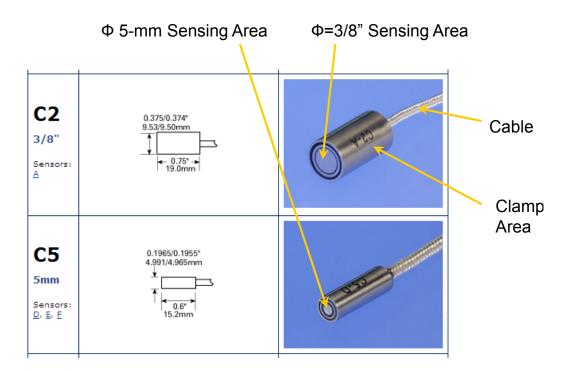

## 2.3.1 Capacitive Probes

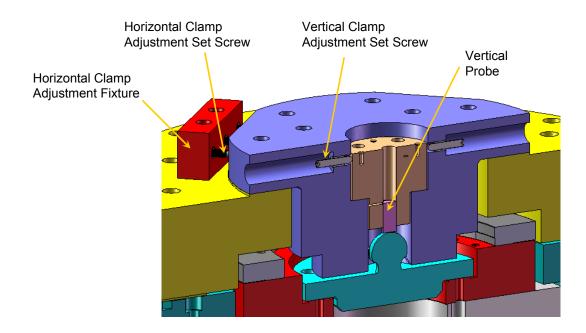

The capacitive displacement sensors are used for measuring the motion of the target ball. The cylindrical shaped probes are shown in Figure 2-18. The vertical error motion does not affect the rotation measurements directly, and hence, has lower precision requirements compared to the horizontal probes. As a result a probe with a larger range but lower resolution is selected for the vertical direction. The vertical probe is slightly larger than the two horizontal probes. The probe holder pieces fix the probes to look at the target ball. Each probe is secured inside a cylindrical clamp built into the probe holder pieces. The probes need to be aligned to look at the equator of the ball. Also, the probes are designed to work at specific distance from the target; therefore, the gap between the probes and the ball needs to be adjusted. Figure 2-19 shows the adjustment mechanism for the probes.

Figure 2-18: Vertical (top) and horizontal (bottom) Lion Precision capacitive probes

Figure 2-19: Section view showing the probe alignment mechanisms

To adjust the gap spacing of the horizontal probes, four Horizontal Clamp Adjustment Fixtures are temporarily added to the setup. Each adjustment fixture will have three set screws which push on the sides of the horizontal clamp. Each two opposing adjustment fixtures enable adjustment and firm constraint of one horizontal probe. The gap spacing of the vertical probe is adjusted by moving the probe inside the vertical clamp. For aligning the horizontal probes to the equator the design relies on the vertical tolerances of the parts and can use precision metal shims between the purple *horizontal probe holder* and the yellow *RON stator mount* as a backup plan. Aligning the vertical probe to the ball center is done by using the four set screws placed every 90-degree around the vertical clamp. The four set screws can be used to move and constrain the probe to point at the equator of the target ball.

### 2.3.2 Precision Target Ball

The precision machined ball is used as a target to monitor the error motion of the spindle. The target ball, manufactured by Professional Instruments, is 1-inch in diameter and has a nominal roundness of 10-nm or better if used with capacitive probe sensors. It is necessary to center the ball because any eccentricity of the ball relative to the rotor will show up as a rotation synchronous component on the error motion measurements. Figure 2-20 shows the centering mechanism. A capacitive probe sensor, held in place by a probe holder fixture and V-shaped clamp, is used to identify eccentricity of the ball. The identified eccentricity is corrected by using the set screws which push against the base of the target ball. The four setscrews in the design enable adjustment of the ball center in the horizontal plane. The pockets cut into the top ERA Encoder Head Mount enable adjustment of the setscrews without having to remove the ERA Encoder Head Mount.

Figure 2-20: Section-view showing the centering mechanism for the target ball

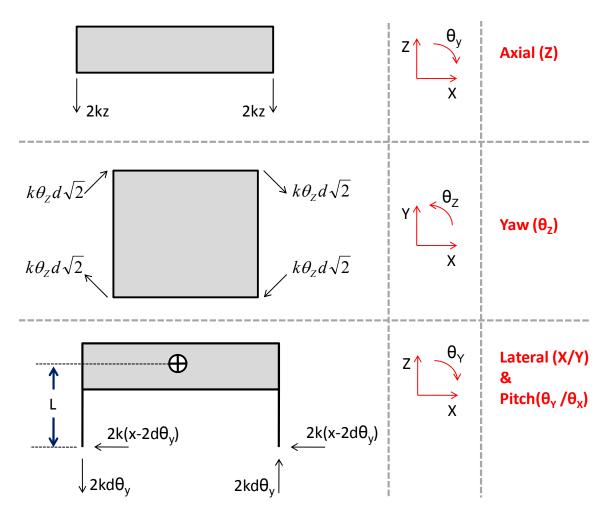

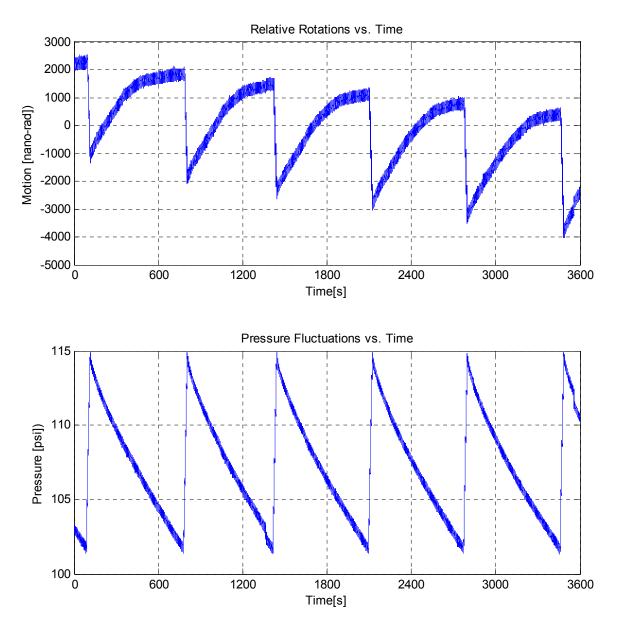

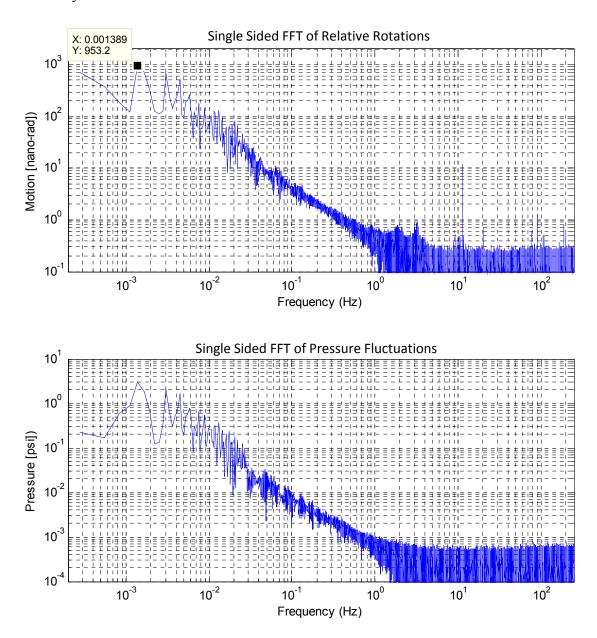

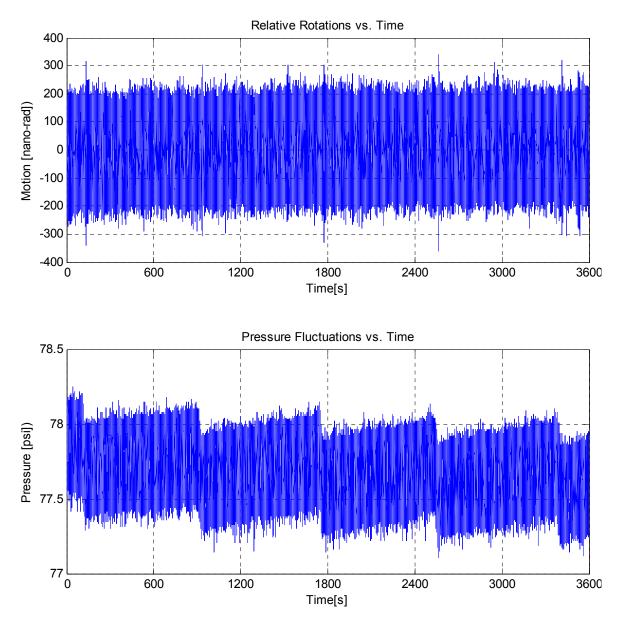

As discussed in the previous section, the capacitive displacement sensors can achieve sub nanometer resolution. However, the target ball's 10-nm roundness limits motion detection resolution to  $\pm 10$  nm. The ball roundness error can be identified using reversal methods. The generated roundness calibration map can be used to compensated for the roundness error of the ball and improve the displacement measurement resolution. To perform the reversal technique the probes need to be adjusted precisely in rotation with respect to the airbearing stator. While moving the probes relative to the stator, it is important that everything else in the setup stays the same. Therefore, it is required to move the probes in the assembled setup. To avoid changing the probe to ball gap, which could introduce error due to non-linearity of the probes, and to avaoid damaging the target ball, we have incorporated a sliding bearing into the design which enables us to rotate the probes without moving them off the spindle center.