# Fast Design Space Exploration for Low-Power Configurable Processors

by

#### PETER HALLSCHMID

M.A.Sc., University of British Columbia, 2003 B.Eng., University of Victoria, 1999 B.Sc., University of Victoria, 1996

# A THESIS SUBMITTED IN PARTIAL FULFILMENT OF THE REQUIREMENTS OF THE DEGREE OF

#### DOCTOR OF PHILOSOPHY

in

The Faculty of Graduate Studies

(Electrical and Computer Engineering)

# UNIVERSITY OF BRITISH COLUMBIA (Vancouver)

**July 2008**

© Peter Hallschmid, 2008

#### **Abstract**

Customizable and extensible processors (commonly known as "configurable processors" or ASIPs) can provide the flexibility of off-the-shelf processors with a performance closer to that of custom logic. Manual configuration of an ASIP requires highly-specialized knowledge of computer architecture and typically results in sub-optimal architectures leading to poor performance and higher costs. Ideally, the ASIP flow should be entirely automated; however, optimal solutions are only guaranteed with an exhaustive search of the design space. Unfortunately, an exhaustive search is computationally prohibitive and so the research community continues to study ways to find "good" solutions within a reasonable time.

This dissertation presents new methods of design space exploration and fast architecture evaluation. These methods are intended to improve the automation and usability of ASIPs. Design space exploration is conducted using a novel approach where the design space is modeled using a small sample of points. Each sample point evaluation is expensive; however, the design space model can then be used to quickly estimate all other points in the space. Non-parametric statistics are used to construct the model and, consequently, the precise nature of the design space need not be specified a priori. This approach provides a computationally-efficient alternative to existing optimization heuristics with additional benefits that provide easy discovery of architectural trends and tradeoffs.

Experiments were conducted using the proposed modeling approach to configure both the branch prediction unit (BPU) and the cache hierarchy of an embedded processor. Results showed that the approach could achieve a 100x speedup while providing near optimal configurations.

In addition, a fast performance estimation approach is proposed for evaluating configurations of instruction-set extensions. This approach considers pipeline effects and consequently improves the quality of results over existing approaches. This improvement is achieved while maintaining constant run-time complexity.

### **Table of Contents**

| Abstract                                   | ii   |

|--------------------------------------------|------|

| Table of Contents                          | iii  |

| List of Tables                             | vii  |

| List of Figures                            | viii |

| List of Abbreviations                      | x    |

| Acknowledgements                           | xi   |

| Chapter 1: Introduction                    | 1    |

| 1.1. MOTIVATION                            | 1    |

| 1.2. RESEARCH GOALS AND CHALLENGES         | 7    |

| 1.3. THESIS ORGANIZATION                   | 8    |

| Chapter 2: Background                      | 10   |

| 2.1. Overview                              | 10   |

| 2.2. CUSTOMIZABLE PROCESSORS / ASIPS       | 10   |

| 2.2.1. Configurability                     | 10   |

| 2.2.2. Customizable Processors             | 12   |

| 2.2.3. ASIP Methodologies                  | 13   |

| 2.3. BASE ARCHITECTURES FOR ASIPS          | 18   |

| 2.3.1. Embedded Processors                 |      |

| 2.3.2. ARM7TDMI                            | 19   |

| 2.3.3. StrongARM SA-110                    |      |

| 2.4. DESIGN OBJECTIVES                     | 20   |

| 2.4.1. Instruction Level Parallelism (ILP) | 20   |

| 2.4.2. Damer                               | 21   |

| 2.4.3. ASIPs and Power                                |     |

|-------------------------------------------------------|-----|

| 2.5. ARCHITECTURAL PARAMETERS                         | 27  |

| 2.5.1. Motivation for Configuring the "Front-end"     | 27  |

| 2.5.2. Branch Prediction                              | 28  |

| 2.5.3. Cache Hierarchy                                | 29  |

| 2.6. DESIGN METHODOLOGIES                             | 32  |

| 2.6.1. Design Space Exploration (DSE)                 | 32  |

| 2.6.2. Instruction Set Extensions                     | 37  |

| Chapter 3: Optimization via Design Space Modeling     | 40  |

| 3.1. Introduction                                     | 40  |

| 3.2. RELATIONSHIP TO PREVIOUS METHODS                 | 42  |

| 3.2.1. Spatial versus Temporal Sampling               | 42  |

| 3.2.2. Relationship to Heuristic Approaches           | 43  |

| 3.3. MODELING PARADIGM                                | 46  |

| 3.3.1. Design Space Definition                        | 46  |

| 3.3.2. Methods of Sampling Points                     | 46  |

| 3.3.3. Model Construction                             | 48  |

| 3.3.4. Optimization                                   | 49  |

| 3.4. CONSTRUCTION APPROACHES                          | 50  |

| 3.4.1. Manual Regression Approach                     | 50  |

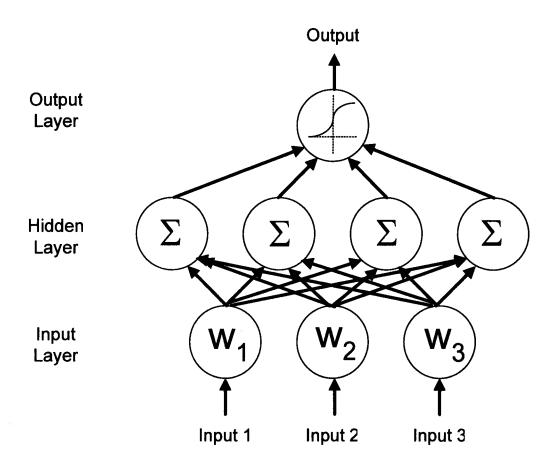

| 3.4.2. Artificial Neural Networks Approach            | 52  |

| 3.4.3. Manual Decomposition Approach                  | 55  |

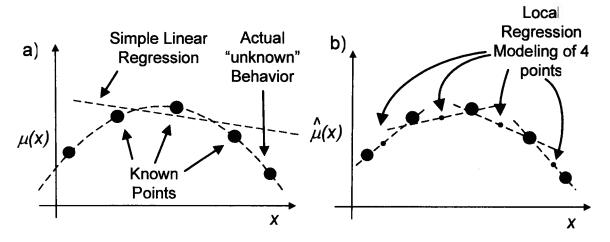

| 3.4.4. Non-Parametric Regression Approach             | 55  |

| 3.5. EXAMPLE: MANUAL DECOMPOSITION APPLIED TO THE BPU | 58  |

| 3.5.1. Overview                                       | 58  |

| 3.5.2. Branch Prediction                              | 59  |

| 3.5.3. Measuring Aliasing via Simulation              | 62  |

| 3.5.4 Model Construction                              | 6.1 |

| 3.5.5. Experimental Platform                                      | 69           |

|-------------------------------------------------------------------|--------------|

| 3.5.6. Results                                                    |              |

| 3.6. SUMMARY                                                      | 74           |

| Chapter 4: Application of Non-parametric Design Space Modeling to | Architecture |

| Exploration                                                       | 76           |

| 4.1. Introduction                                                 | 76           |

| 4.2. LRM-DSE                                                      | 76           |

| 4.2.1. Overview                                                   | 76           |

| 4.2.2. Local Regression Basics                                    | 78           |

| 4.2.3. Point Selection                                            | 82           |

| 4.2.4. Quality of Fit                                             | 83           |

| 4.2.5. LRM-DSE Configuration Methodology                          | 84           |

| 4.3. Example: Tuning the Cache Hierarchy                          | 87           |

| 4.3.1. Cache Hierarchy                                            | 87           |

| 4.3.2. Tuning the Cache using LRM-DSE                             | 89           |

| 4.3.3. Experimental Platform                                      | 90           |

| 4.3.4. Results                                                    | 91           |

| 4.4. Conclusions                                                  | 95           |

| Chapter 5: Fast Evaluation of Instruction-Set Extensions          | 97           |

| 5.1. Introduction                                                 | 97           |

| 5.2. ENUMERATION AND SELECTION                                    | 102          |

| 5.2.1. Problem Definitions                                        |              |

| 5.2.2. Performance Estimation (the Simple Predictor)              | 104          |

| 5.3. PREDICTING THE IMPACT OF HAZARDS                             | 105          |

| 5.3.1. Considering Data Hazards                                   |              |

| 5.3.2. Proposed "Hazard-Aware" Predictor                          |              |

| 5.4. Experimental Platform                                        | 111          |

| 5.5. RESULTS                                              | 113 |

|-----------------------------------------------------------|-----|

| 5.5.1. Accuracy of the Performance Predictor              | 113 |

| 5.5.2. Effects of Data-Hazards on Enumeration & Selection | 115 |

| 5.6. CONCLUSIONS                                          | 116 |

| Chapter 6: Conclusions                                    | 118 |

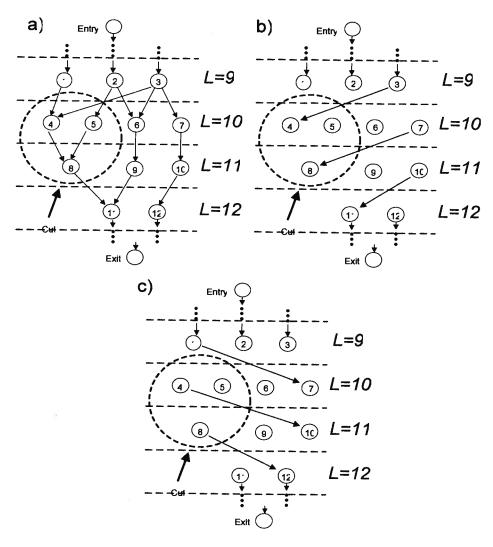

| 6.1.1. Research Summary                                   | 119 |

| 6.1.2. Limitations                                        | 123 |

| 6.1.3. Future Work                                        | 123 |

| References                                                | 126 |

### **List of Tables**

| Table 3.1: Comparison of various model construction approaches                              |

|---------------------------------------------------------------------------------------------|

| Table 3.2: Base processor specifications of the StrongARM processor69                       |

| Table 3.3: The correlation coefficient (R <sup>2</sup> ) for all least square regressions72 |

| Table 3.4: Power reduction after using the proposed configuration approach for GSelect      |

| and Bimodal73                                                                               |

| Table 4.1: The dimensions of the design space resulting in 19,278 configurations 89         |

| Table 4.2: The power reduction due to LRM-DSE for random and evenly distributed             |

| sampling                                                                                    |

| Table 4.3: LRM-DSE and optimal configurations are compared for four benchmarks with         |

| parameters that differ underlined                                                           |

| Table 5.1: Error in execution time per block as predicted by the "hazard-aware"             |

| estimator114                                                                                |

# **List of Figures**

| Figure 1.1: Comparison of Processors, FPGAs, ASICs, and custom devices                       |

|----------------------------------------------------------------------------------------------|

| Figure 1.2: Hypothetical application domains for custom and general-purpose devices 5        |

| Figure 2.1: Classification of configurable platforms                                         |

| Figure 2.2: General ASIP Configuration Methodology                                           |

| Figure 2.3: General parallelization of a logic function                                      |

| Figure 2.4: Parallelism-related versus Fixed-rate Power Dissipation                          |

| Figure 2.5: Y-chart representation of the separation of concerns for design space            |

| exploration                                                                                  |

| Figure 3.1: Hypothetical 1-D and 2-D design space models                                     |

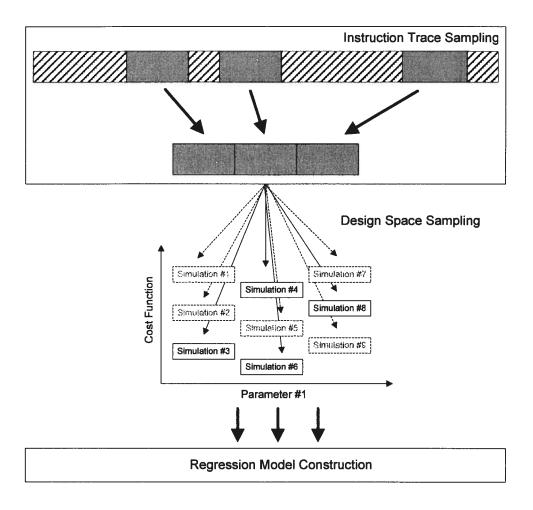

| Figure 3.2: DSE using an approach with combined spatial and temporal sampling45              |

| Figure 3.3: A typical artificial neural network                                              |

| Figure 3.4: (a) Simple Parametric Linear Regression (b) LOESS-based approach 56              |

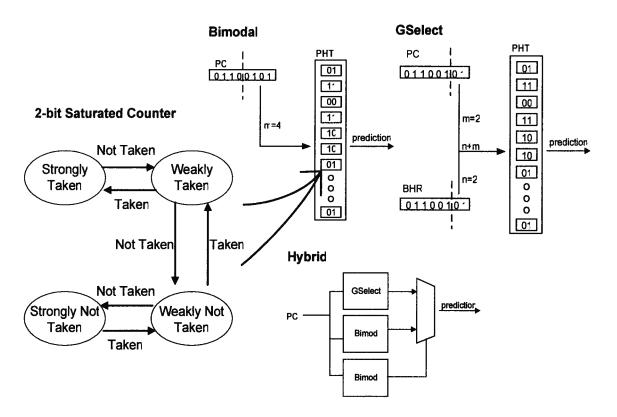

| Figure 3.5: The Bimodal, GSelect, and Hybrid Branch Predictors                               |

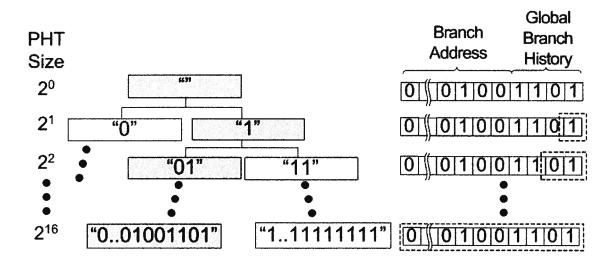

| Figure 3.6: Data structure used to collect aliasing statistics for all PHT configurations in |

| parallel63                                                                                   |

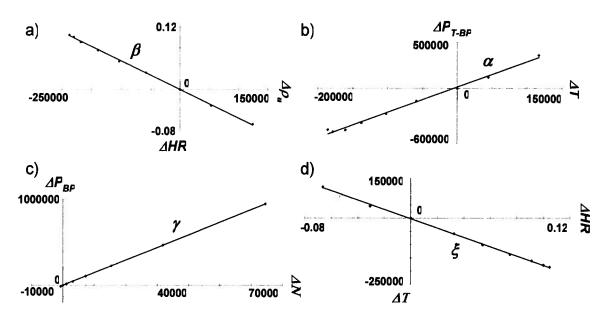

| Figure 3.7: Linearity of regression coefficients, $\alpha$ , $\beta$ , $\xi$ , and $\gamma$  |

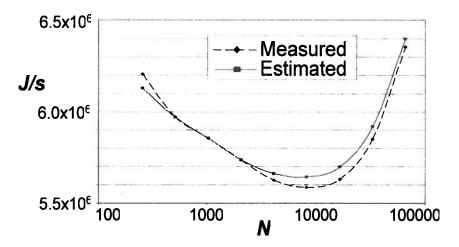

| Figure 3.8: Estimated and measured total power dissipation for the gcc                       |

| Figure 3.9: Flow used to run experiments on BPU configuration. Solid arrows represent        |

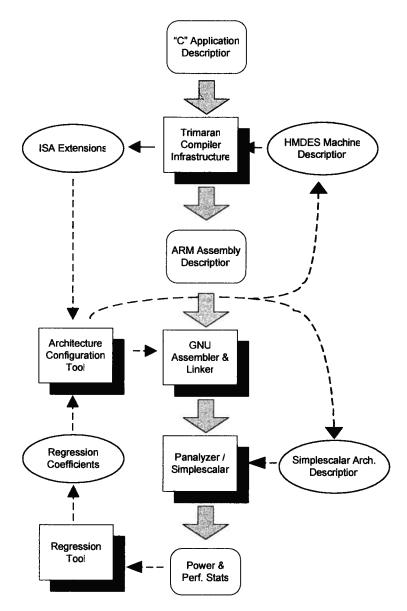

| the sequence of steps used in the standard flow. Dashed arrows represent the additional      |

| steps introduced to add configurability70                                                    |

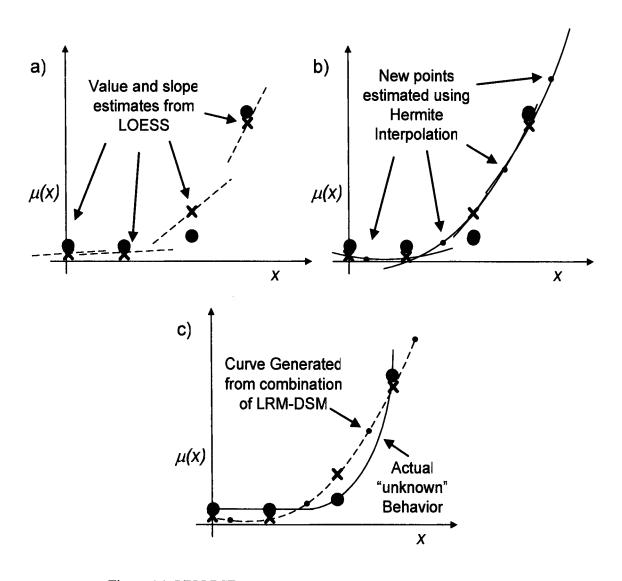

| Figure 4.1: LRM-DSE uses both LOESS and Hermit Interpolation                                 |

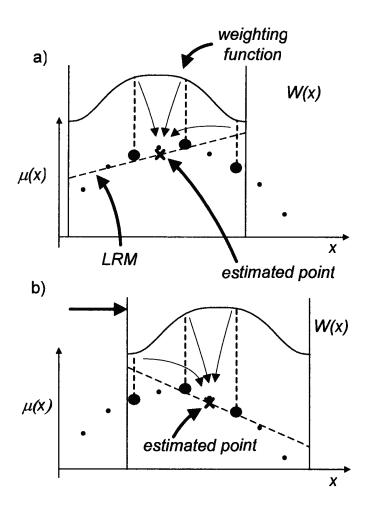

| Figure 4.2: The regression window is shifted from left to right for different points being |

|--------------------------------------------------------------------------------------------|

| estimated81                                                                                |

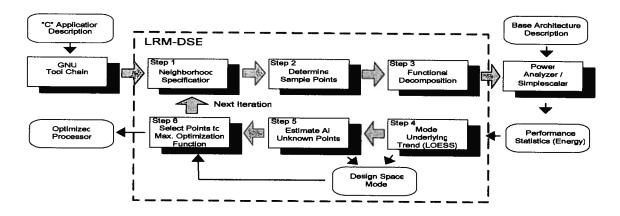

| Figure 4.3: The LRM-DSE experimental flow incorporating LRM-DSE90                          |

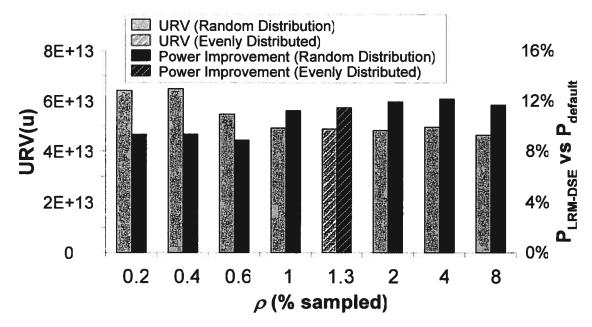

| Figure 4.4: $URV(\mu)$ and percentage power improvement for different sampling densities.  |

| 92                                                                                         |

| Figure 5.1: (a) Pattern Enumeration, (b) Instruction Selection, and (c) Instruction        |

| Mapping                                                                                    |

| Figure 5.2: FU-to-FU forwarding (only one input is shown for simplicity)100                |

| Figure 5.3: The schedule of a basic block (a) before and (b) after adding a custom         |

| instruction                                                                                |

| Figure 5.4: A DAG representation of a basic block (a) partitioned according to levels of   |

| dependency, (b) with worst case dependencies, and (c) with best case dependencies 107      |

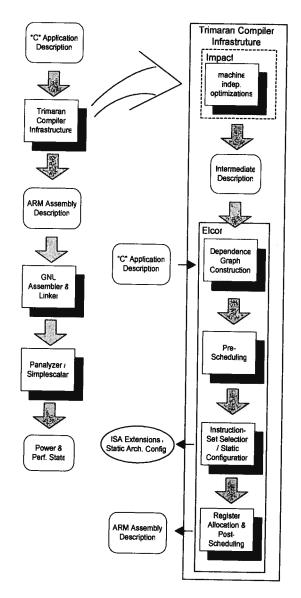

| Figure 5.5: The Trimaran flow with modifications for ISEs                                  |

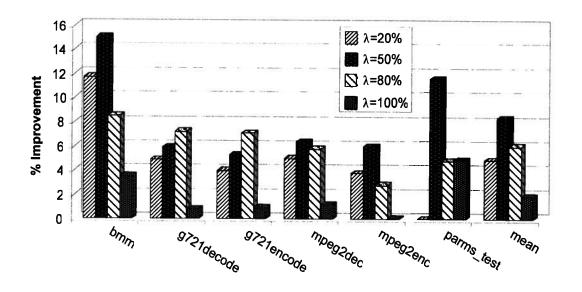

| Figure 5.6: Improvement in ISEs due to the "hazard-aware" predictor                        |

#### List of Abbreviations

ADL Architecture Description Language

AMBA Advanced Microcontroller Bus Architecture

ANN Artificial Neural Network

ASIC Application Specific Integrated Circuit

ASIP Application Specific Instruction-set Processor

BPU Branch Prediction Unit

CAD Computer-Aided Design

DAG Directed Acyclic Graph

DSE Design Space Exploration

DT Design Technology EP Embedded Processor

EPIC Explicitly Parallel Instruction Computing

FPGA Field Programmable Gate Array

FU Functional Unit

GPP General Purpose Processor

HDL Hardware Description Language ILP Instruction Level Parallelism

IP Intellectual Property

ISA Instruction Set Architecture ISE Instruction Set Extension

ITRS International Technology Roadmap for Semiconductors

LOESS LOcally wEighted Scatterplot Smoothing

LRM-DSE Local Regression Modeling-based Design Space Exploration

NRE Non-Recurring Engineering

PHT Pattern History Table

PT Process Technology

SoC System-on-Chip

SoC-PE Power-Efficient System-on-Chip

TLB Translation Lookaside Buffer

VLIW Very Long Instruction Word

#### **Acknowledgements**

This thesis would not have been completed without the help of many great people who made my life at UBC an enjoyable and enlightening experience.

I would first like to thank my supervisor, Dr. Resve Saleh, for the incredible opportunity. His passion for research, dedication to teaching, and wisdom in dealing with others, has mentored me throughout my degree. On countless occasions, he has gone far beyond the call of duty as a supervisor.

I am also grateful to all the other professors of the SoC research Lab for learning something from all of them. I would especially like to thank Dr. Steve Wilton, Dr. Guy Lemieux, Dr. André Ivanov, Dr. Mike Feeley, and Dr. Alan Hu, for serving on my committee and for their support throughout the years.

I would also like to thank past and present student members of the SoC lab for their support. I especially thank Victor Aken'Ova, Brad Quinton, Sohaib Majzoub, Julian Lamoureux, Pedram Samini, Dipanjan Sengupta, Mohsen Nahvi, Marvin Tom, David Yeager, and Zahra Ebadi. I would also like to thank the always helpful staff of the SoC lab, Roberto Rosales, Roozbeh Mehrabadi, and Sandy Scott.

Last, but certainly not least, I would like to thank my loving wife May and my children who have been extremely supportive throughout all of my work. I would also like to thank my father, mother and the rest of my family for the tremendous love and support they have shown me my entire life.

## In Loving Memory of my father

*Dr. Claus August Hallschmid*17/10/41 – 17/05/06

#### **Chapter 1: Introduction**

#### 1.1. Motivation

Embedded systems are special-purpose designs intended for a specific application or set of applications and with specific design constraints (i.e., speed, power consumption, cost, reliability, usability, etc.). Such systems are typically embedded in mechanical or electrical hardware as part of a system deployed in the field. Applications for embedded systems include PDAs, cell phones, MP3 players, traffic control systems, guidance systems and medical instrumentation, to name a few. With a growing market demand for communications and portability, the use of embedded systems has grown correspondingly.

The cost of designing embedded systems and their constituent components has increased in a similar manner for several key reasons. First, the size of circuits has grown according to Moore's law which states that the number of transistors in an integrated circuit doubles every 18 months [1]. Also, deep-submicron effects are contributing to the rising costs because they make design more difficult on a per transistor basis. It has been predicted that if it were not for the CAD innovations developed to date, the average design costs of a *power-efficient system-on-chip (SoC-PE)* would be in the order of \$900M rather than the current \$20M [2]. The International Technology Roadmap for Semiconductors (ITRS) emphasizes that the current pipeline of CAD innovations must continue otherwise design costs will quickly become prohibitive [2].

While designs have become more complex, engineers have also become more productive in part due to increasingly more sophisticated CAD tools and methodologies.

In spite of this, a design trend known as the *productivity gap* continues to widen where design complexity continues to outpace the ability of engineers to meaningfully design them. To make matters worse, market pressures have steadily reduced the acceptable time-to-market. Designers have a reduced design window and a lowered tolerance for design revisions. This forces companies to incur the costs of additional engineers to help meet deadlines.

One approach to reducing development costs is to use System-on-Chip (SoC) methodologies. An SoC integrates pre-verified and pre-qualified intellectual property (IP) components onto a single chip. Design time is reduced through the use of off-the-shelf IP while performance is greatly improved over multi-chip solutions.

A central component of an SoC is the embedded processor which adds programmability to the system. With programmability, the system can be reused for a variety of applications, thus amortizing the cost of design and manufacturing. A design with programmability provides a lower risk and shorter time-to-market implementation path; however, increased flexibility generally comes with a power, speed, and area/cost overhead.

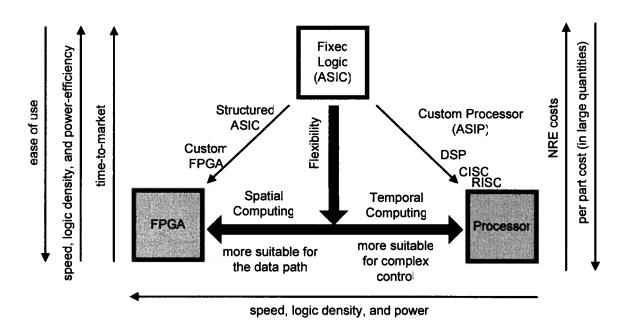

The likely trend for future SoCs will be an increase in the number of on-chip processors and other forms of programmability (i.e., Field Programmable Gate Arrays (FPGAs)). Figure 1.1 illustrates some of the key differences between processors, FPGAs and their fixed-function equivalent known as an *Application Specific Integrated Circuit (ASIC)*. Processors and FPGAs are both configurable devices, but they achieve configurability in very different ways. At one extreme, processors are configurable platforms that implement "temporal" computing and are programmed via software.

Processors are more suitable for complex state machines. At the other extreme, FPGAs implement "spatial" computing and are programmed via programmable look-up tables and programmable interconnect. FPGAs are more suitable for data-path applications where speed, logic density, and power are more important. A typical rule-of-thumb is that an FPGA is an order of magnitude faster, more dense, and more power efficient than the equivalent software running on a processor [3].

Figure 1.1: Comparison of Processors, FPGAs, ASICs, and custom devices.

The vertical axis in Figure 1.1 represents the degree to which the device is configurable (i.e., flexibility). Programmable devices are generally easier to implement, have a faster time-to-market, lower risk, and lower NRE costs than the equivalent ASIC implementation [4]. On the other hand, they are slower, less dense, consume more power, and have a higher per part cost in larger quantities.

A customizable device is inherently programmable but has some aspects of its architecture tailored to a specific application or application domain. In doing so, these devices maintain many of the advantages of programmability such as reduced costs, reduced risk, and faster time-to-market. At the same time, they benefit from improved performance thus closing the gap between programmability and fixed implementations. This compromise between programmable implementations and fixed implementations is evident in Figure 1.1 where customizable processors and customizable FPGAs have been included.

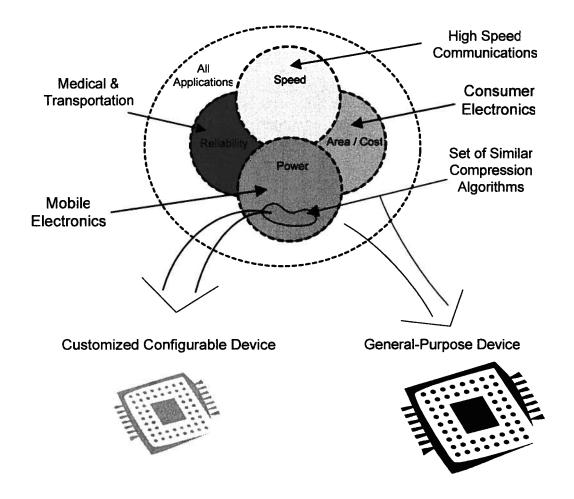

A disadvantage to customizable devices is that they are no longer suitable for as wide a range of applications as for general purpose processors (GPPs). This is illustrated in Figure 1.2 where the set of all applications is shown with several sub-domains labeled for applications with particular speed, density, power, and reliability requirements. In this example, a device has been customized to work best for a specific domain within lower-power applications (i.e. a hypothetical set of similar compression algorithms).

Thus far, we have discussed customizable devices in general; however, the scope of this dissertation is on customizable or configurable processors, so it is useful to understand the key difference between embedded processors (EPs) and GPPs. EPs are intended to be run on a few applications which are known at design time whereas GPPs run a wide variety of applications which are chosen by the end-user. Because we have knowledge of the intended applications at design time, significant performance gains can be made by customizing the EP to the applications. As a result, the system designer only adds what is needed to the processor and can tailor components to precise specifications in order to meet area, speed, and power goals. In fact, customizable processors have

been shown to result in performance gains of 1.12x to 11.3x over general-purpose processors [5].

Figure 1.2: Hypothetical application domains for custom and general-purpose devices.

In the industry, customizable processors are commonly referred to as "configurable processors", or Application-Specific Instruction-Set Processors (ASIPs). To date, industrially-available ASIPs such as Tensilica Xtensa [6], ARCtangent [7], MIPS32 M4K [8], and Altera Nios/Nios II [9] have a base architecture with only a limited set of customizable parameters. Aside from these parameters, many other aspects of the architecture have a significant impact on performance and energy-efficiency but are normally fixed as prescribed by the base architecture. One goal of this research is to

determine the proper settings of key parameters of the processor front-end to customize for reduced power.

Currently-available ASIPs are difficult to use because effective customization requires advanced knowledge of processor architecture. Even if a user were to have indepth knowledge of computer architecture, it is difficult to manually find an optimal configuration due to the complex manner by which parameters interact. With this in mind, the work in this research focuses on methods of automatically tuning the architectural parameters to meet specific design goals while adhering to design specific design constraints.

A major difficulty in automatic customization of ASIPs is that a large solution space may be defined by the parameter set. Even with only a few parameters, exhaustive methods for exploring the solution space quickly become intractable due to a "combinatorial explosion." There are three orthogonal approaches to solving this. First, the solution space can be "pruned" using design constraints. Second, sophisticated heuristics can be used to minimize the time required to explore the design space. Third, fast evaluation techniques can be use to minimize the time needed to evaluate each point visited during exploration. The latter two approaches will be addressed within this dissertation.

This dissertation focuses on customizability of the front-end of the processor because of its impact on *instruction level parallelism (ILP)* and its significant contribution to both power and area. Henceforth, the combined fetch, decode, and memory hierarchy shall be referred to as the "front-end" of the processor. Improvements in ILP through front-end improvements typically come with a penalty of increased

hardware (cache, buffers, and history look-up tables), all of which add significant power consumption in addition to that of the main memory. The trend for memory hierarchy is towards increased size because of the growing gap between memory and processor performance [10]. It is for these reasons that this dissertation focuses on the configuration of several key aspects of the front-end; in particular, it focuses on cache and branch prediction.

The primary design objective in this research is to reduce power. In both academia and industry, power has become the main focus of research and development for both embedded and high-performance processors. For embedded processors, reduced power consumption extends the battery life of mobile devices such as laptops and cell phones. For high-performance processors, reduced power consumption helps reduce power-density problems and related cooling costs.

#### 1.2. Research Goals and Challenges

Having described the motivation and background for the research, a succinct thesis statement is as follows: to investigate methods to improve the automation of customizable processors in order to make them more accessible to system-level designers. The following research objectives where identified for this work:

To develop an efficient methodology for design space exploration. This method

would be used for both optimization and assessing trade-offs and trends between

parameters and design objectives. Further, this method should require only a

minimal set of simulations and the user should not require in-depth knowledge of

the design space.

- 2. To develop fast estimation techniques for evaluating candidate configurations when extending the instructions of a base instruction set.

- 3. To apply the proposed methods to the customization of industry-standard embedded processors using well-recognized benchmarks suites. The primary design objective will be power reduction. All techniques will be incorporated into an existing compiler and simulation flow to demonstrate the advantages and limitations of the new methods.

#### 1.3. Thesis Organization

In Chapter 2, a brief overview is provided on embedded processors and ASIPs. In addition, an overview of previous work is described for key components of the frontend including branch prediction, cache management, and instruction-set extensions. Background is given on the design goals and base architecture used to perform experiments. Research described in this thesis has some overlap with previous work from the high-performance general-purpose processor community, the low-power embedded processor community, and the configurable processor community.

In Chapter 3, a Design Space Exploration (DSE) optimization methodology is proposed based on modeling of the design space and is called Design Space Modeling. First, motivations for modeling the design space are discussed. Second, a comparison is made between Design Space Modeling and existing path-oriented heuristics and instruction trace sampling approaches. Third, the methodology is outlined in detail with a comparison of four modeling variants. The first of these variants (called *Manual Decomposition*) is a first attempt at modeling the design space. This variant provides excellent results; however, construction of the model requires considerable manual effort

and is therefore not scalable. The shortcomings of this method help to motivate the second modeling variant that also offers accurate models but is fully automated. This variant is a major contribution of the thesis and is discussed in detail in Chapter 4. The last two variants were developed by other research groups concurrently with this dissertation. To conclude the chapter, Manual Decomposition is applied to an example problem where the processor's branch prediction unit (BPU) is configured. This example is small enough to illustrate many of the concepts but complex enough to gain insight into the difficulties of the approach.

Chapter 4 proposes a non-parametric regression-based variant of Design Space Modeling. The advantage to this approach is that it is fully automated and that the class of functions required to perform the statistical fit need not be specified *a priori*. A detailed description of the approach is discussed. It is applied to the configuration of a 2-level cache hierarchy.

Chapter 5 discusses ways to improve the speed of customizing an Instruction-Set Architecture (ISA) using fast performance estimation. In this chapter, a general methodology for adding custom instructions (Instruction Set Extensions or ISEs) is introduced and includes a description of the current speed, power, and area estimation techniques. Because existing approaches do not account for data hazards, a novel "hazard-aware" estimation approach is proposed. This approach is evaluated by comparing it to existing approaches through experiments conducted using a modified ISE experimental flow.

Chapter 6 provides conclusions and directions for future work.

#### **Chapter 2: Background**

#### 2.1. Overview

In this chapter, background information is provided beginning with a description of ASIPS in Section 2.2. Then, Section 2.3 discusses the base processor architectures used. Section 2.4 discusses the primary design objectives which include *instruction-level* parallelism (ILP) and power efficiency. Section 2.5 provides background information on the architectural parameters to be configured. Finally, Section 2.6 provides background information on the two methodologies addressed which includes design space exploration and instruction set extensions.

#### 2.2. Customizable Processors / ASIPs

#### 2.2.1. Configurability

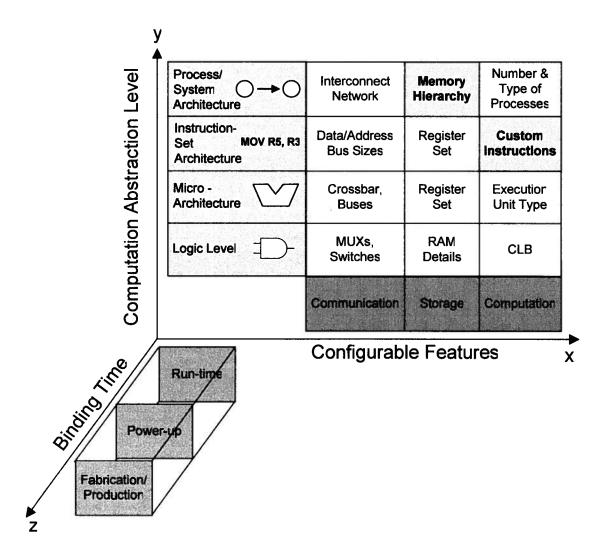

A detailed classification of configurable platforms is shown in Figure 2.1. It is composed of the three dimensions of *Compute Abstraction Level*, *Binding Time*, and *Reconfigurable Feature*. Compute Abstraction Level is the level of configurability presented to the user and can vary from system-level configurability to logic-level configurability. This dimension is shaded on the y-axis in Figure 2.1.

The binding time refers to the time at which the platform is configured. For some platforms such as Tensilica Xtensa [6] and Actel Axcellerator [11], the configuration is set at production/fabrication time. Other platforms, such as the FPGAs available through Xilinx [12] and Altera [9], are configured at start-up. Still others, such as GARP [13] and Chimaera [14], can be configured as many times as needed at run-time. Platforms

with production, start-up and run-time configurability are often referred to as configurable, reconfigurable, and dynamically reconfigurable, respectively. In this thesis, platforms with production-time binding are referred as *customizable platforms*. This dimension is shaded along the y-axis in Figure 2.1.

The configurable dimension is shaded along the x-axis in Figure 2.1 and includes communication elements, storage elements, and computational elements. This dimension represents the manner in which the platform supports configurability.

Figure 2.1: Classification of configurable platforms (adapted from [15] and [16]).

Example architectural features are shown in Figure 2.1 for the space defined by the compute abstraction level and reconfigurable features dimensions. Two examples in this table that will be discussed later in this dissertation are the bold blocks. One of these is the memory hierarchy which is a system level issue when sizing is performed. The other example is instruction customization which is an ISA level issue. As will be discussed in subsequent chapters, the work in this dissertation focuses on configurable devices with binding times at fabrication/production.

#### 2.2.2. Customizable Processors

An application-specific instruction set processor (ASIP) is a processing element that can be customized for a particular application domain [17,18]. The ASIP design flow allows system designers to build processors that can execute code faster while using less power than off-the-shelf processors. This avoids expensive and risky development of a fully custom processor or Application-Specific Integrated Circuit (ASIC). Previous studies have shown improvements from 1.12x to 11.3x over general-purpose processors [5]. Using these processors, designers can tune the instruction set architecture, optimize the pipeline, or add new data components for critical code segments in specific applications.

ASIPs come either in the *soft* or *hard* form. A soft ASIP is implemented on an FPGA and its binding time is at power-up. Industrially available soft ASIPs include Altera Nios/Nios II [9] and Xilinx MicroBlaze [12]. A hard ASIP is one for which the binding time is at fabrication time and is implemented using a standard cell flow like an ASIC. Industrially available ASIPs of this form include Tensilica Xtensa [6], ARC tangent [7], MIPS32 M4K [8] and Improv Jazz [19].

ASIP methodologies use compiler analysis, directed profiling, and design automation techniques to transform a base architecture to one that is optimized for a particular application or application domain. This allows the processor to take advantage of particular regularities in control and data behavior, and common clusters of operations.

#### 2.2.3. ASIP Methodologies

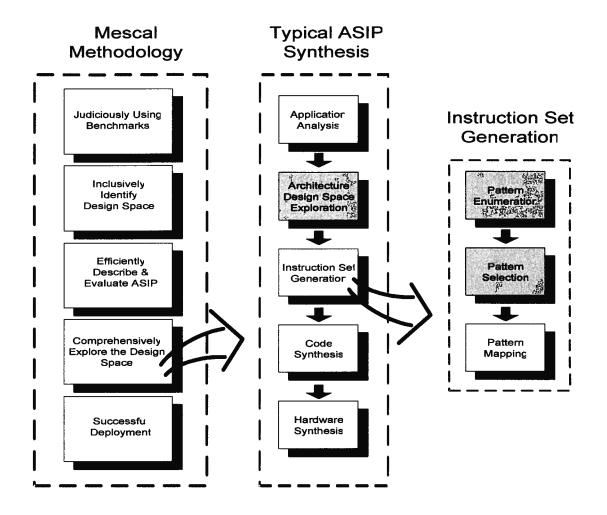

The primary focus of most research in ASIPs is the study and development of algorithms to automate the configuration flow. Many methodologies have been suggested [20,21,22,23,24,25,26]; most methodologies include the following five steps of typical ASIP synthesis [27] which are illustrated in Figure 2.2:

- 1. Application Analysis: statically or dynamically analyzes the application and input data.

- 2. Architecture Design Space Exploration: enumerates all possible parameterizations of the architectures given the design constraints. Power, speed, and area are estimated and used to identify the candidate architecture that minimizes a user-defined metric. This phase will be discussed further in Section 2.6.1.

- 3. Instruction Set Generation: extends the Instruction-Set Architecture (ISA) of the processor to include new instructions that minimize power, speed and area. Newly-defined operations can be of type Fused, Vector, or Very Long Instruction Word (VLIW) [5]. Fused operations are the combination of several simple operations with the outcome of reduced code size, reduced fetch and issue bandwidth needs, and possible reduced register file port requirements.

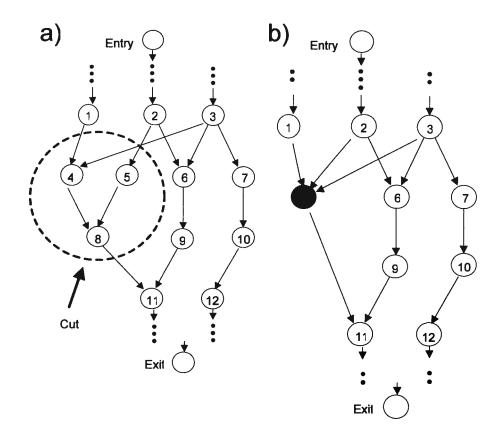

Vector operations increase throughput by operating on more than one data

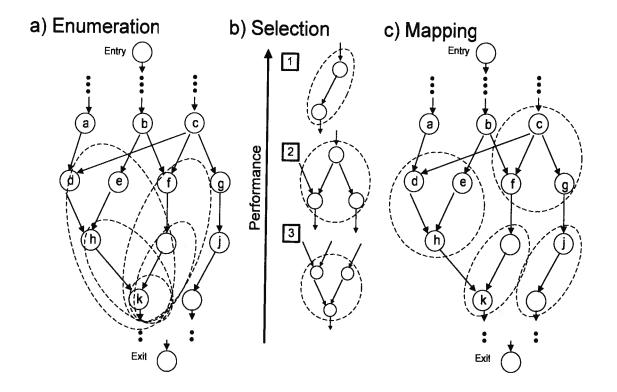

element in parallel. VLIW operations contain multiple independent operations that are encoded into the instruction in "slots". VLIW operations add the potential of significant performance improvements through software pipelining and instruction scheduling techniques [28]. Each of these new instruction types vary in the amount of additional hardware needed. As shown in Figure 2.2, this phase of synthesis can be broken down further into *Pattern Enumeration*, *Pattern Selection*, and *Pattern Mapping*. Each of the sub-phases will be discussed further in Section 2.6.2.

- 4. *Code Synthesis*: either generates a compiler suitable for the new architecture or directly emits the executable code for the application.

- 5. Hardware Synthesis: synthesizes the processor based on ASIP templates written in a hardware description language (HDL) using standard tools.

This research is chiefly concerned with design space exploration and instruction-set enumeration and selection (shaded blocks).

The Mescal research project [17] developed a set of five *elements*, as shown in Figure 2.2, which together provide a coherent approach for the development and deployment of programmable platforms. These five elements are as follows:

1. Judiciously Using Benchmarks: Benchmarks used to perform ASIP synthesis should be chosen such that results are comparable across various system implementations. Further, benchmarks should be representative of the application domain, should be indicative of the real-world application performance, and should be well-specified. The selection of benchmarks used within this thesis will be discussed for each set of experiments separately.

Figure 2.2: General ASIP Configuration Methodology [17, 27, 29].

2. Inclusively Identify the Design Space: In the past, the design space explored has been relatively small and often limited to only those parameters with which the designer is familiar. Defining a broad set of parameters increases the likelihood of discovering more optimal configurations. For this reason, the design space should be inclusive. The focus of this thesis is on novel methods for DSE; consequently, an assumption is made that the design space has been correctly identified and is inclusive.

- 3. Efficiently Describe & Evaluate the ASIP: In order to evaluate a broad range of architectures, each architecture must be easy to describe and evaluate. Efficient methods must be developed to efficiently map the application benchmark(s) onto each candidate architecture. What is necessary is a re-targetable software environment for mapping and evaluation. The development of this environment was an important part of the experimental platforms used in this research work.

- 4. Comprehensively Explore the Design Space: DSE involves two orthogonal issues: first, how each point in the design space should be evaluated, and second, how much of the design space should be covered during exploration. These questions are important because the sheer size of most design spaces makes exhaustive searches computationally infeasible. As a result, intelligence must be built into exploration to minimize the number of points visited in order to find optimal points and to minimize the cost of evaluating point each visited. This represents the central theme of this thesis. Chapters 3 and 4 propose a novel DSE approach that models the design space while only having to evaluate a small sample of points. Chapter 5 proposes a new method to speed-up the evaluation of candidate architectures while performing instruction set generation.

- 5. Successfully Deploy the ASIP: ASIP synthesis may provide an excellent match between the architecture and the intended application while at the same time could result in a useless end product because of poor deployment. Successful deployment implies that the device must be easy to program, debug, and simulate. To easily program the ASIP, it must be at a sufficiently high level to

make it practical; however, it must also be low enough to take advantage of ASIP architectural features. This element is outside the scope of this thesis.

Examples of ASIP flows that are available from industry include the Embedded Processor Designer by CoWare [30], the Sx000 product line from Stretch [31], the Synfora PICO Express processor array [32], and Clarity by Mimosys [33]. The CoWare ASIP flow emits a custom processor based on the LISA processor design platform [34] and a custom compiler using the CoSy compiler development system by ACE [35]. CoWare also emits a configurable instruction-set simulator (ISS) and debugger. Unfortunately, candidate architectures must be specified manually using the LISA architecture specification language.

Synfora's PICO Express is based on the PICO processor array originally developed by Hewlett Packard laboratories [36]. PICO is based on an *explicitly parallel* instruction computing (EPIC) processor developed by Hewlett Packard and Intel which has its origins in very long instruction set (VLIW) processors. The PICO flow includes significant innovations in automatic processor configuration and will be discussed further in Section 2.6. The Trimaran compiler infrastructure is used for PICO and is also used for the experimental framework developed in Chapter 5 of this thesis.

The Stretch processor line is based on Tensilica technology but adds automatic customizability of the instruction set. Included with Stretch products are a customizable compiler, simulator, and debugger. Mimosys Clarity also customizes the instruction set automatically but does so for a number of target architectures including ARC, MIPS, Xilinx, Altera, Tensilica, IBM, ARM, CoWare, and Toshiba.

Academia offers several ASIP flows including LISA [34], ASIP Meister [37], and Expression [38]. Each of these tools allows the system designer to specify the desired architecture of the processor manually. They do not provide any form of automatic configurability; however, a compiler flow and simulator is generated. Using these tools, the user can iterate through various architectures until the desired performance is met. For LISA and Expression, the user specifies candidate architectures using an architecture description language (ADL); for ASIP Meister, the user specifies the architecture through a graphical user interface. In the case of LISA and ASIP Meister, a hardware description language (HDL) description of the processor can be emitted.

#### 2.3. Base Architectures for ASIPs

#### 2.3.1. Embedded Processors

An embedded processor (EP) differs from a general-purpose processor (GPP) in that an EP is designed for one or a few specific applications. Because the EP is designed for specific task, it can be optimized and tailored to increase performance, reduce cost, and increase reliability. EPs are often produced in mass quantity thus taking advantage of economies of scale. Typical uses for embedded processors include phones, DVD players, HDTV sets, photocopiers, GPS navigation, printers, routers, automobiles, personal digital assistants (PDAs), and MP3 players.

With an increase in market demand for communications and portability, EPs have continued to grow at a faster rate than GPPs. In 1998, 2.5 billion embedded processors were installed, compared to 100 million general-purpose machines [39]. In 2002, 98% of all processors were embedded processors [40].

#### **2.3.2. ARM7TDMI**

Experiments conducted throughout this thesis make use of the most popular embedded processor called ARM7TDMI which is a well-known member of the ARM7 family [41]. The ARM7TDMI is a 32-bit reduced instruction set computer (RISC) on a Princeton architecture designed by ARM [42]. Although ARM7 is over 14 years old, it is still seeing extensive use in the market. Because of its popularity, it is also frequently used for academic experimental flows. Therefore, it is a natural choice for use as a base architecture for the research in this thesis.

In addition to the configurability discussed in Section 2.2.2, ARM has incorporated one form of configurability through the use of its *Advanced Microcontroller Bus Architecture (AMBA)* [43] bus. AMBA is an open bus standard designed by ARM for use in *System-on-Chip (SoC)* platforms. AMBA provides a technology-independent solution that can easily be used for modular *Intellectual Property (IP)* design. ARM also offers *PrimeCell Peripherals* [42] which are re-usable, pre-verified, AMBA-compliant macrocells. The combination of AMBA and PrimeCell, to some extent, provides a configurable SoC infrastructure based on reusable modular design.

#### **2.3.3. StrongARM SA-110**

In 1995, the StrongARM SA-110 processor [44] was launched by ARM and Digital Equipment Corporation (sold later to Intel in 1998). The StrongARM was based on the ARM architecture but was intended for higher-speed applications. One key difference is that StrongARM has a separate data and instruction cache rather than the unified cache of the ARM7TDMI. The processor has also been prevalent in academia

and industry and so it is also used as a base architecture for the research outlined in this thesis.

#### 2.4. Design Objectives

The primary design objective used throughout this dissertation for optimization experiments is energy. The total energy dissipated by the processor to complete a task is a combination of the power it dissipates and how long it takes to execute the task. Achieving a low-energy solution typically requires a balance between reducing architecture size and complexity to reduce the *power* dissipated by the processor and increasing architecture size and complexity to improve Instruction Level Parallelism (ILP) (which consequently reduces the execution time, thus saving energy). An in-depth discussion of both ILP and power is discussed in the following sections.

#### 2.4.1. Instruction Level Parallelism (ILP)

ILP is a measure of how many instructions in a program can be executed in parallel. With increased ILP, the processor can complete program execution within a shorter number of cycles, thus consuming less energy as shown in the next section.

Program execution is inherently sequential; however, there are several mechanisms that provide ILP including pipelined execution, superscalar execution, out-of-order execution, and VLIW techniques [45]. All of these methods can increase ILP; however, there is a significant amount of overhead circuitry and memory that contribute additional power. In most cases, the benefits of ILP must be carefully weighed against the power and area penalties associated with the overhead.

A basic block is a sequence of instructions with only one entry point, one exit point, and no jump instructions contained within. Techniques have been developed to improve ILP within blocks and between blocks. Within blocks, traditional techniques include register renaming [46] and aliasing analysis [47]. Across block boundaries, branch prediction [48], loop unrolling [49], software pipelining [28], and trace scheduling [50] are traditional techniques.

The theoretical limit to ILP was explored by Wall [51] using what he called an "impossibly good" architecture that has effectively unlimited resources with perfect branch prediction and speculation. In that work, Wall found that such architectures could achieve an ILP of 7 at best, with 5 being more common. Lam et al. [52] attributed limitations of ILP primarily to control flow and then explored how this can be resolved by speculatively executing multiple flows. Processors with the ability to speculatively execute multiple flows are relatively complex and are not considered to be suitable for embedded systems.

In this dissertation, ILP is regulated by tuning a parameter in the branch prediction unit (BPU) called the pattern history table (PHT) and through several parameters in a 2-level cache hierarchy.

#### **2.4.2. Power**

Power consumption for CMOS logic is typically expressed as:

$$P = \alpha C V_{DD}^{2} f + \tau \alpha V_{DD} I_{short} f + V_{DD} I_{leak}$$

(2.1)

where the terms represent dynamic power, short-circuit power, and leakage power, respectively [53].  $\alpha$  is the gate activity, C is the total capacitance of the gate,  $V_{DD}$  is the

supply voltage, f is the operating frequency,  $\tau$  is the short-circuit switching time,  $I_{short}$  is the short-circuit current, and  $I_{leak}$  is the leakage current. Further, the following proportionality relationship holds, where  $V_T$  is the threshold voltage:

$$f_{\text{max}} \propto (V_{DD} - V_T)^2 / V_{DD} \tag{2.2}$$

In Equation (2.1), the first term represents a dynamic contribution due to capacitive charging and discharging, and has traditionally been the dominant term due to increases in f over the years. On the other hand, scaling supply voltages and threshold voltages has increased the contribution of static power dissipation from the last term in Equation (2.1) which is based on leakage current<sup>1</sup>. The second term in Equation (2.1) represents a relatively small contribution due to switching current and is often incorporated into the first term.

At the architectural level, two important aspects that affect power consumption are the level of parallelism and the amount of memory used for main memory, cache, branch prediction, and the translation lookaside buffer (TLB). At a fundamental level, the effect of parallelism is evident from Equations (2.1) and (2.2). Parallelism can reduce the intrinsic power needed to complete a task because it permits the supply voltage to be scaled. For a system with a doubling of parallelism, ½ the voltage is needed to maintain throughput; thus, only ¼ of the dynamic power is needed. With overhead, leakage, and short-circuit power neglected, it has been shown that the general equation for a circuit with N levels of parallelism is:

<sup>&</sup>lt;sup>1</sup> Leakage current is composed of both subthreshold leakage and gate-oxide leakage.

$$\frac{P_{N}}{P_{1}} = \frac{V_{N}^{2}}{V_{ref}^{2}} = \frac{1}{N^{2}}$$

(2.3)

where  $V_N$  is the supply voltage for an N processor system and  $V_{ref}$  is the reference supply voltage for a system implemented with one processor [54]. This equation represents an upper bound on the reduction in power dissipation due to parallelism.

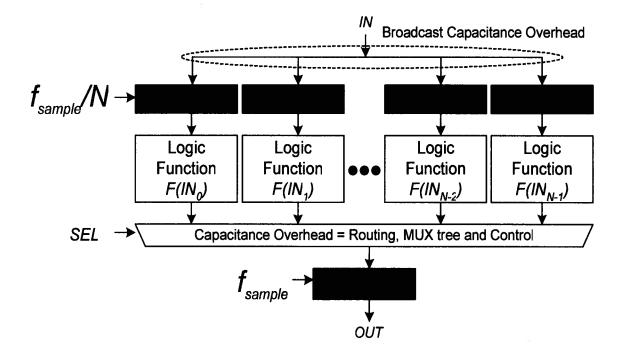

Figure 2.3: General parallelization of a logic function.

Overhead power must be accounted for in the extra circuitry needed to facilitate parallelism. Figure 2.3 illustrates the general case where a logic function, F, sampling the input at a rate of  $f_{sample}$  is parallelized such that there are N logic functions, each sampling input at a rate of  $f_{sample}/N$ . In the figure, overhead circuitry is needed to broadcast the inputs and to combine the outputs. With overhead circuitry considered, Equation (2.3) becomes [54]:

$$\frac{P_N}{P_1} = \left(1 + \frac{C_s(N)}{N \cdot C_{\text{ref}}} + \frac{C_{ns}(N)}{C_{\text{ref}}}\right) \cdot \left(\frac{V_N}{V_{\text{ref}}}\right)^2 \tag{2.4}$$

where  $C_s(N)$  is overhead that scales the operating frequency with increased parallelism and  $C_{ns}(N)$  is overhead that does not scale the frequency with increased parallelism. As the operating voltage is scaled in Equation (2.4), capacitance due to overhead circuitry may grow to the point that there is no longer a benefit to increase parallelism. It is for this reason that the degree of parallelism must be carefully selected to optimally reduce power dissipation.

Equation (2.4) does not consider power dissipation due to leakage current. Static leakage power is heavily dependent on the form of parallelism used whether it be logic function duplication or pipelining [55]. If parallelism is achieved by duplicating logic functions, then static power dissipation is effectively duplicated. Alternatively, parallelism can be achieved by pipelining the logic function. Other than inter-stage latches, no other circuitry is added for this solution; thus, static power is minimized. Parallelization of a logic function through pipelining is usually the more power-efficient solution. Unfortunately, the power benefits of pipelining may also be offset by data and control hazards.

For most applications, parallelism is used not only to reduce power dissipation but also to reduce the number of cycles of execution. Both of these objectives have motivated aggressive instruction-level parallelism techniques in the design of processors. As described in the previous section, it is difficult to extract parallelism from most applications. In fact, most modern processors include significant overhead hardware in an attempt to maintain very modest levels of parallelism. This overhead hardware

dissipates both dynamic and static power. Examples of this include the cache hierarchy and the branch prediction unit.

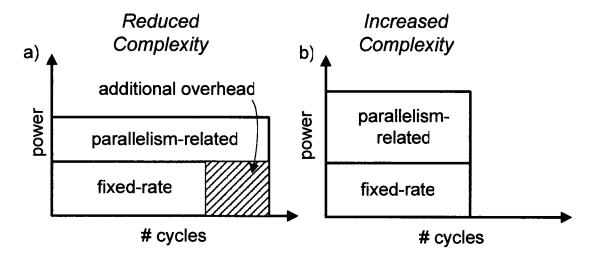

In order to minimize power dissipation, processor designers must find the correct balance of the size and complexity of extra hardware used to improve parallelism. Large and complex hardware improves parallelism (which reduces intrinsic power and reduces run-time) while at the same time dissipates excess dynamic and static power. At the same time, reduced run-time also reduces the static power from all other components of the processor [56]. Figure 2.4(a) shows power dissipation for a processor with *reduced* hardware dedicated to maintaining parallelism and Figure 2.4(b) shows a processor with *increased* hardware dedicated to maintaining parallelism. This figure shows the power/run-time tradeoff between all circuitry related to improving parallelism. In addition, fixed-rate circuitry is shown which represents all components of the processor that dissipates static power at a fixed-rate regardless of the level of parallelism. Also shown in Figure 2.4(a) is the excess energy due to fixed-rate power dissipation caused by a longer execution time.

Figure 2.4: Parallelism-related versus Fixed-rate Power Dissipation.

This dissertation primarily focuses on the configuration of memory structures to reduce power. The memory hierarchy (and branch prediction) of a processor consumes a significant amount of power, often being the dominant source of power [57]. Memory systems have two sources of power loss. Dynamic power consumption is caused by frequent access of the memory and static power consumption is caused by leakage current. At the architectural level, power dissipation can be reduced in memory systems by correctly reducing the code size, organizing the code to reduce memory access, correctly sizing the memory, using a suitable cache organization, and using memory banking techniques.

### 2.4.3. ASIPs and Power

There is a significant body of research dealing with reduced power dissipation for general-purpose processors at the logic level [58,57,59,60,61,62], architectural level [63,64,65,66,67], and the system/OS level [68,69]. Previous work on power and configurability specific to branch prediction, the cache hierarchy, and instruction-set extensions and are provided in Sections 2.5.2, 2.5.3, and 2.6.2 respectively.

Research on power in ASIPs is still in its infancy. Work by Glökler et al. [70] uses gate-level simulations to jointly consider speed, area, and power while optimizing the number of pipeline stages, clock gating, logic netlist restructuring, data-path optimizations, instruction memory power reduction by optimized instruction encoding, and the implementation of coprocessors. They claim that these optimizations together improve power dissipation by 92%; however, they do not explicitly address the trade-offs between energy and runtime. Further, they only consider a limited set of course-grain parameters at the architectural level and do not automate the flow.

In this dissertation, ASIP power optimization is approached differently. The goal is to use a general-purpose approach that is highly automated and can be used to configure a wide variety of course- and fine-grain parameters at the architecture level. This makes automation difficult because of the large inclusive design space and because DSE takes place early in the flow thus making it difficult to evaluate the value of each candidate configuration.

#### 2.5. Architectural Parameters

### 2.5.1. Motivation for Configuring the "Front-end"

As a rule of thumb, a processor uses an order of magnitude more power than an FPGA to compute the same task [3]. The most significant explanation for this problem is that processors fetch and decode instructions from the memory hierarchy, which is relatively slow, impedes *instruction level parallelism (ILP)*, and consumes significant area and power. Here, we refer to the combined fetch, decode, and memory hierarchy as the "front-end" of the processor.

The purpose of the front-end is to supply valid decoded instructions to the execution core with *low latency* and *high bandwidth* to maintain ILP. In the presence of highly control-based applications (which is typical for tasks assigned to processors), it is difficult to speculate which instructions should be delivered to the execution core after encountering a control operation such as a branch. On average, the CPU is in a steady state 50% of the time, stalled 20% of the time, and in transition between steady and stall 30% of the time [71]. A substantial amount of research has focused on improving ILP but with limited success.

Increases in ILP through front-end improvements typically come with the penalty of increased resources (cache, buffers, and history look-up tables) all of which add significant power consumption in addition to that of the main memory. The trend for memory hierarchy is towards increased size because of the growing gap between memory and processor performance [10]. It is for these reasons that this work focuses on the front-end and the memory hierarchy.

Configurability can be used to adjust the complexity of the front-end to control how instructions are speculatively fetched for a given application. If the front-end has more resources than necessary (over-speculation), then power is wasted through excess dynamic and static power. If there are not enough resources (under-speculation), then excess power is consumed because of reduced ILP, pipeline stalls and the execution of incorrectly fetched instructions.

#### 2.5.2. Branch Prediction

An initial investigation of the role of branch predictor organization on power was described in [72]. This work concluded that it is better to spend extra power on a more complex branch predictor if it results in more accurate predictions and improves runtime. In spite of this conclusion, both methods proposed in [72] reduce power dissipation solely by reducing the capabilities of the branch prediction unit (BPU). They first suggest that power can be saved by banking the branch predictor in a similar way to what has been done in the past for caches. Second, they propose a prediction probe detector (PPD) that is used to switch off the BPU for non-branch instructions.

In [73], profiling is used to determine whether each branch instance is "biased" towards global or local predictability. Branch instructions are then encoded with a bit

that specifies whether their direction should be predicted using a global type predictor such as GSelect [74] or a local type predictor such as Bimodal [75].

The approach taken in [76] is similar to [73] in that the application is profiled to determine which of the gated parts of the BPU should be switched off at run-time. In [76], the branch target buffer (BTB) is resized and parts of the hybrid predictor are disabled. In both cases, power dissipation is reduced in part by improving run-time. The two approaches differ in that resizing of the BTB in [76] requires extra hardware for run-time support. Further, [76] sizes the BTB *a priori* using a "brute-force" trial-and-error approach where they simulate all possible configurations in the search space. Even with just a few other dimensions in the search space, this approach would quickly become impractical.

Previous work has focused on run-time solutions by gating part of the BPU. The processor architecture is fixed but has extra hardware in the pipeline and BPU specifically to reduce power. Conversely, extra bits are encoded into the instructions to provide the processor with "hints" on how to save power. In either case, extra hardware must be added. The work discussed in Chapter 3 differs in that the architecture of the processor BPU is undecided until the synthesis tool/compiler profiles the application, compares all possible configurations using a cost function, and finds the correct trade-off between BPU complexity and execution time. Extra hardware is not needed to provide run-time support.

## 2.5.3. Cache Hierarchy

The cache hierarchy has a significant impact on the total power and performance of the processor. In some cases, the memory hierarchy of a microprocessor can consume

as much as 50% of the system power [77]. One approach is to save energy in the cache [78] using schemes such as way prediction [79], selective cache way access [80], subbanking [81], multi-banking [72], selective prediction [82], and confidence prediction and throttling [83].

Another approach for saving energy is to tune the cache based on the application which is the approach taken in this dissertation. Currently, many vendors offer tunable caches; however, the designer is left to manually choose the correct configuration for their application. Configurable caches are now offered by several vendors with most of them configurable at design time. This is true for processor cores such as Tensilica Xtensa [6], MIPS [8], ARM [42], ARC [7], and Altera Nios/Nios II [9]. Motorola offers a processor with reconfigurable cache hardware called M\*Core [77] where individual ways in the second-level cache may be specified for use by data, instructions, or both. In addition, ways may be individually shut down.

Industrially available processors offer configurable caches; however, they do not provide mechanisms for automatically configuring them. This presents a significant problem to system designers who may not have in-depth knowledge of processor architecture and who most often have significant time-to-market pressures. This is especially true for cache due to the sheer number of possible configurations within its design space. Tensilica Xtensa currently has only one level of cache hierarchy but it can be configured in 6561 ways. Reconfigurable caches such as M\*Core [147] have few parameters with few configurations; however, a second level unified cache increases the number of configurations to 17,640. Exploring these configurations has the potential to take many weeks thus slowing down the design cycle dramatically. To worsen the

problem, the industry trend is towards increased cache complexity with an increase in the number of levels. Clearly, any advances in DSE would have a significant impact on cache configurability and performance.

Automatic cache configuration has been well-studied and includes work that configures the cache through simulation [84,85], trace reduction [86], and analytical approaches [87]. Several heuristics have been developed to help speed-up the time required to search the solution space while tuning the cache. The previously exhaustive searches used to tune the L1 cache of the Platune [88] framework was improved by Palesi et al. [89] using a genetic algorithm. Zhang et al. [90] propose a heuristic where each design parameter is searched in order of its impact on energy and performance. In doing so, a list of *Pareto-optimal* solutions is generated. Ghosh et al. [91] use an analytical model to explore cache size and associativity to directly find the configuration that meets the designer performance constraints.

Few methods exist for exploring multiple-level caches. Balasubramonian et al. [92] propose a method of redistributing the cache size between the L1 and L2 caches or between the L2 and L3 caches while maintaining a conventional L1 cache. They achieved a 43% energy improvement. Gordon-Ross et al. [93] designed a cache tuning heuristic that explores separate L1 data and instruction caches as well as separate L2 data and instruction caches. In that work, an examination of 7% of the design space yielded a 53% reduction in energy.

Current state-of-the-art heuristics by Gordon-Ross et al. [94] can achieve a search-space speedup of up to 500x over an exhaustive search resulting in a reported

62% energy savings and a 35% performance improvement. The downside to this heuristic is that it is specific to a particular architecture, the Motorola M\*Core.

Configurable cache subsetting was proposed by Viana et al. [95] where a small subset of configurations can be identified for a specific set of benchmarks. The intention of this work is that a user with an application in the same domain as the original set of benchmarks need only consider a small subset of configurations rather than the entire solution space. Although their approach shows promise, the problem they address is different from this dissertation. Here, no assumptions are made that an application will fall into the domain of a prescribed set of benchmarks. To guarantee a high quality solution, *single-application* design exploration should be performed for the specific application in question.

## 2.6. Design Methodologies

## 2.6.1. Design Space Exploration (DSE)

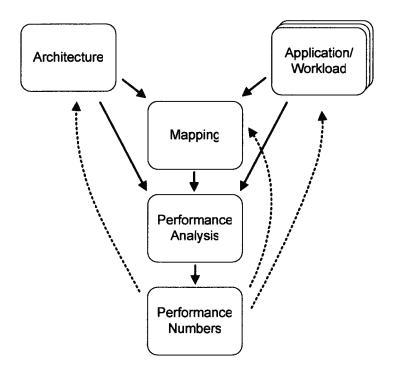

System design space exploration typically follows a Y-chart approach [96] as shown in Figure 2.5. It illustrates a concept referred to as a *separation of concerns* [97, 17] where one or more descriptions of the application (workload, computation, and communication tasks) and the architecture specification are kept separate. A mapping phase binds application tasks to architecture building blocks. An evaluation of the mapping may include synthesis, compilation, transformation, and simulations, resulting in performance statistics. Constraints from the architecture, workload description, and application may influence the evaluation phase. Results from evaluation would determine whether or not successive iterations of mapping and evaluation will take place

to iteratively improve the quality of the mapping. In this thesis, two aspects of the Y-chart are dealt with. First, we explore methods for improving DSE where intelligent coverage of the design space is achieved through systematic modification of the mapping phase. Second, we explore methods of improving the way by which mappings are evaluated.

Figure 2.5: Y-chart representation of the separation of concerns for design space exploration.

A number of challenges exist relating to DSE. The dimensions of a design space are defined by the set of configurable parameters with each point representing a unique configuration. For a given set of N design parameters  $P_i$ ,  $0 \le i < N$ , with  $C_i$  possible configurations each, the total number of configurations in the design space can be expressed as,

$$C = \prod_{i=0}^{N-1} C_i , \qquad (2.5)$$

Due to its sheer size, an exhaustive searching a design space becomes computationally prohibitive as the number of parameters grows. To make matters worse, complexity is further increased when optimizing multiple objectives; however, objective functions can be combined to form a *cost function* or used as a *Pareto Optimal* objective where all objectives are maximized to the extent that an improvement of one metric results in the degradation of another.

Aside from an exhaustive search, there are a number of more efficient strategies for exploring the design space. One approach is to randomly sample the design space using what is often referred to as a Monte Carlo based approach [98]. This approach lacks any form of intelligence; however, it has the advantage of an unbiased selection criterion which is less likely to overlook less than obvious optimal configurations. One approach based on Monte Carlo is Simulated Annealing [99] where the severity of changes made to the design that is allowed is gradually reduced as the algorithm Although Simulated Annealing is based on the random selection of progresses. candidate points, it has an intelligent filtering process in which it will only consider those "positive" candidates that drive exploration closer to an optimal solution. To avoid locally optimal solutions, Simulated Annealing will also consider a proportion of "negative" candidates based on the progress of the algorithm. In general, Monte Carlo based approaches are very effective for very large and complex design spaces. On the other hand, they are not very effective in taking advantage of well-defined structure in the design space.

Path-oriented approaches incorporate knowledge of the design space into DSE [100]. Hill-climbing approaches evaluate the neighborhood of the current configuration

to determine which neighbors yield the greatest improvement to the design objective. Another path-oriented approach that can be used for DSE is based on genetic algorithms [101].

To help reduce exploration time, pruning techniques can be used that include hierarchical exploration, sub-sampling of the design space, and sub-division of the design space into independent parts. Sub-division decomposes the architecture according to natural spatial boundaries that are assumed to be independent of one another to a first degree. Given this assumption, the total size of the design space becomes:

$$C = \sum_{i=0}^{D} \prod_{j=0}^{n_i - 1} C_{i,j}$$

(2.6)

where D is the number of independent parts,  $n_i$  is number of design parameters for the  $i^{th}$  part, and  $C_{i,j}$  is the number of configurations for the  $j^{th}$  design parameter of the  $i^{th}$  part. Equation (2.6) relates to (2.5) in that:

$$N = \sum_{i=0}^{D} n_i \ . \tag{2.7}$$

The total size of the design space is no longer the Cartesian product of design parameters as in Equation (2.5) but a sum of products. Thus, the total size of the design space is reduced significantly. An interesting form of the latter technique is used for ASIPs by Sanghavi et al. [102] of Tensilica and is presumably used to estimate power, area, and speed for their synthesis tools. It is an analytical approach to providing a first-degree decomposition of the design space in both space and time.

Sensitivity analysis [103,104] is another effective way of pruning the design space where all design parameters are treated as independent. In turn, the impact of each

design parameter upon the design objective is measured while all other parameters are held constant. The results from this are used to determine the "sensitivity" of the design objective to each parameter. Parameters are then configured one at a time according to an ordering from most sensitive to least sensitive. As a consequence, the effective size of the design space becomes:

$$C = \sum_{i=0}^{N-1} C_i \tag{2.8}$$

Sensitivity prunes the design space significantly such that it is a summation of design parameter settings rather than a product. The disadvantage to sensitivity analysis-based approaches is that they do not adequately address correlations between parameters and so it is often inaccurate.

The Spacewalker algorithm used for PICO [36,105] exemplifies a complete algorithm that incorporates path-oriented DSE with several pruning techniques. More explicitly, Spacewalker uses a hill-climbing approach to find Pareto-optimal solutions. If the design space is too large, then it uses a manifold strategy to search only those points that are likely Pareto-optimal. Further, decomposition is used to separate parts of the architecture and then a path-oriented search is applied to each part. Results from each search are combined to form a system design space which is then searched to find a system solution.

Evaluation tools specific to ASIPs can also be sped up through hybrid simulation techniques such as [106] which combines instruction-level techniques and macromodeling techniques for the base architecture and custom instructions. Trace-driven simulation provides a method for reducing the number of simulations needed during

space exploration [107]. This approach collects memory access sequences from an initial simulation and uses them when subsequent configurations are evaluated.

#### 2.6.2. Instruction Set Extensions

Instruction-Set Extensions (ISEs) are a specific instance of DSE where custom instructions are generated to improve processor performance. As an example, one custom instruction created through fusion might be the combination of two ADD operations followed by a multiply which is then fed into an inverter. Instruction-Set Extensions using fusion can be broken into three parts: pattern enumeration, pattern selection (instruction selection), and pattern matching. During pattern enumeration, a list of candidate complex instructions is generated such that all candidates adhere to the microarchitectural constraints imposed by the processor architecture. A subset of these is chosen during the Pattern Selection phase based on a set of cost functions. Once a group of patterns has been identified, pattern matching then maps new instructions throughout the application.

Several approaches have been proposed to perform Instruction Enumeration and Instruction Selection [29,108,109,110,111,112]. All of these are significant contributions towards the ASIP flow; however, they do not address the effects of pipeline stalls due to data hazards between functional units (FUs) of the processor. This motivates some of the proposed work described in this thesis. Like many algorithms in ASIP and compiler research, the methods used in previous work operate on intermediate representations of the application by adding, removing, and clustering operations. All algorithms of this type would benefit from the addition of a "hazard-aware" performance predictor for architectures with pipeline data hazards to reduce overall run-time of the application.

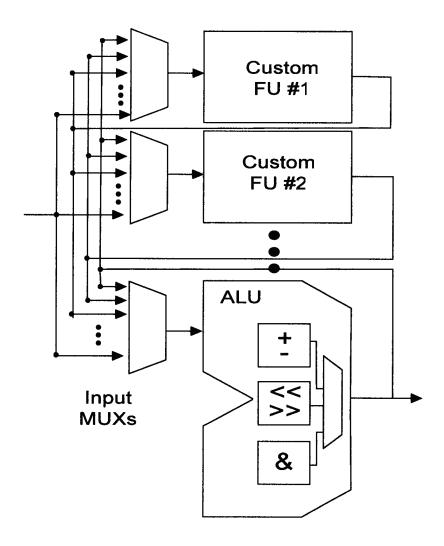

The authors of [29] and [113] assume an ideal pipeline because predicting performance would otherwise be difficult. The authors of [29] state that "it is not trivial to compute the total latency" of the application with data hazards. The authors of [113] claims that data hazards need not be considered in the presence of functional unit to functional unit (FU-to-FU) forwarding<sup>2</sup>. As stated above, FU-to-FU forwarding is a possible solution; however, it would require new multiplexers to be added to all new FUs. This might be practical for a small number of custom FUs but it would likely add significant power and performance penalties with large numbers of FUs. With a trend towards increased number of FUs, it is important to evaluate the impact of data hazards on instruction fusion.

Thus far, there is little work that considers power when fusing instructions. Sun et al. [114] develop a cost function to reduce speed and then quantify the power saved as a biproduct of the reduced run-time. They claim to improve performance by an average of 3.4X, energy by an average of 3.2X, and energy-delay by an average of 12.6X. This work serves as an example of the significant gains possible with application-specific configurability; however, it uses an ad-hoc methodology that does not fully explore its design space.

This dissertation will build upon the ideas presented in this chapter to improve the speed and automation of processor customizability and extensibility. An ASIP flow will be developed that incorporates a novel DSE approach that will drastically reduce the number of simulations required for architecture optimization. This will be used to

<sup>&</sup>lt;sup>2</sup> FU-to-FU forwarding is the forwarding of output from a functional unit to a previous stage of the pipeline in order to avoid a data hazard.

configure the BPU and the cache hierarchy of an embedded processor. Further, the capabilities of ISE configuration will be improved by speeding up the evaluation of candidate instructions using a novel performance prediction approach. All of the proposed approaches will be used to improve execution time (and thus ILP) and reduce power, thus saving energy.

# **Chapter 3: Optimization via Design Space Modeling**

### 3.1. Introduction

The previous chapter introduced the design space exploration (DSE) problem and discussed the difficulties associated with its run-time complexity. It further discussed how DSE run-time can be reduced through better exploration and through faster point evaluations. In addition, some of the known approaches for DSE including both pathoriented and random-based methods were described. It was shown that DSE is a key bottleneck in the automatic configuration of ASIPs [115].

In this chapter, a new paradigm for DSE is introduced [116, 117]. This paradigm is based on a predictive model of the design space using statistical methods. It is much faster than simulation and it helps users to expose the tradeoffs between different parameters in different regions of the design space. Requiring only the evaluation of a small sample of the design points, all other points in the design space can be estimated through *DSE modeling*. The model must be accurate enough to predict changes in performance due to architectural changes.

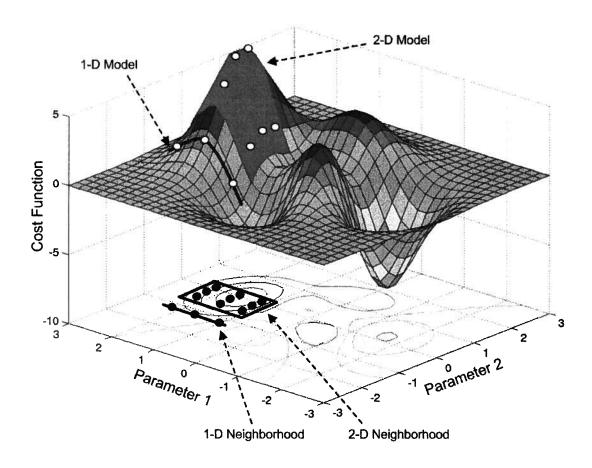

To illustrate how *Design Space Modeling* could be used in a hypothetical problem, consider the mesh plot shown in Figure 3.1. The x-axis and y-axis represent two parameters, and the z-axis represents the cost function of a DSE problem. The domains or neighborhoods for hypothetical one-dimensional and two-dimensional problems are shown as a line and a rectangle on the contour map, respectively. Shown on the mesh plot are the corresponding predictive models of the design space. Each model was constructed from a sample of points known through simulation which are

represented as "dots". From these models, all other points within their domain can be estimated.

Figure 3.1: Hypothetical 1-D and 2-D design space models.