# Architectures and Limits of GPU-CPU Heterogeneous Systems

by

Henry Ting-Hei Wong

B.A.Sc., University of Toronto, 2006

# A THESIS SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF

MASTER OF APPLIED SCIENCE

in

The Faculty of Graduate Studies

(Electrical and Computer Engineering)

THE UNIVERSITY OF BRITISH COLUMBIA

(Vancouver)

October 2008

© Henry Ting-Hei Wong 2008

## **Abstract**

As we continue to be able to put an increasing number of transistors on a single chip, the answer to the perpetual question of what the best processor we could build with the transistors is remains uncertain.

Past work has shown that heterogeneous multiprocessor systems provide benefits in performance and efficiency. This thesis explores heterogeneous systems composed of a traditional sequential processor (CPU) and highly parallel graphics processors (GPU). This thesis presents a tightly-coupled heterogeneous chip multiprocessor architecture for general-purpose non-graphics computation and a limit study exploring the potential benefits of GPU-like cores for accelerating a set of general-purpose workloads.

Pangaea is a heterogeneous CMP design for non-rendering workloads that integrates IA32 CPU cores with GMA X4500 GPU cores. Pangaea introduces a resource partitioning of the GPU, where 3D graphics-specific hardware is removed to reduce area or add more processing cores, and a 3-instruction extension to the IA32 ISA that supports fast communication between CPU and GPU by building user-level interrupts on top of existing cache coherency mechanisms.

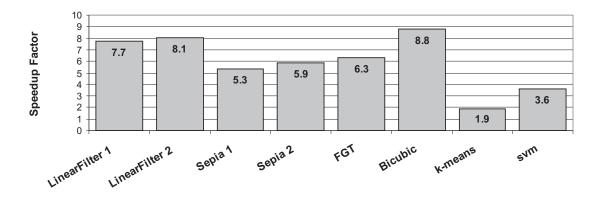

By removing graphics-specific hardware on a 65 nm process, the area saved is equivalent to 9 GPU cores, while the power saved is equivalent to 5 cores. Our FPGA prototype shows thread spawn latency improvements from thousands of clock cycles to 26. A set of non-graphics workloads demonstrate speedups of up to 8.8×.

This thesis also presents a limit study, where we measure the limit of algorithm parallelism in the context of a heterogeneous system that can be usefully extracted from a set of general-purpose applications. We measure sensitivity to the sequential performance (register read-after-write latency) of the low-cost parallel cores, and latency and bandwidth of the communication channel between the two cores. Using these measurements, we propose system characteristics that maximize area and power efficiencies.

As in previous limit studies, we find a high amount of parallelism. We show, however, that the potential speedup on GPU-like systems is low  $(2.2 \times -12.7 \times)$  due to poor sequential performance. Communication latency and bandwidth have comparatively small performance effects (<25%). Optimal area efficiency requires a lower-cost parallel processor while optimal power efficiency requires a higher-performance parallel processor than today's GPUs.

# **Table of Contents**

| A۱ | bstrac | ct       |                                                          | <br>ii  |

|----|--------|----------|----------------------------------------------------------|---------|

| Ta | ıble o | f Conte  | ents                                                     | <br>iii |

| Li | st of  | Tables   |                                                          | <br>vi  |

| Li | st of  | Figures  | s                                                        | <br>vii |

| A  | cknov  | vledgei  | ments                                                    | <br>ix  |

| St | atem   | ent of ( | Co-Authorship                                            | <br>Х   |

| 1  | Intr   | oductio  | on                                                       | <br>1   |

|    | 1.1    | Motiv    | vation                                                   | <br>1   |

|    | 1.2    | Thesis   | s Contributions                                          | <br>3   |

|    | 1.3    | Backg    | ground on GPU Computation                                | <br>4   |

|    |        | 1.3.1    | GPU Organization                                         | <br>4   |

|    |        | 1.3.2    | Programmability                                          | <br>5   |

|    |        | 1.3.3    | Computation                                              | <br>7   |

|    |        | 1.3.4    | CUDA, ATI Stream                                         | <br>7   |

|    |        | 1.3.5    | CPU-GPU Integration                                      | <br>7   |

|    |        | 1.3.6    | Pangaea Preview                                          | <br>9   |

|    | 1.4    | Relate   | ed Work                                                  | <br>11  |

|    |        | 1.4.1    | Multicore Processors                                     | <br>11  |

|    |        | 1.4.2    | GPU Compute                                              | <br>12  |

|    |        | 1.4.3    | Limit Studies on parallelism                             | <br>15  |

| Re | eferer | ices     |                                                          | <br>16  |

| 2  | Pan    | gaea: A  | A Tightly-Coupled IA32 Heterogeneous Chip Multiprocessor | <br>22  |

|    | 2.1    | -        | duction                                                  |         |

|    | 2.2    | Relate   | ed Work                                                  | <br>24  |

|    | 2.3    | Backg    | ground                                                   | <br>25  |

#### **Table of Contents**

|    | 2.4    | Panga          | ea Architecture                                                |

|----|--------|----------------|----------------------------------------------------------------|

|    |        | 2.4.1          | CPU-GPU Integration                                            |

|    |        | 2.4.2          | ISA Extension for User-level Interrupts                        |

|    |        | 2.4.3          | User-level Interrupt Handler                                   |

|    | 2.5    | Panga          | ea Implementation                                              |

|    |        | 2.5.1          | Pangaea's Synthesizable RTL Design                             |

|    |        | 2.5.2          | Area Efficiency Analysis                                       |

|    |        | 2.5.3          | Power Efficiency Analysis                                      |

|    |        | 2.5.4          | Thread Spawn Latency                                           |

|    | 2.6    | Perfor         | mance Evaluation                                               |

|    | 2.7    | Conclu         | usion and Future Work 45                                       |

|    |        |                |                                                                |

| Re | eferen | ices           |                                                                |

| 3  | The    | Perfor         | mance Potential for Single Application Heterogeneous System 52 |

| ,  | 3.1    |                | uction                                                         |

|    | 3.2    |                | d Work                                                         |

|    | 3.3    |                | ing a Heterogeneous System                                     |

|    | 5.5    | 3.3.1          | Serial Processor                                               |

|    |        | 3.3.2          | Parallel Processor                                             |

|    |        | 3.3.3          | Heterogeneity                                                  |

|    |        | 3.3.4          | Latency                                                        |

|    |        | 3.3.5          | Bandwidth                                                      |

|    | 3.4    |                | ation Infrastructure                                           |

|    | 3.4    | 3.4.1          | Benchmark Set                                                  |

|    |        | 3.4.2          | Traces                                                         |

|    | 3.5    |                | s                                                              |

|    | 3.3    |                |                                                                |

|    |        | 3.5.2          | Why Heterogeneous?                                             |

|    |        | 0.0.2          | Communication                                                  |

|    |        | 3.5.3<br>3.5.4 | Latency                                                        |

|    |        |                | Bandwidth                                                      |

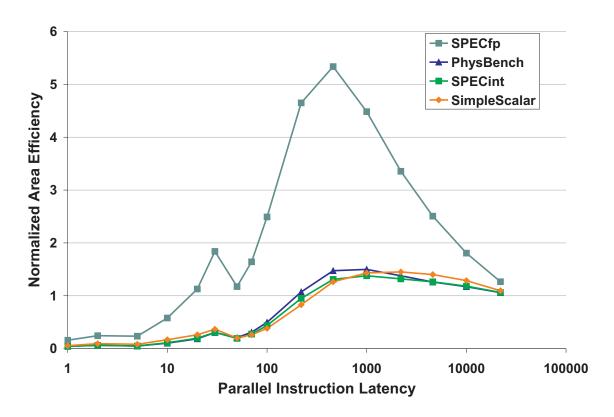

|    |        | 3.5.5          | Efficiency                                                     |

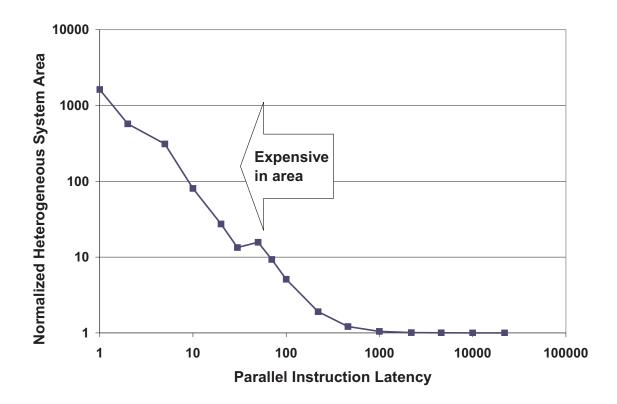

|    |        | 3.5.6          | Area Cost                                                      |

|    |        | 3.5.7          | Energy Per Instruction                                         |

|    | 2 -    | 3.5.8          | Efficiency Results                                             |

|    | 3.6    | Concli         | asion                                                          |

| Da | foron  |                | 85                                                             |

#### Table of Contents

| 4  | Con   | clusion                     |

|----|-------|-----------------------------|

|    | 4.1   | Summary                     |

|    |       | 4.1.1 Pangaea               |

|    |       | 4.1.2 Limit Study           |

|    | 4.2   | Relation Between Works      |

|    | 4.3   | Potential Applications      |

|    | 4.4   | Limitations and Future Work |

|    |       | 4.4.1 Pangaea               |

|    |       | 4.4.2 Limit Study           |

|    |       |                             |

| Re | ferer | nces                        |

# **List of Tables**

| 2.1 | One Pangaea Prototype Configuration that fits one Xilinx Virtex-5       | 35 |

|-----|-------------------------------------------------------------------------|----|

| 2.2 | Virtex-5 FPGA Resource Usage for the Pangaea configuration in Table 2.1 | 37 |

| 2.3 | Area distribution of two-EU systems                                     | 38 |

| 2.4 | Power distribution of a two-EU GPU                                      | 39 |

| 2.5 | Thread Spawn Latency in cycles                                          | 40 |

| 2.6 | Benchmark Suites                                                        | 41 |

| 3.1 | Our microbenchmark set. We also employ many real benchmarks. (See       |    |

|     | Section 3.4.1)                                                          | 62 |

# **List of Figures**

| 1.1  | Discrete GPU Organization                                                                 | 6  |

|------|-------------------------------------------------------------------------------------------|----|

| 1.2  | Single-chip "Fused" CPU-GPU Organization                                                  | 8  |

| 1.3  | Single-chip Pangaea CPU-GPU Organization                                                  | 10 |

| 2.1  | Organization of the Intel GMA X4500                                                       | 26 |

| 2.2  | $Pangaea:\ Integrated\ CPU\text{-}GPU\ without\ Legacy\ Graphics\ Front-\ and\ Back-End.$ | 28 |

| 2.3  | Example of User-Level Interrupt (ULI)                                                     | 29 |

| 2.4  | IA32 CPU Block Diagram. Shaded blocks indicate modifications to support                   |    |

|      | ULI                                                                                       | 32 |

| 2.5  | Pangaea speedup vs. CPU w/ SSE alone                                                      | 42 |

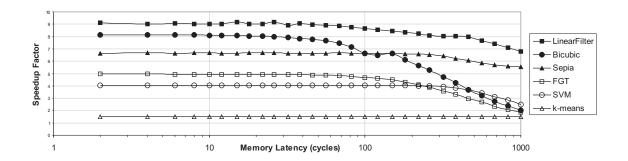

| 2.6  | Tolerance of Pangaea to Different Memory Access Latencies                                 | 43 |

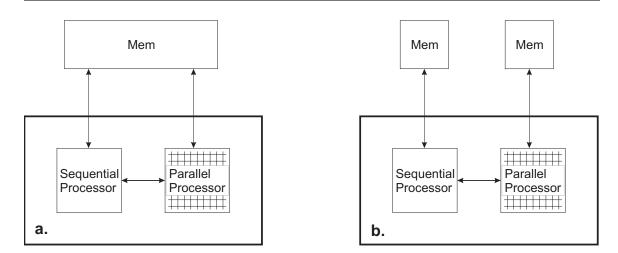

| 3.1  | Conceptual Model of a Heterogeneous System. Two processors with differ-                   |    |

|      | ent characteristics may (a) or may not (b) share memory, affecting whether                |    |

|      | data needs to be copied over the communication channel connecting them                    | 56 |

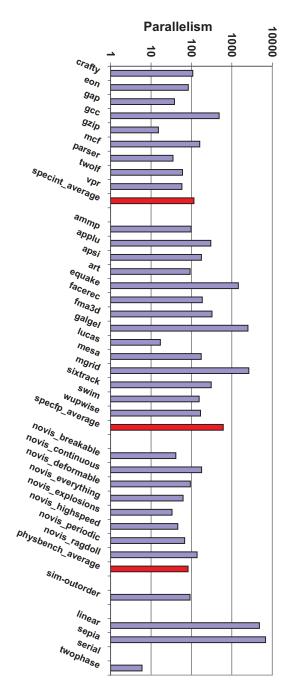

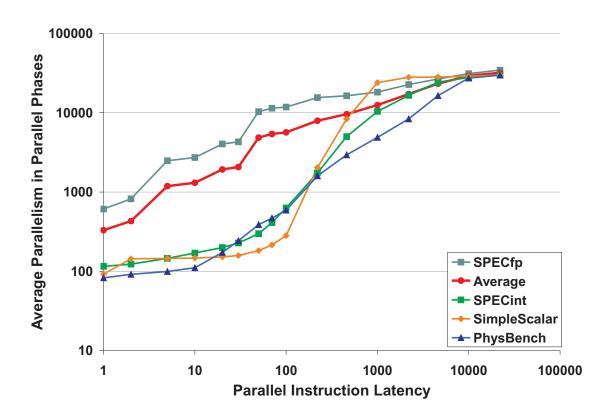

| 3.2  | Average Parallelism of Our Benchmark Set                                                  | 63 |

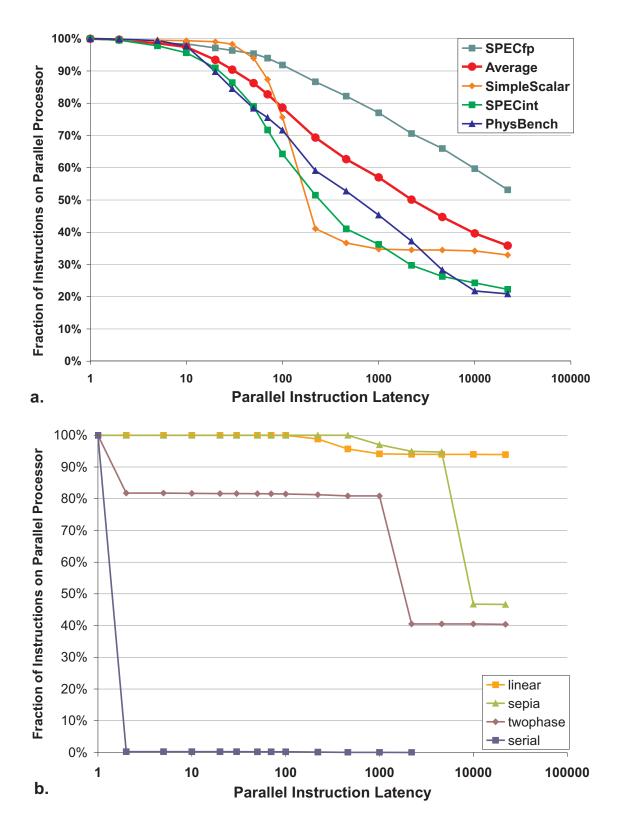

| 3.3  | Proportion of Instructions Scheduled on Parallel Core. Real benchmarks (a),               |    |

|      | Microbenchmarks(b)  .  .  .  .  .  .  .  .  .                                             | 66 |

| 3.4  | Average Parallelism on Parallel Processor                                                 | 67 |

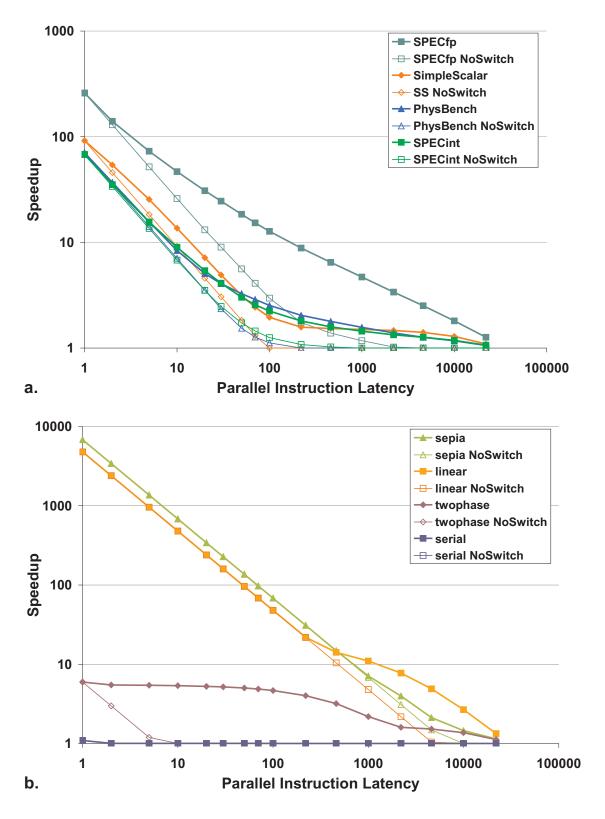

| 3.5  | Speedup of Heterogeneous System. Traces show speedup for ideal com-                       |    |

|      | munication (solid) and with communication forbidden (dashed, NoSwitch).                   |    |

|      | Real benchmarks (a), Microbenchmarks (b)                                                  | 69 |

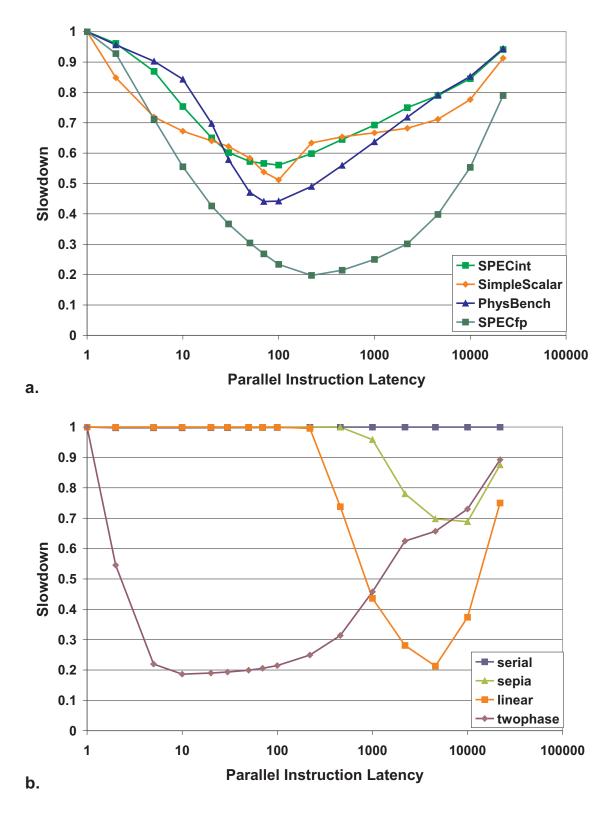

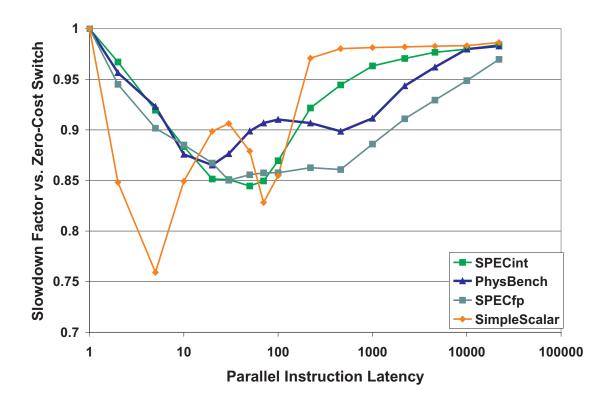

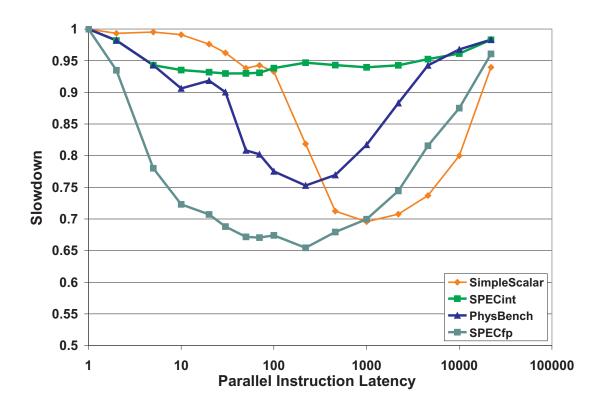

| 3.6  | Slowdown of infinite communication cost (NoSwitch) compared to zero com-                  |    |

|      | munication cost. Real benchmarks (a), Microbenchmarks (b)                                 | 71 |

| 3.7  | Slowdown due to 100,000 cycles of mode-switch latency. Real benchmarks                    | 72 |

| 3.8  | Slowdown due to a bandwidth constraint of 8 cycles per 32-bit value and                   |    |

|      | 1,000 cycles latency, similar to PCI Express x16. Real benchmarks                         | 74 |

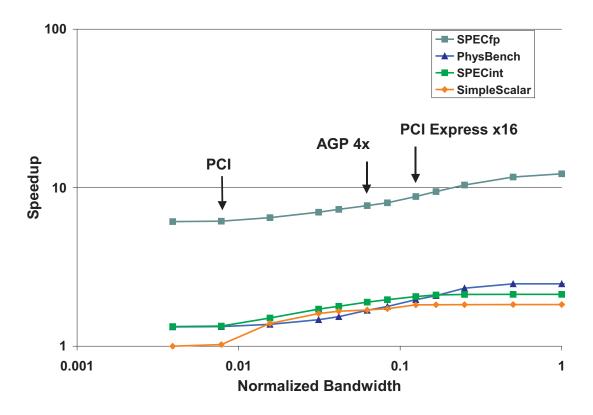

| 3.9  | Speedup over sequential processor for varying bandwidth constraints. Real                 |    |

|      | benchmarks                                                                                | 75 |

| 3.10 | Heterogeneous system area, normalized to area of sequential processor. $\ . \ . \ .$      | 79 |

| 3.11 | Normalized area efficiency. Real benchmarks                                               | 80 |

## List of Figures

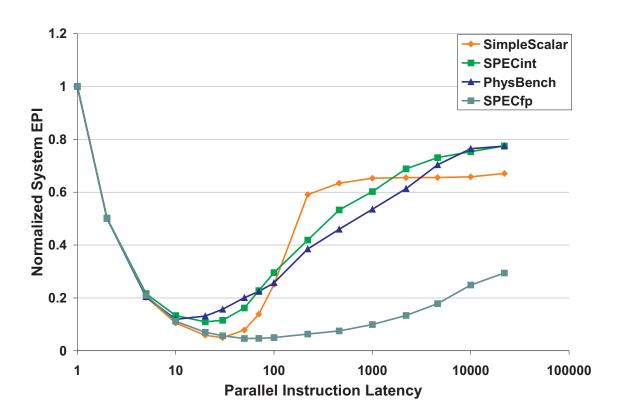

| 3.12 Normalized energy per instruction (EPI). Real benchmarks 8 |

|-----------------------------------------------------------------|

|-----------------------------------------------------------------|

# Acknowledgements

I would like to thank my thesis supervisor Tor Aamodt for the guidance throughout my masters career. Thanks also go to Steve Wilton and Sathish Gopalakrishnan for their comments and feedback during the thesis defense process.

Thanks also goes to Wilson Fung, off whom I had bounced many ideas and had many thought-provoking and insightful discussions over the last two years, and for proofreading the thesis.

I would also like to thank Intel Microarchitecture Research Lab for providing me with the opportunity to conduct research in an industrial setting. Particular thanks goes to Hong Wang and Anne Bracy for the guidance throughout the project.

I acknowledge the financial support from the Natural Sciences and Engineering Research Council of Canada (NSERC) during my masters program.

# Statement of Co-Authorship

Pangaea (Chapter 2) was work done while on internship at Microarchitecture Research Labs, Intel Corp. The architecture was conceived by colleagues at MRL, and refined by me to suit implementation constraints as work proceeded. The FPGA prototype of the heterogeneous system was designed and built by me from existing CPU and GPU code. Data analysis was performed by me. The Pangaea manuscript was co-authored with colleagues at MRL and Tor Aamodt.

The limit study (Chapter 3) experiment was designed collaboratively by Tor Aamodt and I. The research, data collection and analysis, and manuscript preparation were done by me.

## Chapter 1

# Introduction

#### 1.1 Motivation

As we continue to be able to put an increasing number of transistors on a single chip, what we build using these resources continually changes. One question is whether we should devote increasing resources to improving serial performance using larger processors or to increasing parallelism with more processors.

Amdahl [1] argued in 1967 that the correct method of improving computer performance was to build ever-faster uniprocessors, as the now-famous Amdahl's Law shows that a program's sequential fraction will dominate runtime if sequential performance improvements were neglected. The argument for building large uniprocessors was again made in 1997 [2], arguing that multiple processor cores ought to be placed on separate chips because communication latency is more tolerable *between* processors than *within* a processor, and that we should build the largest uniprocessor that is possible on a single chip, and use multiple chips for parallelism.

Gustafson [3] argues against Amdahl's Law in 1988 that increasing problem sizes result in increasing parallelism with a roughly constant sequential fraction, thus justifying large multiprocessor systems. A more recent appeal for single-chip multiprocessor parallelism was made in 1996 [4], noting that improving uniprocessor performance was achieving diminishing returns.

One example of the effective use of a single-chip multiprocessor system is in commodity 3D graphics accelerators. Graphics processing units (GPUs) are chips specialized to implement 3D graphics acceleration as dictated by 3D APIs like OpenGL or DirectX. The

abundance of parallelism in the workload naturally led to highly-parallel architectures.

GPUs became programmable by adding support for various types of programmable shaders in the graphics APIs and the development of high-level shader programming languages [5, 6]. Being programmable, GPUs began to be interesting for unintended uses [7, 8, 9]. Many of these early general-purpose (GPGPU) applications involved linear algebra.

Originally, GPGPU applications were limited to using graphics APIs, using programmable shaders embedded within the standard graphics pipeline defined by the APIs. For non-graphics purposes, this presented an unnecessary overhead layer between the application and the hardware doing the computation. This was also difficult to use, as it required the developer with no interest in graphics to understand graphics APIs.

Some of the overhead of graphics APIs is reduced with the introduction of compute-oriented APIs like Nvidia's CUDA [10] or ATI's Stream SDK [11], which allow access to the computation cores in a GPU bypassing the graphics API.

These APIs allowed the GPU to be programmed directly and relatively easily, but the GPU still is treated as a device, its memory space separate from that used by the CPU. GPUs are still difficult to program as the developer needs to manually copy data between the CPU and GPU, and programs on the GPU can not invoke operating system services. The EXO [12] architecture reduces programmer effort by providing the appearance of a shared memory space and supports exception handling by signaling the CPU to perform address translation and exception handling on behalf of the GPU. The GPU hardware still maintained all the hardware overhead needed to support graphics APIs.

In Chapter 2, we address some of these problems and present a heterogeneous multicore chip architecture, *Pangaea*, that further tightly-couples GPU cores with the CPU. Pangaea proposes to integrate the processing cores from a GPU with a CPU on a single chip, removing hardware support for legacy graphics APIs (reducing overhead), and sharing cache and memory hierarchy between the two core types. Fast communication between CPU and GPU cores would be done using proposed x86 ISA extensions which enable user-

level interrupts implemented on top of existing cache coherence mechanisms. Removing graphics-specific hardware results in significant area and power reductions.

Although we show that Pangaea succeeds in reducing communication latency between CPU and GPU, the performance impact is small for highly-parallel applications that can tolerate communication latency (and memory latency too, as the GPU philosophy goes).

This motivates an exploration of designs *and applications* around the design point presented by Pangaea. We want to find the potential impact of communication and GPU core characteristics on performance, as well as which types of applications are sensitive to these design choices. In our limit study (Chapter 3), we attempt to measure the potential impacts of communication latency and bandwidth for general-purpose applications, without requiring that they be manually parallelized.

Our limit study finds that when algorithms are optimally partitioned between GPU-and CPU-like processors, the performance impacts of communication latency and bandwidth are not large. Despite traditional wisdom, we notice many implementations of applications for GPUs do not report CPU-GPU communication as a major limiter of performance [13]. We also find that despite the optimistic assumptions made in our limit study, many general-purpose applications do not have sufficient parallelism to create thousands or millions of threads to be used by the GPU to tolerate long register read-after-write latencies, leaving GPUs under-utilized due to insufficient parallelism in the application.

#### 1.2 Thesis Contributions

We summarize the contributions of this thesis here:

- We propose an architecture for GPU compute only, which achieves tighter coupling with the CPU by sharing memory hierarchy and leveraging cache coherency mechanisms for fast user-level signaling. (Chapter 2)

- We prototype a Pangaea design on an FPGA using RTL code from an IA32 CPU core and the Intel GMA X4500 GPU.

- We show that removing support for the legacy graphics pipeline and sharing of memory hierarchy with the CPU result in significant area and power savings, and significantly reduced communication latency.

- To explore the design and application space around Pangaea, our limit study abstractly models a GPU and CPU heterogeneous system, using an algorithm that extracts parallelism from applications and optimally schedules instructions onto the two processor types. (Chapter 3)

- Our limit study models GPU register read-after-write latency and a constrained CPU-GPU communication channel, and shows that the register read-after-write latency of GPU cores is a significant limiter of achievable speedup, while CPU-GPU communication latency and bandwidth only have minor effects on achievable performance.

- We use area and power efficiency metrics with our limit study data to propose designs for GPU core properties that maximize efficiency. We observe that for area efficiency, GPU cores with higher register read-after-write latency than today's GPU cores are optimal, while optimal power efficiency requires GPU cores with lower read-after-write latency.

The rest of the thesis is structured as follows. We present a background on GPU computation and related work in the following sections (Sections 1.3 and 1.4). In Chapter 2 we propose and evaluate the Pangaea architecture. In Chapter 3 we explore the CPU-GPU design space in our limit study. We conclude in Chapter 4.

## 1.3 Background on GPU Computation

#### 1.3.1 GPU Organization

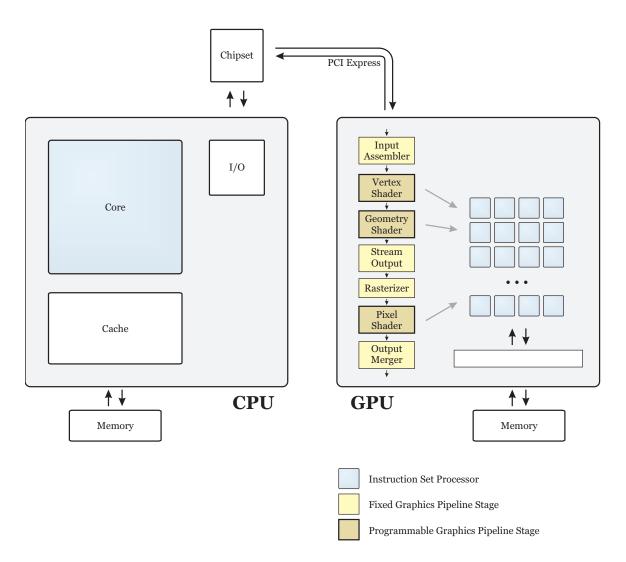

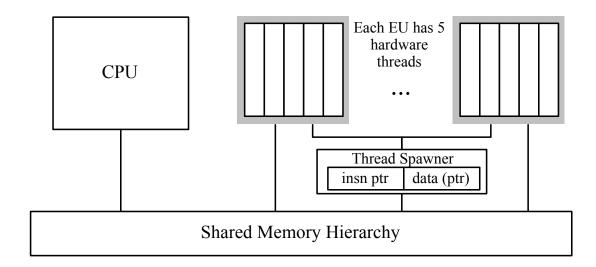

Figure 1.1 shows the general system organization of a modern discrete GPU, used in conjunction with a traditional CPU-based system.

The intended use of graphics processors is to accelerate 3D graphics rendering. This is often done using a standard graphics API like OpenGL or DirectX [14]. Graphics APIs present a pipeline where vertices are manipulated, rasterized, textured, and output to the frame buffer to be displayed on a bitmapped display. The DirectX 10 [14] pipeline stages (Input Assembler through Output Merger) are shown in Figures 1.1 and 1.2. Although it is possible to render 3D graphics in software on the CPU, the processing performed by the rendering pipeline is usually offloaded to the graphics processor (GPU), which is designed specifically to implement the rendering pipeline, and provides a large performance improvement.

When rendering, the graphics driver running on the host operating system is responsible for interfacing between the graphics API runtime and the GPU hardware. Data and commands are sent from driver software running on the CPU to the GPU over the PCI Express bus, which is then processed by the hardware.

#### 1.3.2 Programmability

Modern rendering pipelines have increased in programmability. Figure 3.1 shows the rendering pipeline stages which are programmable. The *Vertex Shader* and *Geometry Shader* stages take each vertex as input then runs a short program transforming each one. The *Pixel Shader* stage takes each pixel fragment as input, and likewise runs a short program on each to transform it. As vertices and pixels are essentially mutually independent, multiple instances of shaders can execute in parallel, which encourages highly parallel hardware designs. In a typical GPU, there is an array of multi-threaded, SIMD processing cores which executes the shader programs. These cores are architected to exploit the available parallelism to get the most throughput in the least area. The graphics driver is responsible for translating vendor-neutral shader code into the device-specific instruction set.

Figure 1.1: Discrete GPU Organization

#### 1.3.3 Computation

Early efforts at GPU computation took advantage of the programmable shaders. Computation problems were mapped into graphics rendering problems, and shaders were written which achieve the desired computation rather than output a rendered image. This approach leaves the hardware organization unchanged. Drawbacks include the requirement that a computation be mapped onto vertex and pixel primitives, and that some stages of the rendering pipeline are irrelevant to the desired computation and is thus wasted area, power, and possibly performance.

#### 1.3.4 CUDA, ATI Stream

Some of the problems of mapping computations to shaders can be avoided by allowing the use of the array of cores by programs without using the graphics API, allowing computation to be specified directly in programs without remapping into vertices and pixels [10, 11]. The hardware organization remains nearly unchanged from Figure 1.1, but a new mechanism to use the array of cores needs to be added (not shown). Since graphics remains the main usage of GPUs, all of the hardware to support graphics is left intact and simply left unused as appropriate.

#### 1.3.5 CPU-GPU Integration

As seen in Figure 1.1, a discrete GPU is typically attached to the CPU system over an off-chip PCI Express bus. Discrete GPUs typically have their own memory, physically separate from the CPU's memory, and data is transferred by copying over the PCI Express bus using DMA. Current integrated GPUs are integrated into the chipset and use a portion of the CPU's memory instead of having its own dedicated memory. This results in lower cost in exchange for a performance penalty. The general architecture is otherwise similar.

One issue with off-chip buses is their high latency and limited bandwidth [15]. This thesis explores in Chapter 3 the impact that this latency and limited bandwidth can have on performance. One solution to this issue is to integrate the GPU on the same chip as the

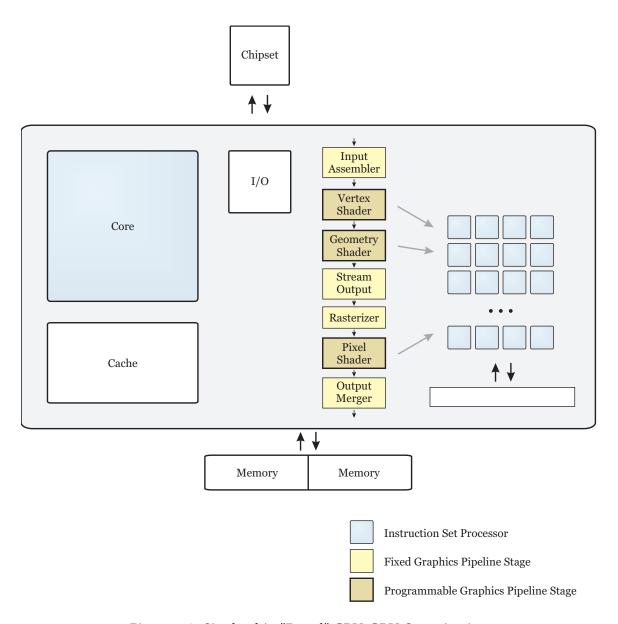

Figure 1.2: Single-chip "Fused" CPU-GPU Organization

CPU.

There are planned products which integrate CPU and GPU on the same chip [16]. One possible arrangement is shown in Figure 1.2. Unlike the discrete GPU, communication between CPU and GPU is now on chip, and no longer across an off-chip PCI Express bus. As the GPU still appears to the system as a graphics device, memory is logically separate, although it would likely share the physical memory array with the CPU. Graphics-specific hardware is left intact, as such a system is intended to support 3D rendering. This arrangement is referred to as the *fused* GPGPU organization in Chapter 2.

The Nvidia CUDA and AMD Stream enhancements allowing direct use of the core array are also applicable to single-chip CPU-GPU multiprocessors.

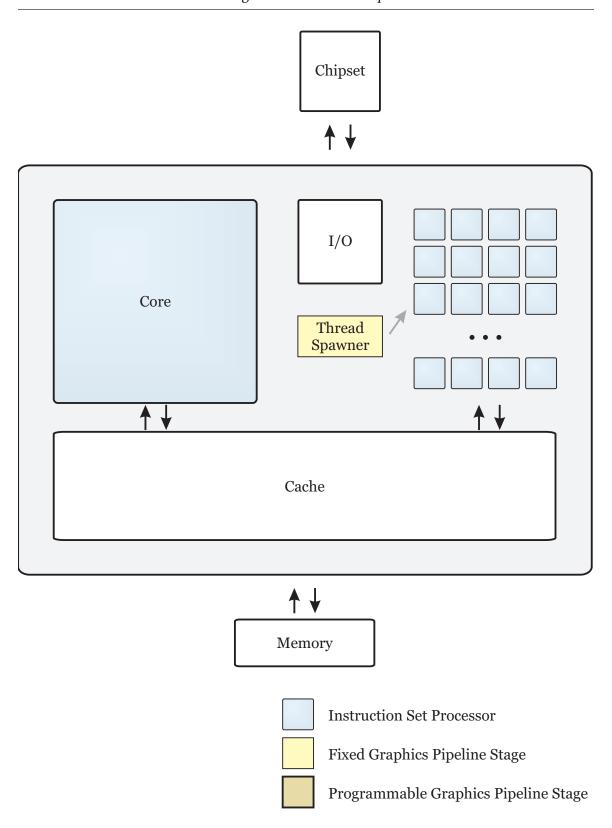

#### 1.3.6 Pangaea Preview

Extending the integration further, Pangaea proposes to support only general-purpose computation, and removes graphics-specific hardware to save area and power. It is also proposed that memory address space be shared between the parallel cores and the CPU, and that communication occur through cache coherence mechanisms. Sharing a cache allows fast data sharing and reuse between CPU and the GPU-like core array. See Chapter 2 for details.

Figure 1.3: Single-chip Pangaea CPU-GPU Organization

#### 1.4 Related Work

#### 1.4.1 Multicore Processors

In the beginning von Neumann [17] created the processor. "I'll take one," Amdahl said [1]. "I'll take more," said Gustafson [3]. "Give me some on a chip," says Olukotun [4]. Patt objected [2], "Only one on a chip." AMD [18] and Intel [19] disagreed and gave everyone two on a chip. And then more [20], perhaps even a thousand someday [21].

Homogeneous Multicore Current personal computer systems use homogeneous multicore processors, where two or more processors of the same microarchitecture are placed on a single chip. Oluktun et al. [4] make the argument that given diminishing returns of improving single-processor performance, multiple processors on a chip provide better performance in many cases.

Indeed, single-processor scaling has been shown historically to be fairly poor, with performance increasing approximately proportional to the square root of resources (area, power) used. This is Pollack's Rule [21]. Multiple cores have the potential to scale throughput linearly as the area and power consumed.

Heterogeneous Multicore As opposed to homogeneous systems, heterogeneous systems use two or more types of processor cores in a system. As programs have both parallel and sequential phases, it makes intuitive sense that in order to prevent Amdahl's Law from limiting speedup, a fast sequential processor should exist to run sequential portions of programs.

Kumar *et al.* showed that single-ISA heterogeneous systems using different microarchitectures implementing the same instruction set can reduce power consumption [22] at little performance loss compared to a single high-performance processor. They also showed improved performance [23] when running multiprogrammed workloads compared to a homogeneous multicore system of equivalent area.

Later work arrive at similar conclusions. Growchowski *et al.* [24] report improved performance under a fixed power budget, and Annavaram *et al.* [25] demonstrate a prototype.

Kumar *et al.* also try to choose processor core sizes in a four-core single-ISA heterogeneous system to optimize for one set of multiprogrammed workloads [26]. They conclude that a homogeneous multiprocessor system outperforms the best homogeneous system, and chooses parameters that optimize the cores for the chosen workload.

Past work has focused mainly on single-ISA systems and single-threaded or multiprogrammed workloads with few cores. In CPU-GPU heterogeneous systems the ISAs of the two processors differ: The GPU uses an ISA specialized for supporting graphics. The GPU is also far more parallel than the ~4 thread contexts considered in earlier work, while the single-thread sequential performance of GPU relative to the CPU is far greater than between CPUs of varying microarchitectures (typically 100x between GPU and CPU).

This thesis concerns heterogeneous systems with a single-threaded CPU core and a highly parallel GPU-like core, with parallelism and performance characteristics more extreme than earlier work considers.

#### 1.4.2 GPU Compute

Ever since graphics processors (GPU) became programmable, there has been interest in using it for computation beyond its intended use of 3D graphics rendering. Initially, custom computation was essentially hacked into the standard graphics pipeline by transforming the desired computation into a rendering computation, but recent hardware has allowed programming the GPU directly.

**GPGPU using shaders** General-purpose programming of GPUs started when GPUs incorporated various programmable "shaders" into the graphics pipeline. OpenGL and Direct3D defined virtual machine-like models for shaders. High-level languages were also defined to ease programming. Examples include GLSL [6] for use with OpenGL, HLSL for Direct3D, and Nvidia's Cg [5] which can target both APIs.

Early GPGPU work usually involved building algorithm primitives like sorting or applications using linear algebra [27, 28]. Sparse matrix solvers [7, 8] seemed especially popular. One example of an application of sparse matrix solutions is quadratic cell placement [9].

General-purpose Languages Programming within a graphics model when working on a general-purpose program is inconvenient. There have been some attempts at abstracting away the graphics pipeline by providing a more general programming environment (usually C-like) that is then compiled for execution by the GPU shaders. Examples include Brook for GPUs [29] and Accelerator [30]. Note that although these languages can abstract away the graphics pipeline from the developer, the compiled program is still compiled to shader programs within a graphics pipeline, and retain any related overheads.

ClawHMMER [31] is an example application using Brook.

**Unified Shaders** The increasing number stages of the graphics pipeline that became programmable (vertex, pixel, and, in DirectX 10, geometry shaders) eventually led to the definition of a unified shader model, instead of different shader models for each type of shader. DirectX 10's Shader Model 4.0 [14] requires unified shaders.

**GPU Compute Hardware** Unified shaders with increasing programmability naturally led to the desire to use them outside the graphics pipeline. Using the shader cores directly can improve performance by avoiding translation/compilation from vendor-neutral shader code into the native instruction set of the GPU cores. It also avoids the programming complexity of trying to fit a general-purpose problem into a graphics-specific programming model.

Nvidia's CUDA [10] and ATI's CTM [11] allow programming of their respective GPUs without using the graphics API. CUDA presents a C-like programming environment, reducing programming complexity. However, much of the complexity caused by constraints inherent in the GPU cores' architecture remains that the developer still needs to consider,

for example SIMD width, VLIW scheduling of instructions, or matching the number of threads and registers used to hardware capabilities.

The relative ease of use of CUDA led to many applications [13, 32, 33]. It is interesting to note that the communication latency and bandwidth over PCI Express is not a major limiter on performance [13], an observation also seen in our limit study (Chapter 3).

**Unified Programming Model** Even with CUDA, programming GPUs is not easy. As the GPU is viewed as a device in a CPU-based system, memory spaces are separate and the developer needs to manage data copying between CPU and GPU memory. Programs on GPUs also are unable to use OS services on their own.

Efforts to improve ease of programming have involved defining new programing model that can target both CPU and GPU implementations [34, 35], so that a program need only be written once. Another approach involves making the GPU programming model more similar to the existing CPU model, for example the Exoskeleton Sequencer (EXO) architecture [12]. EXO gives the illusion of a shared memory space between GPU and CPU and allows exception handling in GPU code using Address Translation Remapping and Collaborative Exception Handling, where the CPU handles page faults and other exceptions on behalf of the GPU.

**Unified Hardware: CPU-GPU integration** Commercial products integrating the GPU and CPU (single package or single chip) are expected to be available soon [16]. Although likely lower in raw performance than a discrete GPU due to more stringent area and power constraints, CPU-GPU integration offers interesting possibilities in supporting a unified programming model.

Pangaea goes further than simple integration of GPU and CPU, but proposes that the GPU be specialized for parallel compute only. Pangaea follows the EXO shared-memory model, but also physically shares parts of the memory hierarchy, and adds mechanisms for fast communication between CPU and GPU.

#### 1.4.3 Limit Studies on parallelism

Single Processor One of the early limit studies on available parallelism in programs was done by Wall [36]. He reports fairly low available parallelism (~5-7), due mainly to branch mispredictions. The poor results due to branch prediction prompted Lam and Wilson's study [37] on the effects on available parallelism of various control flow constraints (prediction and/or condition dependence) and allowing multiple fetch streams, using a similar methodology. This study finds that multiple fetch streams and condition dependence analysis unlock much of the parallelism available (40 for integer and 561 for floating-point applications).

**Thread-Level Speculation** There have also been limit studies modeling the potential benefits of thread-level speculation machines [38, 39]. These placed additional constraints on the model used by Lam and Wilson's work.

Homogeneous Multiprocessor With the recent trend toward multicore processors, there is an interest in evaluating the potential performance in parallelizing existing applications. The limit study by Vachharajani *et al.* [40] uses a similar methodology to earlier work, but adds various scheduling algorithms that distribute instructions from a single thread among processors in a homogeneous multiprocessor system. They find that there is significant parallelism in ordinary applications when parallelized for homogeneous multiprocessor systems, but find that communication latency between cores is a significant limiter of performance.

We are not aware of prior limit studies that attempt to model *heterogeneous* systems where some processors are faster than others, which is characteristic of GPU-based compute systems.

# References

- [1] G. M. Amdahl. Validity of the single-processor approach to achieving large scale computing capabilities. In *AFIPS Conference Proceedings vol.* 30, pages 483–485, 1967.

- [2] Y.N. Patt, S.J. Patel, M. Evers, D.H. Friendly, and J. Stark. One Billion Transistors, One Uniprocessor, One Chip. *Computer*, 30(9):51–57, Sep 1997.

- [3] J. L. Gustafson. Reevaluating Amdahl's Law. *Communications of ACM*, 31(5):532–533, 1988.

- [4] K. Olukotun, B. A. Nayfeh, L. Hammond, K. Wilson, and K. Chang. The case for a single-chip multiprocessor. In *ASPLOS-VII: Proc. 7th international conference on Architectural support for programming languages and operating systems*, pages 2–11, New York, NY, USA, 1996. ACM.

- [5] William R. Mark, R. Steven Glanville, Kurt Akeley, and Mark J. Kilgard. Cg: a system for programming graphics hardware in a C-like language. *ACM Trans. Graph.*, 22(3):896–907, 2003.

- [6] John Kessenich, Dave Baldwin, and Randi Rost. The OpenGL Shading Language, version 1.20. http://www.opengl.org/registry/doc/GLSLangSpec.Full.1.20.8.pdf, Sept. 2006.

- [7] Jeff Bolz, Ian Farmer, Eitan Grinspun, and Peter Schröoder. Sparse matrix solvers on the GPU: conjugate gradients and multigrid. In *SIGGRAPH '03: ACM SIGGRAPH 2003 Papers*, pages 917–924, New York, NY, USA, 2003. ACM.

- [8] Nico Galoppo, Naga K. Govindaraju, Michael Henson, and Dinesh Manocha. LU-GPU: Efficient Algorithms for Solving Dense Linear Systems on Graphics Hardware. In SC '05: Proceedings of the 2005 ACM/IEEE conference on Supercomputing, page 3, Washington, DC, USA, 2005. IEEE Computer Society.

- [9] Guilherme Flach, Marcelo Johann, Renato Hentschke, and Ricardo Reis. Cell placement on graphics processing units. In SBCCI '07: Proceedings of the 20th annual conference on Integrated circuits and systems design, pages 87–92, New York, NY, USA, 2007. ACM.

- [10] Nvidia. Compute Unified Device Architecture Programming Guide Version 2.0. http://developer.download.nvidia.com/compute/cuda/2.0-Beta2/docs/Programming\_Guide\_2.0beta2.pdf.

- [11] J. Hensley. Close to the Metal. ACM SIGGRAPH 2007 courses, course 24 article 7, 2007.

- [12] Perry H. Wang, Jamison D. Collins, Gautham N. Chinya, Hong Jiang, Xinmin Tian, Milind Girkar, Nick Y. Yang, Guei-Yuan Lueh, and Hong Wang. EXOCHI: architecture and programming environment for a heterogeneous multi-core multithreaded system. In PLDI '07: Proceedings of the 2007 ACM SIGPLAN conference on Programming language design and implementation, pages 156–166, New York, NY, USA, 2007. ACM.

- [13] Shane Ryoo, Christopher I. Rodrigues, Sara S. Baghsorkhi, Sam S. Stone, David B. Kirk, and Wen-mei W. Hwu. Optimization principles and application performance evaluation of a multithreaded GPU using CUDA. In *PPoPP '08: Proceedings of the 13th ACM SIGPLAN Symposium on Principles and practice of parallel programming*, pages 73–82, New York, NY, USA, 2008. ACM.

- [14] David Blythe. The Direct3D 10 system. ACM Trans. Graph., 25(3):724-734, 2006.

- [15] B. Holden. Latency Comparison Between Hyper-Transport and PCI-Express in Communications Systems. http://www.hypertransport.org/docs/wp/Latency\_Comparison \_HyperTransport\_PCIe\_in\_Communications\_Systems.pdf.

- [16] AMD. 2007 Financial Analyst Day. http://download.amd.com/Corporate/MarioRivasDec2007AMDAnalystDay.pdf, 2007.

- [17] John von Neumann. First Draft of a Report on the EDVAC. Technical report, Moore School of Electrical Engineering, University of Pensylvania, June 1945.

- [18] AMD. AMD "Shatters The Hourglass" With The Arrival Of The AMD Athlon 64 X2 Dual-Core Processor. http://www.amd.com/us-en/Corporate/VirtualPressRoom/0,,51\_104\_543~98647,00.html, May 2005.

- [19] O. Wechsler. Inside Intel Core Microarchitecture: Setting New Standards for Energy-efficient Performance. http://download.intel.com/technology/architecture/new\_architecture\_06.pdf, 2006.

- [20] AMD. Family 10h AMD Phenom Processor Product Data Sheet. http://www.amd.com/us-en/assets/content\_type/white\_papers\_and\_tech\_docs/44109.pdf, November 2007.

- [21] S. Borkar. Thousand Core Chips A Technology Perspective. In *Proc. 44th Annual Conference on Design Automation*, pages 746–749, 2007.

- [22] Rakesh Kumar, Keith I. Farkas, Norman P. Jouppi, Parthasarathy Ranganathan, and Dean M. Tullsen. Single-ISA Heterogeneous Multi-Core Architectures: The Potential for Processor Power Reduction. In MICRO 36: Proceedings of the 36th annual IEEE/ACM International Symposium on Microarchitecture, page 81, Washington, DC, USA, 2003. IEEE Computer Society.

- [23] Rakesh Kumar, Dean M. Tullsen, Parthasarathy Ranganathan, Norman P. Jouppi,

- and Keith I. Farkas. Single-ISA Heterogeneous Multi-Core Architectures for Multithreaded Workload Performance. In *ISCA '04: Proceedings of the 31st annual international symposium on Computer architecture*, page 64, Washington, DC, USA, 2004. IEEE Computer Society.

- [24] E. Grochowski, R. Ronen, J. Shen, and Hong Wang. Best of both latency and throughput. Computer Design: VLSI in Computers and Processors, 2004. ICCD 2004. Proceedings. IEEE International Conference on, pages 236–243, Oct. 2004.

- [25] Murali Annavaram, Ed Grochowski, and John Shen. Mitigating Amdahl's Law through EPI Throttling. In *ISCA '05: Proceedings of the 32nd annual international symposium on Computer Architecture*, pages 298–309, Washington, DC, USA, 2005. IEEE Computer Society.

- [26] Rakesh Kumar, Dean M. Tullsen, and Norman P. Jouppi. Core architecture optimization for heterogeneous chip multiprocessors. In *PACT '06: Proceedings of the 15th international conference on Parallel architectures and compilation techniques*, pages 23–32, New York, NY, USA, 2006. ACM.

- [27] Dinesh Manocha. General-Purpose Computations Using Graphics Processors. *Computer*, 38(8):85–88, 2005.

- [28] John D. Owens, David Luebke, Naga Govindaraju, Mark Harris, Jens Krüger, Aaron E. Lefohn, and Timothy J. Purcell. EUROGRAPHICS 2005 STAR State of The Art Report A Survey of General-Purpose Computation on Graphics Hardware, aug 2005.

- [29] Ian Buck, Tim Foley, Daniel Horn, Jeremy Sugerman, Kayvon Fatahalian, Mike Houston, and Pat Hanrahan. Brook for GPUs: stream computing on graphics hardware. In SIGGRAPH '04: ACM SIGGRAPH 2004 Papers, pages 777–786, New York, NY, USA, 2004. ACM.

- [30] David Tarditi, Sidd Puri, and Jose Oglesby. Accelerator: using data parallelism to

- program GPUs for general-purpose uses. *SIGARCH Comput. Archit. News*, 34(5):325–335, 2006.

- [31] Daniel Reiter Horn, Mike Houston, and Pat Hanrahan. ClawHMMER: A Streaming HMMer-Search Implementatio. In SC '05: Proceedings of the 2005 ACM/IEEE conference on Supercomputing, page 11, Washington, DC, USA, 2005. IEEE Computer Society.

- [32] Samuel S. Stone, Justin P. Haldar, Stephanie C. Tsao, Wen-mei W. Hwu, Zhi-Pei Liang, and Bradley P. Sutton. Accelerating Advanced MRI Reconstructions on GPUs. In *CF* '08: Proceedings of the 2008 conference on Computing frontiers, pages 261–272, New York, NY, USA, 2008. ACM.

- [33] L. Nyland, M. Harris, J. Prins. Fast N-Body Simulation with CUDA. *GPU Gems* 3, 2007.

- [34] Michael D. Linderman, Jamison D. Collins, Hong Wang, and Teresa H. Meng. Merge: A Programming Model for Heterogeneous Multi-core Systems. In *ASPLOS XIII: Proceedings of the 13th international conference on Architectural support for programming languages and operating systems*, pages 287–296, New York, NY, USA, 2008. ACM.

- [35] Michael D. McCool, Kevin Wadleigh, Kevin Wadleigh, Brent Henderson, and Hsin-Ying Lin. Performance evaluation of GPUs using the RapidMind development platform. In SC '06: Proceedings of the 2006 ACM/IEEE conference on Supercomputing, page 181, New York, NY, USA, 2006. ACM.

- [36] David W. Wall. Limits of instruction-level parallelism. In ASPLOS-IV: Proceedings of the fourth international conference on Architectural support for programming languages and operating systems, pages 176–188, New York, NY, USA, 1991. ACM.

- [37] M. S. Lam, R. P. Wilson. Limits of control flow on parallelism. In *Proc. 19th International Symposium on Computer Architecture*, pages 46–57, 1992.

- [38] Nakajima Akio, Kobayashi Ryotaro, ANDO HIDEKI, and SHIMADA TOSHIO. Limits of Thread-Level Parallelism in Non-Numerical Programs. *IPSJ Transactions on Advanced Computing Systems*, 47(SIG 7(ACS14)), May 2006.

- [39] Katsuhiko Metsugi and Kazuaki Murakami. Limits of Parallelism on Thread-Level Speculative Parallel Processing Architecture. In *International Workshop on Information and Electrical Engineering (IWIE2002)*, May 2002.

- [40] N. Vachharajani, M. Iyer, C. Ashok, M. Vachharajani, D. I. August, D. Connors. Chip multi-processor scalability for single-threaded applications. *ACM SIGARCH Computer Architecture News*, 33(4):44–53, 2005.

## Chapter 2

# Pangaea: A Tightly-Coupled IA32 Heterogeneous Chip Multiprocessor<sup>1</sup>

#### 2.1 Introduction

As Moore's Law pushes for a more rapid pace of silicon development and even higher degree of on-die integration, the number of cores in future multi-core designs will continue to increase. As the microprocessor industry rapidly marches into the era of multi-core design, the future generation of multi-core processors will essentially become an integration platform with not only numerous cores, but also different types of cores varying in functionality, performance, power, and energy efficiency [1]. Fundamentally, ultra low EPI (Energy Per Instruction) cores are essential to scale multi-core processor designs to incorporate a large number of cores. One approach to improving EPI by an order of magnitude is through heterogeneous multi-core designs, which have a small number of large, general-purpose cores optimized for instruction-level parallelism (ILP) and many more special-purpose cores optimized for data-level parallelism (DLP) and thread-level parallelism (TLP). Such a multi-core processor offers opportunities for non-graphics application software and usage models [2, 3, 4, 5, 6, 7] to aggressively exploit the combination of ILP, DLP and TLP.

In this paper we present Pangaea, a synthesizable design of a heterogeneous chip mul-

<sup>&</sup>lt;sup>1</sup>To appear in Proceedings of Parallel Architectures and Compilation Techniques (PACT 08), Toronto, Ontario, Canada

Henry Wong, Anne Bracy, Ethan Schuchman, Tor M. Aamodt, Jamison D. Collins, Perry H. Wang, Gautham Chinya, Ankur Khandelwal Groen, Hong Jiang, Hong Wang. Pangaea: A Tightly-Coupled IA32 Heterogeneous Chip Multiprocessor. In *Proceedings of Parallel Architectures and Compilation Techniques*, October 2008, Toronto, Ontario, Canada.

tiprocessor (CMP) that integrates IA32 CPU cores with GPU multi-cores. Architected to support general-purpose parallel computation, Pangaea goes beyond the current stateof-the-art CPU-GPU integration that physically "fuses" an existing CPU design and an existing GPU design on the same die. In Pangaea, new enhancements are introduced to both the CPU and GPU to support tighter architectural integration, improved area and power efficiency, and scalable modular design. On the CPU side, a three-instruction extension to the IA32 ISA supports a fly-weight communication mechanism between the CPU and the GPU and a fine-grain shared memory collaborative multithreading environment between the IA32 CPU cores and the GPU multi-cores. This ISA enhancement allows an IA32 thread to directly spawn user-level threads to the GPU cores, bypassing most of the legacy graphics specific fixed-function hardware (e.g., input assembler, vertex shader, rasterization, pixel shader, output merger [8]) found in a modern GPU design. This can achieve a two-order of magnitude reduction in thread spawning latency. On the GPU side, a state-of-the-art existing GPU design (Intel GMA X4500 [9]) is rearchitected to significantly reduce the fixed-function hardware, which is traditionally dedicated to support 3D-specific graphics processing. The legacy front-end is replaced with a small FIFO controller that can buffer and dispatch GPU threads spawned by the IA32 CPU. The legacy back-end is replaced by sharing the memory hierarchy between the IA32 CPU and the GPU multi-cores. The removal of the legacy fixed-function hardware can result in area savings (on a 65 nm process) equivalent to nine additional GPU cores (of five hardware threads each) and power savings equivalent to five GPU cores.

This paper makes the following contributions:

- We describe the architecture support and microarchitecture reorganization of both CPU and GPU in Pangaea to achieve tighter architecture integration and power and area efficiency of a heterogeneous CMP design.

- We detail a fully functional synthesizable implementation of a Pangaea design, based on production quality RTL from an ILP optimized IA32 core and the GMA X4500 GPU.

- We present an in-depth analysis of architectural tradeoffs between the Pangaea design and a state-of-the-art design that physically fuses existing CPU and GPU on the same die.

- We report significant performance gains for a set of media and non-graphics parallel applications by employing Pangaea to harvest ILP, DLP and TLP, achieving speedups of up to 8.8×.

The rest of the paper is organized as follows. Section 2.2 reviews related work. Section 2.3 provides a background on baseline GPU architecture. Section 2.4 introduces the architectural enhancements to the IA32 CPU and the microarchitectural reorganization of the X4500 GPU to support tighter architectural integration. Section 2.5 details the implementation of Pangaea and assesses the key architectural tradeoffs in terms of power and area savings compared to the state-of-the-art CPU-GPU design with physical fusion. Section 2.6 evaluates the performance of a set of general-purpose applications on a Pangaea hardware prototype on an FPGA-based emulator. Section 2.7 concludes.

#### 2.2 Related Work

We adopt the distinction between *asymmetric* and *heterogeneous* multi-core designs from related work [7, 10]. All cores in an *asymmetric* multi-core design are of the same ISA but differ microarchitecturally. In a *heterogeneous* multi-core design, some cores feature different ISAs in addition to microarchitectural differences. Prior work on multi-core architectures has demonstrated significant benefits for both power/performance and area/performance efficiency [10, 11, 12, 13, 14, 15, 16, 17, 18, 19]. However, those studies primarily focus on asymmetric rather than heterogenous multi-core design.

Heterogeneous multi-core designs integrate cores of different ISAs and functionalities and can potentially lead to even further improvement in power/area/performance efficiency. IBM Cell's heterogeneous architecture [20] offers a mix of execution elements optimized for a spectrum of functions. Applications execute on this system, rather than a col-

lection of individual cores, by partitioning the application and executing each component on the most appropriate execution element. The *exoskeleton sequencer* (EXO) architecture [7] presents heterogeneous cores as MIMD function units to the IA32 CPU and provides architectural support for shared virtual memory, ensuring efficient data sharing across the heterogeneous execution elements.

Recently, both AMD and Intel have made public announcements on their upcoming mainstream heterogeneous processor designs for the 2009-10 timeframe. These processors will be on-die integrations of the IA32 CPU and their respective GPUs, which are traditionally found on the chipset or in discrete GPU cards. The so-called *fusion* integration physically connects existing CPU and GPU designs and supports some level of cache sharing between them, while the designs themselves remain unchanged. Although the integrated GPU is intended to run the legacy graphics software stack, there has been growing interest in harvesting such heterogeneous multi-core processors to accelerate non-graphics applications. Furthermore, there have been extensive efforts to provide programming model abstractions and runtime support to ease the otherwise daunting task for programmers to use heterogeneous multi-cores [4, 5, 6, 21].

Although heterogeneous integration is key to Pangaea, Pangaea is different than fused designs in that it supports a tighter-coupled integration through lightweight user-level interrupts. Bracy *et al.* discuss these lightweight user-level interrupts and utilize existing coherency logic to provide simple, preemptive, low-latency communication between cores [22]. Many other microarchitectures also support preemptive communication [23, 24, 25, 26, 27, 28, 29, 30, 31].

### 2.3 Background

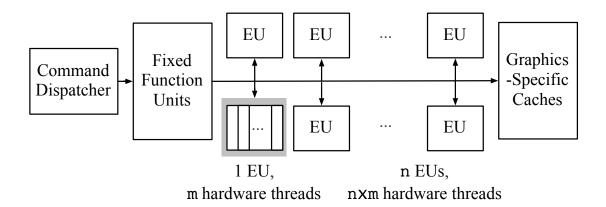

This section provides some necessary background on GPU architecture and defines terminology that will be used in the following sections. Figure 2.1 depicts an architectural organization of a modern GPU. It consists of three major components (from left to right):

• Front-end: a graphics-specific pipeline ensemble of fixed-function units, each corre-

Figure 2.1: Organization of the Intel GMA X4500.

sponding to a certain phase of the pixel and vertex processing primitives, *e.g.*, command streamer, vertex fetcher, vertex shader, clipper, strip/fan, windower/masker, roughly in correspondence to DirectX's input assembler, vertex shader, rasterization, pixel shader, and output merger [8], respectively. The front-end translates graphics commands into threads that can be run by the processing cores.

- Processing multi-cores: hereafter referred to as Execution Units (EU). This is where

most GPU computations are performed. Each EU usually consists of multiple SMT

hardware threads, each implementing a wide SIMD ISA. In the GMA X4500, each

thread supports 8-wide SIMD operations.

- **Back-end:** consists of graphics-specific structures like render cache, etc., which are responsible for marshalling data results produced by the EUs back to the legacy graphics pipeline's data representation.

Non-graphics communities are understandably interested in harvesting the massive amount of thread level and data-level parallelism offered by the EU to accelerate general-purpose computation, for which the graphics specific hardware front-end and back-end are largely overhead. The GPU is managed by device drivers that run in a separate memory space from applications. Consequently, communication between an application and the GPU usually requires device driver involvement and explicit data copying. This results in

additional latency overhead due to the software programming model.

Pangaea assumes the EXO execution model that supports user-level shared memory heterogeneous multithreading and an integrated programming environment such as *C* for Heterogeneous Integration (CHI) [7] that can produce a single fat binary consisting of multiple code sections of different instruction sets that target different cores. The focus of our study of the Pangaea design space is to investigate architectural improvements beyond the physical on-die fusion of existing CPUs and GPUs and to assess the power/area/performance efficiency using production quality RTL for both an IA32 CPU design and a modern multi-core multithreaded GPU design. The proposed architecture enhancements to both the CPU and GPU can enable much more efficient software management of parallel computation across heterogeneous cores. By minimizing resources dedicated solely to 3D-specific graphics processing, significant improvements in area and power efficiency can be achieved.

# 2.4 Pangaea Architecture

This section introduces Pangaea's architecture enhancements to the IA32 CPU and architectural reorganization of the X4500 GPU to support tighter architectural integration.

# 2.4.1 CPU-GPU Integration

Pangaea is a novel CPU-GPU integration architecture design that removes the legacy graphics front-end and back-end of the traditional GPU design to enhance general-purpose (non-graphics) computation. With architectural support for shared memory and a fly-weight user-level inter-core communication mechanism, Pangaea provides a tightly-coupled architectural integration of CPU and GPU EUs to more efficiently support collaborative heterogeneous multithreading between GPU threads and CPU threads.

Figure 2.2 shows a high level diagram of the Pangaea architecture. Pangaea physically couples a set of EUs directly with each CPU via an agile thread spawning interface, but

Figure 2.2: Pangaea: Integrated CPU-GPU without Legacy Graphics Front- and Back-End. without the legacy graphics front-end and back-end. Each EU works as a TLP/DLP coprocessor to the CPU. This mechanism allows for a more power and area efficient design, which maximizes the utilization of the massively-parallel ALUs packed in the EUs.

The shared cache supports the collaborative multithreading relationship (peer-to-peer or producer-consumer) between the CPU and EUs. Both CPU and EU cores fetch their instructions and data from the shared memory. The common working sets between CPU threads and EU threads benefit from the shared cache. Enabling a coherent shared address space also make it easier to build a simple communication mechanism between the CPU and EU cores. The communication mechanism between the CPU and EU cores is introduced as an ISA extension.

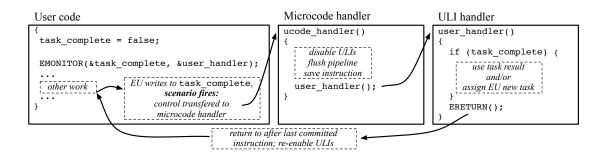

In Panagea, the EUs appear as additional function units to which threads can be dispatched from the CPU. The CPU is responsible for both assigning and monitoring the GPU's work. The CPU can receive results from the GPU as soon as they are ready and schedule new threads to the GPU as soon as EU cores become idle. Inter-processor interrupts (IPIs) have often been leveraged for cross-core communication, but they introduce performance overheads that are not appropriate in the intended fine grained multi-

Figure 2.3: Example of User-Level Interrupt (ULI).

threaded environment of Pangaea. Instead of using IPIs, Pangaea leverages simple and fast *user-level interrupts* (ULIs) which are discussed in the next section. A fast mechanism is desirable as the EU threads are short lived and each EU thread processes only a small amount of data. The CPU spawns a large number of threads to increase the resource utilization of the EUs which are optimized for DLP and TLP.

Sections 2.4.2 and 2.4.3 describe the IA32 ISA extension that supports a user-level communication mechanism between the CPU and EUs. Section 2.5 presents an analysis of the power and area efficiency of Pangaea versus the fusion design.

# 2.4.2 ISA Extension for User-level Interrupts

Pangaea introduces a three-instruction IA32 ISA extension that supports communication between heterogeneous cores. The three instructions are **EMONITOR**, **ERETURN**, and **SIGNAL**. The communication mechanism is as follows.

A *scenario* is a particular machine event that may occur (or *fire*) on any core. Example scenarios include an invalidation of a particular address, an exception on an EU, or termination of a thread on an EU. **EMONITOR** allows application software to register interest in a particular scenario and to specify a user-defined software handler to be invoked (via user-level interrupt (ULI)) when the scenario fires. This scenario-to-handler mapping is stored in a new form of user-level architecture register called a *channel*. Multiple channels allow multiple scenarios to be monitored simultaneously.

When the scenario fires, the microcode handler disables future ULIs, flushes the pipeline, pushes the current interrupted instruction pointer onto the stack, looks up the instruction pointer for the user-defined handler associated with the channel, and redirects program flow to that address. The change in program control flow is similar to what happens when an interrupt is delivered. The key difference is that the ULI is handled completely in user mode with minimal state being saved/restored when the user-level interrupt handler is invoked.

**ERETURN** is the final instruction of the user-defined handler. It pops the stack and returns the processor to the interrupted instruction while re-enabling ULIs.

Figure 2.3 shows an example of using ULIs. On the left and right is code provided by software. In the middle is the microcode handler. Software activates a channel by executing the EMONITOR instruction, registering its interest in invalidations to the task\_complete variable and providing the handler that should be called when the invalidation occurs. In this example—one of many possible usage models—the user code spawns a task to the EU and then performs other work. When the EU completes its task, it writes to the variable task\_complete which is being monitored and the scenario fires. The microcode handler invokes the user-defined interrupt handler. The user's handler can use the result of the EUs immediately and/or assign the EU another task. The user's handler ends with ERETURN. The program then returns to the instruction just after the last committed instruction prior to the interrupt and the user code continues its work. Other usage models might have the EU's task completion affect the user code's behavior upon returning from the interrupt.

To spawn a thread to the EU, the CPU stores the task (including an instruction pointer to the task itself and a data pointer to the possible task input) at an address monitored by the *Thread Spawner*, shown in Figure 2.2. The Thread Spawner is directly associated with the thread dispatcher hardware on the EUs. The CPU then executes the SIGNAL instruction—the third ISA extension—to establish the signaling interface between the CPU and EU.

As in related work [10], the SIGNAL instruction is a special store to shared memory

that the CPU uses to spawn EU threads. Using SIGNAL, the EUs can be programmed to monitor and snoop a range of shared addresses similar to SSE3's MONITOR instruction [32]. Upon observing the invalidation caused by the CPU's SIGNAL, the Thread Spawner loads the task information from the cache-line payload. The Thread Spawner then enqueues the EU thread into the hardware FIFO in the EU's thread dispatcher, which binds a ready thread to a hardware thread core (EU), and then monitors the completion of the thread's execution.

Upon recognizing the completion of a thread, the Thread Spawner performs a final store (here, writing to task\_complete) that results in the scenario firing, as shown in Figure 2.3. The CPU thread can schedule and dispatch more EU threads in response (not shown).

Because the thread spawning and signaling interface between the CPU and EUs leverages simple loads and stores, it can be built as efficiently as regular cache coherence with very low on-chip latencies.

A similar fly-weight signaling mechanism is also used in hardware to implement the exoskeleton *proxy execution* mechanism [7]. In Pangaea the IA32 CPU handles exceptions and faults incurred on the GMA X4500 cores for *address translation remapping* and *collaborative exception handling* using proxy execution. These mechanisms are essential to support a shared virtual address space between the IA32 CPU and the GMA X4500 cores.

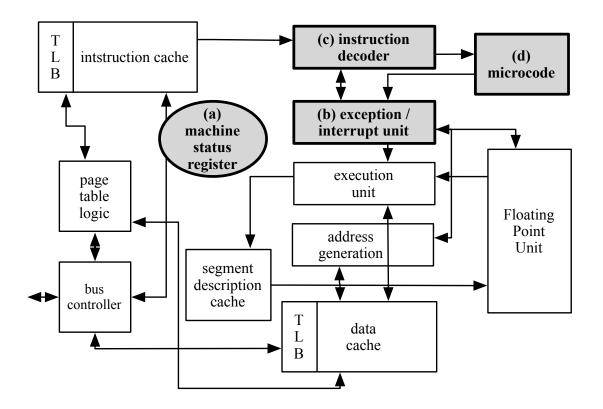

Figure 2.4 shows the microarchitecture block diagram of the IA32 core used for this study. The darkened units were modified to support ULIs. First, new registers are introduced to support multiple channels (shown in Figure 2.4(a)). Each channel holds a mapping between a user handler's starting address and the associated ULI scenario. A register is used to hold a blocking bit which specifies if ULIs are temporarily disabled. Since the channel registers store application specific state, these registers need to be saved and restored across OS thread context switches along with any active EU thread context. Existing IA32 XSAVE/XRSTOR instruction support can be modified to save and restore additional state across context switches [33]. These registers can be read and written under

Figure 2.4: IA32 CPU Block Diagram. Shaded blocks indicate modifications to support ULI.

the control of microcode.

The exception/interrupt unit (shown in Figure 2.4(b)) handles all interrupts and faults, and determines whether instructions should be read from the instruction decoder or the microcode. This unit is modified to recognize ULI scenarios. A new class of interrupt request, ULI-YIELD, triggers at the firing of a scenario and requests a microcode control-flow transfer to the ULI microcode handler. This interrupt is handled in the integer pipeline. All state logic associated with the ULI-YIELD, determining when an ULI-YIELD should be taken, and saving pending ULI-YIELD events is found here. Because the ULI-YIELD request has the lowest priority of all interrupt events, ULIs do not interfere with traditional interrupt handling. Once the ULI-YIELD has priority, the exception/interrupt unit flushes the pipeline and jumps to the ULI microcode handler. If multiple channels are im-

plemented, when multiple instances of ULI-YIELD interrupts simultaneously occur, lower indexed channels have higher priority over higher indexed channels.

The instruction decoder (shown in Figure 2.4(c)) is responsible for decoding instructions and providing information needed for the rest of the CPU to execute the instruction. The decoder is modified to add entry points for the new IA32 instructions EMONITOR, ERETURN and SIGNAL. These changes map the CPU instructions to the corresponding microcode flows in the microcode. The microcode (shown in Figure 2.4(d)) is modified to contain the ULI microcode handler and the microcode flows for EMONITOR, ERETURN and SIGNAL. The ULI microcode handler flow saves the current instruction pointer by pushing it onto the current stack, sets the blocking bit to prevent taking recursive ULI events, and then transfers control to the user-level ULI handler. The EMONITOR microcode flow registers a scenario and the user handler instruction pointer in the ULI channel register. The ERETURN microcode flow pops the saved instruction pointer off the stack, clears the blocking bit and finally transfers control to the main user-code where it starts re-executing the interrupted instruction.

In Pangaea, we introduce a ULI scenario, ADDR-INVAL, which architecturally represents an invalidation event incurred on a range of addresses, which resembles the behavior of a user-level version of the MONITOR/MWAIT instruction in SSE3. Unlike MWAIT [32], when the IA32 CPU in Pangaea snoops a store to the monitored address range, the CPU will activate the ULI microcode handler and transfer program control to the user-level ULI handler. To implement a producer-consumer workload using a traditional polling model, the producer regularly reads a designated semaphore address, checking for a value indicating that the consumer has completed its task. With the ADDR-INVAL ULI, the producer sets up a ULI channel to monitor future asynchronous updates to a semaphore and then proceeds to work on other tasks in parallel while the hardware performs the monitoring. When a consumer writes to the semaphore indicating task completion, this triggers the ADDR-INVAL ULI scenario and the producer is informed of this asynchronously. This ULI scenario is used for the signaling between the IA32 CPU cores, the thread spawner,

and the GMA X4500 EUs by leveraging the existing cache coherence protocol support, which is much more efficient than traditional IPI mechanisms that are sent via the interrupt controller. The address range that needs to be monitored is set up using the SIGNAL instruction which directly communicates with the thread spawner.

# 2.4.3 User-level Interrupt Handler

Certain precautions need to be taken in designing and writing a user-level interrupt handler as it runs in the context of the monitoring software thread. The monitoring software thread is the thread that executes the EMONITOR instruction and monitors the execution of the EU threads. The monitoring software thread runs on the IA32 CPU concurrently with the EU threads that run on the GPU. The user-level interrupts are delivered in the context of the monitoring thread without operating system intervention and they pre-empt the execution of the monitoring thread. Due to the pre-emptive nature of the user-level interrupt the user-defined interrupt handler should avoid attempting to acquire locks or invoke system calls that acquire locks as the monitoring thread may be executing in the middle of a critical section when it is pre-empted to execute the user-level interrupt handler. If the user-level interrupt handler attempts to acquire the same lock that has already been acquired then a deadlock results. An ideal user-level interrupt handler does not need to be complex or invoke system calls as the user-level interrupt handler is responsible for dispatching a new set of threads to the EU or resolving exception conditions for the EU threads to make forward progress. The user-level interrupt handler usually sets flags that are checked by the monitoring thread when exception conditions have to be resolved. An example of this is shown in Figure 2.3.

The user-level interrupt serves as a notification mechanism of a exception that needs to be resolved for the EU threads to make forward progress or to inform the monitoring thread about the termination of a group of EU threads. The monitoring thread can resolve the exception condition and then resume the EU thread at a later point in time. The interrupt mechanism is optional and the monitoring thread can always use the polling

| Parameter   | Configuration                                                           |

|-------------|-------------------------------------------------------------------------|

| IA32 CPU    | 2-issue, in-order, 4-wide SIMD capabilities, optimistically giving 4x   |

| IA32 CI U   | speedup over non-SIMD                                                   |

| CPU-only L1 | 8KB 2-cycle access write-back data cache, 8KB Instruction cache, 2-     |

| Caches      | way set associative                                                     |

|             | 2 EUs, 5 hardware threads each, 8-wide SIMD ISA, 4-wide SIMD ex-        |

| EUs         | ecution unit, 0 latency thread switch, 64 256-bit registers per thread. |

|             | Same clock speed as CPU                                                 |

| EU-only     |                                                                         |

| Instruction | 4KB shared instruction cache, 4-way set associative                     |

| Cache       |                                                                         |

| Shared L2   | 256KB shared with EU for EU instructions and data, 32-bits/clock        |

| Cache       | bandwidth, configurable access latency by EU (2 to >100 cycles)         |

Table 2.1: One Pangaea Prototype Configuration that fits one Xilinx Virtex-5.

mechanism to poll on the status of the EU threads by reading the channel registers which contain the scenarios that are being monitored as well as the current status of the scenario. The monitoring thread may attempt to just poll the channel registers when there is no more concurrent work to do or there is a need for a barrier synchronization between the monitoring thread and the EU threads.

The user-level interrupt handler is also responsible for saving and restoring the register state that is not saved/restored by the microcode handler. Since the user-level interrupt handler runs in the context of the monitoring thread it is safe to assume that the code segment or stack segment registers do not change after the monitoring thread executes the EMONITOR instruction as segmentation is not normally used for virtual memory management in modern operating systems. The only exception to this assumption is when the monitoring thread is running in compatibility 32-bit mode under a wrapper on a 64-bit operating system. A change in the code and stack segment occurs during transition from compatibility 32-bit mode to 64-bit mode in user space. The microcode handler is modified to suppress any user-level interrupts to be delivered when the code segment values do not match what was recorded when the EMONITOR instruction is executed. The delivery of the user-level interrupt is frozen for the duration of execution in 64-bit user mode. The EU threads that do not need to report any exceptions or terminate can continue to execute

even when the monitoring thread is executing in 64-bit user mode. When the monitoring thread returns from executing in 64-bit mode back to 32-bit mode the microcode detects the pending user-level interrupt and invokes the user-level interrupt handler. This simple mechanism is sufficient to allow 32-bit applications to continue to work when migrated to run on a 64-bit operating system that runs the application in compatibility mode.

The user-level interrupt mechanism provides a simple, fast and efficient core-to-core communication mechanism without having to introduce new interrupts that need device driver management or major changes to the interrupt controller.

# 2.5 Pangaea Implementation

To assess its power/area/performance efficiency, we implement a synthesizable design of Pangaea using production quality RTL for both an IA32 CPU design and a modern multicore multithreaded GPU design. This section describes the Pangaea implementation and prototyping on an FPGA. We also discuss the power/area efficiency analysis. Section 2.6 presents a performance evaluation of Pangaea using a set of non-graphics parallel workloads.

# 2.5.1 Pangaea's Synthesizable RTL Design

We build a prototype of the proposed Pangaea architecture by implementing synthesizable RTL of a fully functional single-chip heterogeneous CMP consisting of an IA32 CPU and GMA X4500 multi-cores (*i.e.*, EUs). The CPU used in our prototype (shown in Figure 2.4) is a production two-issue in-order IA32 processor equivalent to a Pentium with a 4-wide SSE enhancement. The EU is derived from the RTL for the full GMA X4500 production GPU. We configure our RTL to have two EUs, each supporting five hardware threads. While the baseline design is the physical fusion of the existing CPU and full GPU, in Pangaea much of the front-end and back-end of the GPU have been removed, keeping only the EUs and necessary supporting hardware. By attaching the EU onto the memory hierarchy of the

|              | LUTs  | Registers | Block RAMs | DSP48 blocks |

|--------------|-------|-----------|------------|--------------|

| IA32 CPU     | 50621 | 24518     | 118        | 24           |

| EU Subsystem | 84547 | 36170     | 67         | 64           |

| Other        | 1604  | 591       | 91         | 2            |

Table 2.2: Virtex-5 FPGA Resource Usage for the Pangaea configuration in Table 2.1.

CPU (sharing of the last-level cache), we no longer need to duplicate the hardware required for accessing and caching memory on the GPU. This prototype design provides means to adjust various configuration parameters, including capacities and access latencies for the memory hierarchy, number of EUs and number of hardware threads per EU. The RTL can be synthesized to either ASIC or FPGA targets.

Table 2.1 shows one particular design that can be synthesized to a Xilinx Virtex-5 XC5VLX330 FPGA using Synplify Pro 9.1 and Xilinx ISE 9.2.03i. Table 2.2 shows the resource usage as reported by Synplify Pro for our FPGA prototype. The IA32 core is larger than one EU, taking up approximately 24% of the 207,360 available FPGA 6-LUTs. As the table shows, the EU subsystem with 2 EUs is less than double the area IA32 CPU in our prototype. The impact from the modifications to the CPU to support ULIs (not shown) is negligible—on the order of 50 LUTs. The logic added to support the thread spawner (not shown) is only 2% of a single EU.