## Test and Fault-Tolerance for Network-on-Chip Infrastructures

by

Cristian Grecu

B.Sc., Technical University of Iasi, 1996

M.A.Sc., The University of British Columbia, 2003

### A THESIS SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENT FOR THE DEGREE OF

### DOCTOR OF PHILOSOPHY

in

The Faculty of Graduate Studies

(Electrical and Computer Engineering)

### THE UNIVERSITY OF BRITISH COLUMBIA (Vancouver)

November 2008

© Cristian Grecu, 2008

### Abstract

The demands of future computing, as well as the challenges of nanometer-era VLSI design, will require new design techniques and design styles that are simultaneously high-performance, energy-efficient, and robust to noise and process variation. One of the emerging problems concerns the communication mechanisms between the increasing number of blocks, or cores, that can be integrated onto a single chip. The bus-based systems and point-to-point interconnection strategies in use today cannot be easily scaled to accommodate the large numbers of cores projected in the near future. Network-on-chip (NoC) interconnect infrastructures are one of the key technologies that will enable the emergence of many-core processors and systems-on-chip with increased computing power and energy efficiency. This dissertation is focused on testing, yield improvement and fault-tolerance of such NoC infrastructures.

The motivation for the work is that, with technology scaling into the nanometer range, defect densities will become a serious challenge for fabrication of integrated circuits counting billions of transistors. Manufacturing these systems in high volumes can only be possible if their cost is low. The test cost is one of the main components of the total chip cost. However, relying on post-manufacturing test alone for guaranteeing that ICs will operate correctly will not suffice, for two reasons: first, the increased fabrication problems that are expected to characterize upcoming technology nodes will adversely affect the manufacturing yield, and second, post-fabrication faults may develop due to electromigration, thermal effects, and other mechanisms. Therefore, solutions must be developed to tolerate faults of the NoC infrastructure, as well as of the functional cores.

In this dissertation, a fast, efficient test method is developed for NoCs, that exploits their inherent parallelism to reduce the test time by transporting test data on multiple paths and testing multiple NoC components concurrently. The improvement of test time varies, depending on the NoC architecture and test transport protocol, from 2X to 34X, compared to current NoC test methods. This test mechanism is used subsequently to perform detection of NoC link permanent faults, which are then repaired by an on-chip mechanism that replaces the faulty signal lines with fault-free ones, thereby increasing the yield, while maintaining the same wire delay characteristics. The solution described in this dissertation improves significantly the achievable yield of NoC inter-switch channels – from 4% improvement for an 8-bit wide channel, to a 71% improvement for a 128-bit wide channel. The direct benefit is an improved fault-tolerance and increased yield and long-term reliability of NoC-based multicore systems.

# **Table of Contents**

| A | bstrac       | et                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ii  |

|---|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| T | able o       | f Contents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | iii |

| L | ist of '     | Fables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | v   |

| L | ist of ]     | Figures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | vi  |

|   |              | Acronyms and Abbreviations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

|   |              | vledgments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

| 1 |              | oduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

| T | 1.1          | Dissertation contribution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

| 2 |              | kground on Network-on-chip Testing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| 4 | 2.1          | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

|   | 2.1          | Multi-processor systems-on-chip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

|   | 2.2          | Networks-on-chip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

|   | 2.4          | Network-on-chip test – previous work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

|   | 2.5          | Fault models for NoC infrastructure test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

|   | 2.5.1        | Wire/crosstalk fault models for NoC inter-switch links                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 19  |

|   | 2.5.2        | 2 Logic/memory fault models for FIFO buffers in NoC switches                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 20  |

|   | 2.6          | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 23  |

| 3 | Tes          | t Time Minimization for Networks-on-Chip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 24  |

|   | 3.1          | Test data organization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 24  |

|   | 3.2          | Testing NoC switches                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 25  |

|   | 3.3          | Testing NoC links                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 26  |

|   | 3.4          | Test data transport                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 28  |

|   | 3.4.1        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

|   | 3.5          | Test scheduling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

|   | 3.5.1        | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |

|   | 3.5.2        | 1 .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

|   | 3.5.3        | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |

|   | 3.5.4        | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |

|   | 3.6<br>3.6.1 | Experimental results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

|   | 3.6.2        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

|   | 3.6.2        | $-\cdots$ $j$ $-\cdots$ $-\cdots$ $j$ $-\cdots$ $-\cdots$ $-\cdots$ $-\cdots$ $-\cdots$ $-\cdots$ $-\cdots$ $-\cdots$ |     |

|   | 3.7          | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

| Λ |              | It-tolerance Techniques for Networks-on-chip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

| 7 | 4.1          | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

|   | 4.2          | Traditional fault-tolerance metrics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

|   | 4.3          | Fault-tolerance metrics for network-on-chip subsystems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

|   | 4.4          | Metrics evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

|   | 4.5          | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

| 5 |              | lt-tolerant Global Links for Inter-core Communication in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

|   |              | ks-on-chip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 83  |

| 1 | 5.1          | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

|   | 5.1<br>5.2   | Related work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

|   |              | I VAAA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

| 5.3    | Problem statement                                                 |     |

|--------|-------------------------------------------------------------------|-----|

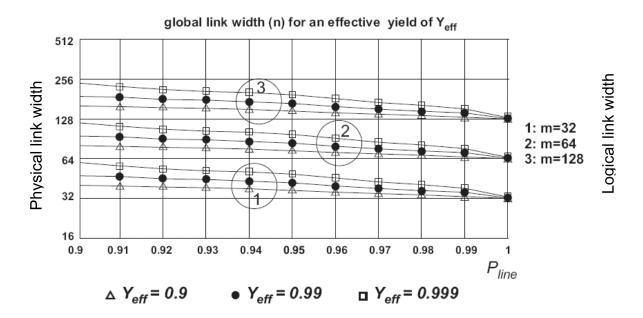

| 5.4    | Interconnect yield modeling and spare calculation                 |     |

| 5.5    | Fault-tolerant NoC links                                          |     |

| 5.6    | Sparse crossbar concentrators                                     |     |

| 5.7    | Fault tolerant global interconnects based on balanced crossbars   |     |

| 5.8    | Link test and reconfiguration mechanisms                          | 103 |

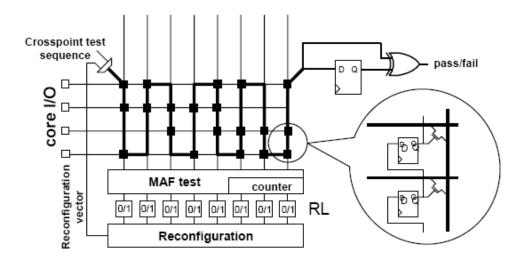

| 5.8    | 8.1 Testing the sparse crossbar matrix and interconnect wires     | 104 |

| 5.8    | 8.2 Link reconfiguration                                          | 107 |

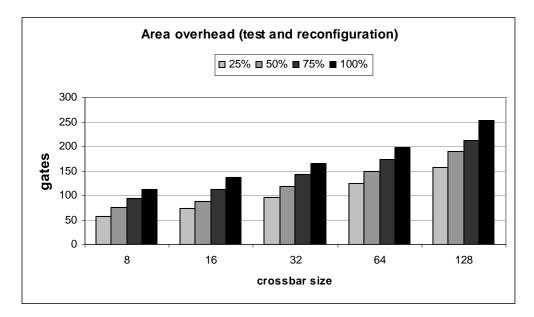

| 5.8    | 8.3 Yield, performance and cost analysis                          | 110 |

| 5.9    | Summary                                                           |     |

| 6 Ce   | onclusions                                                        | 115 |

| 6.1    | Summary of contributions                                          |     |

| 6.2    | Limitations                                                       |     |

| 6.3    | Future work                                                       |     |

| 7 Aj   | ppendices                                                         | 122 |

| 7.1    | Appendix 1: Proof of Correctness for Algorithms 1 and 2           | 122 |

| 7.2    | Appendix 2: Algorithm for balancing fault-tolerant sparse crossba |     |

| Refere | ences                                                             | 129 |

# List of Tables

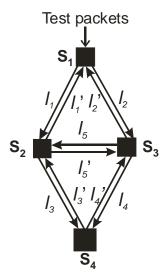

| Table 3-1: Unicast test data scheduling for the example in Fig. 3-7   | 44  |

|-----------------------------------------------------------------------|-----|

| Table 3-2: Multicast test data scheduling for the example in Fig. 3-7 |     |

| Table 3-4: Gate count and comparison for the proposed test mechanism  |     |

| Table 3-5: Test scheduling run-times                                  |     |

| Table 4-1: Detection latency (10-10 flit error rate)                  | 81  |

| Table 4-2: Recovery latency (10-10 flit error rate)                   | 81  |

| Table 5-1: Effective yield improvement vs interconnect complexity     | 111 |

| Table 5-2: Test and reconfiguration time overhead                     | 113 |

|                                                                       |     |

# List of Figures

| Figure 1-1: a) Regular NoC. b) Irregular NoC.                                                                       | 2  |

|---------------------------------------------------------------------------------------------------------------------|----|

| Figure 1-2: (a) Global links in NoC-based systems-on-chip; (b) global inter-con                                     |    |

| with m signal lines; (c) interconnect line spanning multiple metal/via level                                        |    |

| Figure 2-1: MP-SoC platform                                                                                         |    |

| Figure 2-2: Network-on-chip building blocks in a mesh configuration                                                 |    |

| Figure 2-3: Test configurations in [29]: (a) straight paths; (b) turning paths; (c)                                 |    |

| resource connections                                                                                                |    |

| Figure 2-4: Core-based test of NoC routers using an IEEE 1500 test wrapper a                                        |    |

| scan insertion [30]                                                                                                 |    |

| Figure 2-5: Test data transport for NoC router testing using (a) multicast and                                      |    |

| unicast [26]                                                                                                        | 17 |

| Figure 2-6: Examples of faults that can affect NoC infrastructures: (a) crossta                                     | lk |

| faults; (b) memory faults in the input/output buffers of the switches; (c)                                          |    |

| short/open interconnect faults; (d) stuck-at faults affecting the logic gates                                       | of |

| NoC switches.                                                                                                       | 18 |

| Figure 2-7: MAF crosstalk errors (Y <sub>2</sub> – victim wire; Y <sub>1</sub> , Y <sub>3</sub> – aggressor wires). |    |

| Figure 2-8: (a) 4-port NoC switch – generic architecture; (b) dual port NoC Fl                                      |    |

| Figure 3-1: Test packet structure                                                                                   |    |

| Figure 3-2: a) Wire i and adjacent wires; b) Test sequence for wire i; c) Conce                                     |    |

| state machine for MAF patterns generation.                                                                          | -  |

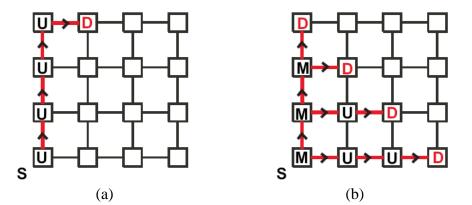

| Figure 3-3: (a) Unicast data transport in a NoC; (b) multicast data transport                                       |    |

| NoC (S – source; D – destination; U – switches in unicast mode; M – switches                                        |    |

| multicast mode).                                                                                                    |    |

| Figure 3-4: 4-port NoC switch with multicast wrapper unit (MWU) for test da                                         |    |

| transport.                                                                                                          |    |

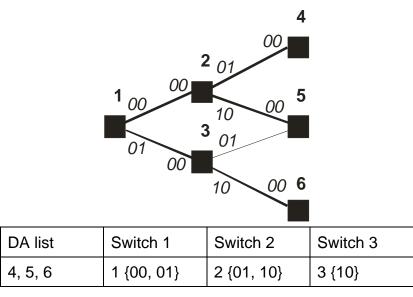

| Figure 3-5: Multicast route for test packets.                                                                       |    |

| Figure 3-6: (a), (b): Unicast test transport. (c) Multicast test transport                                          |    |

| Figure 3-7: 4-switch network with unidirectional links.                                                             |    |

| Figure 3-8: Test packets processing and output comparison                                                           |    |

| Figure 4-1: Processes communicating across a NoC fabric                                                             |    |

| Figure 4-2: Hierarchical partitioning for fault tolerant NoC designs                                                |    |

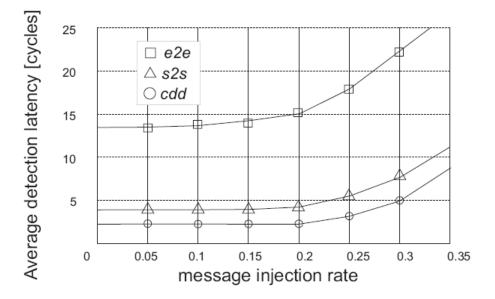

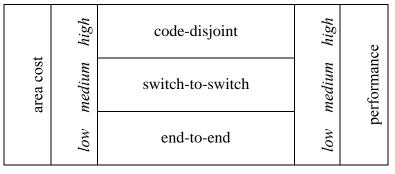

| Figure 4-3: Average detection latency for end-to-end (e2e), switch-to-switch (s                                     |    |

| and code-disjoint (cdd) detection schemes.                                                                          |    |

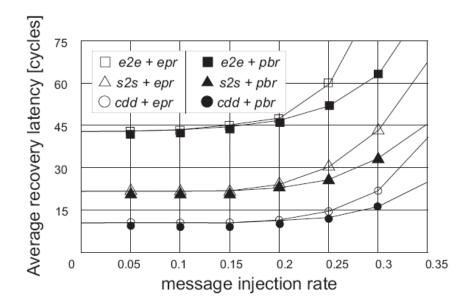

| Figure 4-4: Average recovery latency for equal priority recovery (epr) and pri                                      |    |

| based recovery (pbr).                                                                                               | v  |

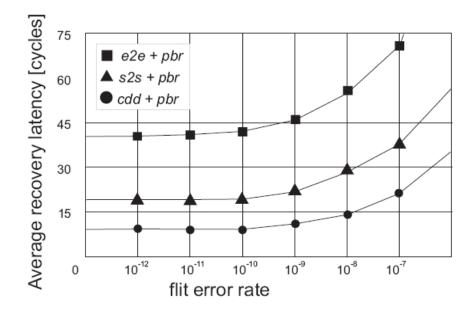

| Figure 4-5: Average recovery latency for pbr scheme with variable flit error r                                      |    |

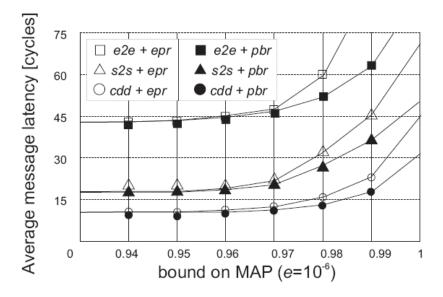

| Figure 4-6: Average message latency vs. bound on MAP.                                                               |    |

| Figure 4-7: Processes P <sub>1</sub> , P <sub>2</sub> mapped on a mesh NoC with QoS communication                   |    |

| constraints.                                                                                                        |    |

| Figure 4-8: Performance and cost of detection techniques.                                                           |    |

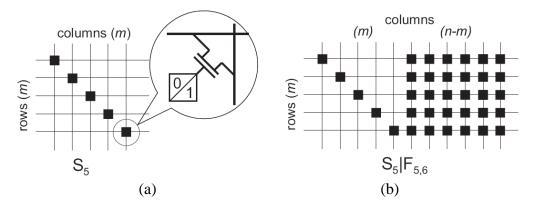

| Figure 5-1: (a) Non-fault-tolerant sparse crossbar and crosspoint implementat                                       |    |

| (b) n-m fault-tolerant sparse crossbar.                                                                             |    |

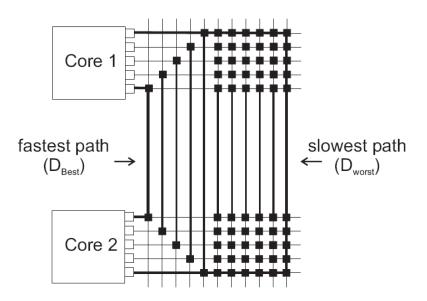

| Figure 5-2: Fastest and slowest propagation delay paths for non-balanced faul                                       |    |

| tolerant links.                                                                                                     |    |

|                                                                                                                     |    |

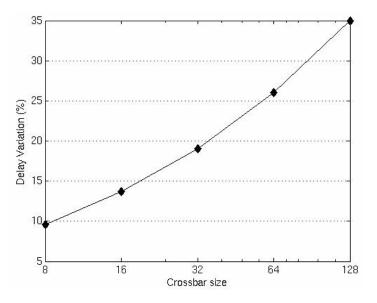

| Figure 5-3: Delay variation for imbalanced fault-tolerant links with 25%           |       |

|------------------------------------------------------------------------------------|-------|

| redundancy.                                                                        | 84    |

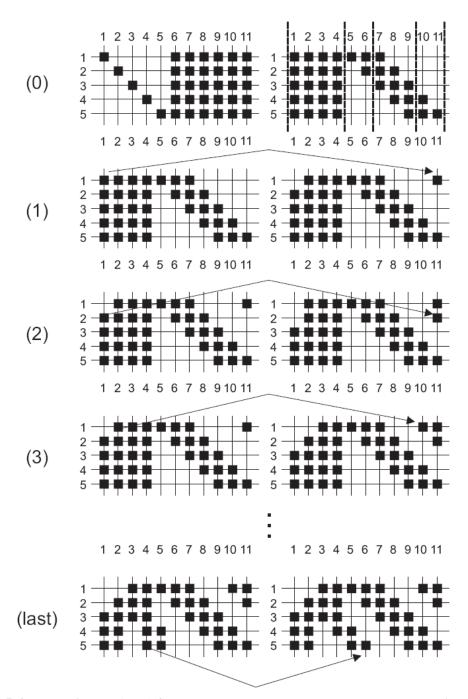

| Figure 5-4: Balancing an (n-m) fault-tolerant sparse crossbar through successiv    | ve    |

| column exchange operations; m=5, n=11                                              | 98    |

| Figure 5-5: Delay variation for balanced (b) links with 25% redundancy             | 100   |

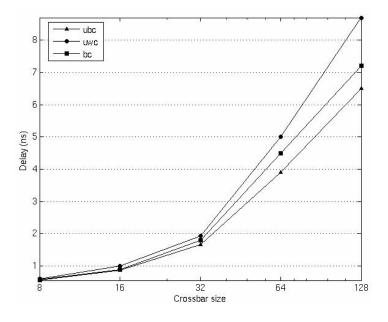

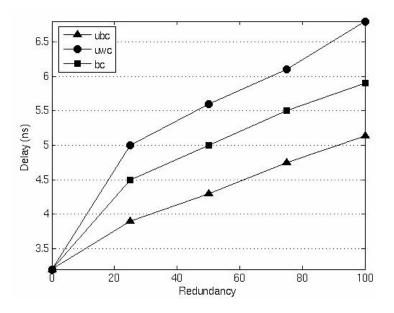

| Figure 5-6: Delay variation versus degree of redundancy for a 64-bit link          | 102   |

| Figure 5-7: Delay variation versus crossbar size and degree of redundancy          | 102   |

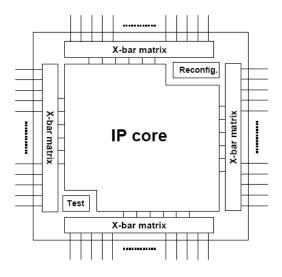

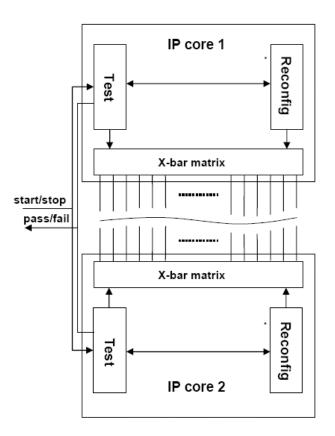

| Figure 5-8: Self-test and repair link architecture with shared test and            |       |

| reconfiguration blocks                                                             | 104   |

| Figure 5-9: Link-level test and reconfiguration.                                   | 105   |

| Figure 5-10: Test and reconfiguration hardware.                                    | 107   |

| Figure 5-11: Link reconfiguration algorithm.                                       | 108   |

| Figure 5-12: Physical link width (n) for different values of logic link width (m = | = 32, |

| 64, 128 bits) and target effective yield (Y <sub>eff</sub> ).                      | 110   |

| Figure 5-13: Area overhead for different crossbar sizes and degrees of redunda     | incy. |

| -                                                                                  | 112   |

# List of Acronyms and Abbreviations

ATE: Automated Test Equipment ATPG: Automated Test Pattern Generation CAD: Computer Aided Design CMOS: Complementary Metal Oxide Semiconductor CMP: Chip Multi-Processors CPU: Central Processing Unit DFT: Design for Test DFM: Design for Manufacturability DRC: Design Rule Checking DSP: Digital Signal Processor FIFO: First In First Out FO4: Fan-out of four FPGA: Field Programmable Gate Array IC: Integrated Circuit IP: Intellectual Property ISO: International Organization for Standardization ITRS: International Technology Roadmap for Semiconductors *I/O*: Input/Output MAF: Maximum Aggressor Fault MAP: Message Arrival Probability MP-SoC: Multi-processor System-on-chip MWU: Multicast Wrapper Unit NMR: N-Modular Redundancy *NoC*: Network-on-chip OSI: Open Systems Interconnection QoS: Quality of Services *RISC*: Reduced Instruction Set Computer *RLB*: Routing Logic Block *SoC*: System-on-chip TAM: Test Access Mechanism TTPE: Test Time per Element TT: Test Time

VLSI: Very Large Scale Integration

## Acknowledgments

I would like to thank my research supervisors, Professors André Ivanov and Resve Saleh, for their continued support along my graduate studies. Without their guidance and help, this work would have not been possible.

I would also like to thank my colleague and friend Partha Pande, for his advice, participation and help in my research.

Special thanks are due to my wife, Gabriela, who supported me unconditionally all these years.

This work was partially supported by NSERC of Canada and Micronet.

# Chapter 1

### **1** Introduction

The microprocessor industry is moving from a single-core processor to multi-core and, in the foreseeable future, to many-core processor architectures built with tens to hundreds of identical cores arranged as chip multi-processors (CMPs) [1]. Another similar trend can be seen in the evolution of systems-on-chip (SoCs) from singleprocessor systems with a set of peripherals to heterogeneous multi-core systems, composed of several different types of processing elements and peripherals (memory blocks, hardware accelerators, custom designed cores, input/output blocks, etc.) [2]. Microprocessor vendors are also venturing forwards to mixed approaches, combining multiple identical processors with different types of cores, such as the AMD Fusion family [3], which combines together multiple identical CPU cores and a graphics processor in one design.

Such multi-core, multi-processor systems, whether homogeneous, heterogeneous, or hybrid, must be interconnected in a manner that is high-performance, scalable, and reliable. The emerging design paradigm that targets such interconnections is called an onchip interconnection network, or network-on-chip (NoC). The basic idea of the NoC paradigm can be summarized as "route packets, not wires" [4]. Interconnecting cores through an on-chip network has several advantages over dedicated point-to-point or bus-based wiring, offering potential advantages in terms of high aggregate bandwidth, low communication latency, low power dissipation in inter-core communication, and increased scalability, modularity and flexibility.

The potential of NoCs is, however, far from being fully realized, and their practical implementation presents numerous challenges [5]. The first set of challenges is associated with meeting power/performance targets. The second set of issues relates to CAD tools and design methodologies to cope with the typical number of devices (in the range of one billion transistors or more), and the high degree of hardware and software parallelism that is characteristic of NoC-based systems.

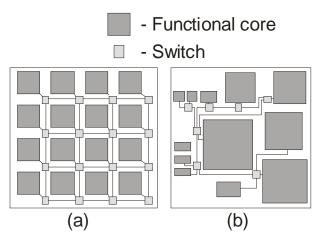

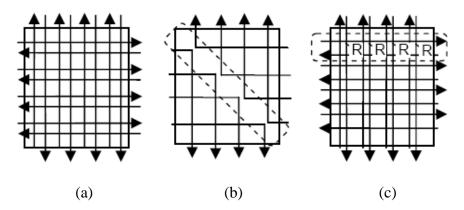

Network-on-chip architectures were proposed as a holistic solution for a set of challenges faced by designers of large, multi-core systems-on-chip. In general, two types of NoC architectures can be identified, as shown in Fig. 1-1: (a) regular interconnection structures derived from parallel computing, and (b) irregular, custom-built NoC fabrics. The infrastructure for NoC includes switches, inter-switch wires, interface blocks to connect to the cores, and a protocol for data transmission [6]. There is a significant number of active research efforts to bring NoCs into mainstream use [7].

Figure 1-1: a) Regular NoC. b) Irregular NoC.

The power dissipation of current NoC implementations is estimated to be significantly higher (in the order of 10 times or more) compared to the expected power budget of future CMP interconnects [5]. Both circuit-level and architecture-level techniques must be combined in order to reduce the power dissipation of NoC-based systems and their data-communication sub-systems to acceptable values.

The data transport latency of NoC infrastructures is too large for the current programming models, leading to significant performance degradation, especially in the case of on-chip memory access operations. Here, various research efforts are focused on reduced-latency router microarchitecture design [8], circuit techniques that reduce signal propagation time through NoC channels [9], and network architectures with reduced number of hops for latency-critical data transfers [10].

From a CAD perspective, most of the NoC architectures and circuit techniques are incompatible with the current design flows and tools, making them difficult to integrate in the typical SoC design flow. The fundamental reason is the high degree of parallelism at both computation and data transport levels, combined with the different ways in which the software and hardware components of a NoC interact with each other.

A major challenge that SoC designers are expected to face [11] is related to the intrinsic unreliability of the communication infrastructure due to technology limitations. Two different sources can be identified: random and systematic. The random defects arise from the contaminants, particles and scratches [12] that occur during the fabrication process. The systematic defects have roots in the photolithographic process, chemical-mechanical polishing methods and the continuous feature size shrinking in semiconductor fabrication technology. Chips are increasingly prone to feature corruption producing

shorts and opens in the wires, and missing vias, or vias with voids, as a result of photolithographic limitations. In addition, the effect of steps such as chemical-mechanical polishing may cause surface dishing through over-polishing, ultimately becoming important yield-loss factors [13].

Metal and via layers in advanced CMOS processes are characterized by defect densities correlated with their specific physical dimensions. Upper layers of metal tend to be wider and taller due to the expected current levels. The fabrication of wider wires does not present as much of a problem to photolithographic techniques; however, the vias tend to be tall and thin and are prone to voids. Therefore, via duplication or via arrays are employed to circumvent this issue.

Producing fine-lined wires presents the greatest challenge to the resolution of the most advanced photolithographic capabilities available today. Mitigating all these general observations is the fact that, in a typical foundry, older generations of equipment are used to fabricate the middle and upper layers of metal, each with their own yield characteristics. It is expected that the overall yield of interconnects will continue to decrease as the number of metal layers increases (e.g., 12 metal layers for 45 nm technology, compared with 9 layers for a typical 90nm process, and 5 layers for a 180nm process), as projected by the ITRS documents [14].

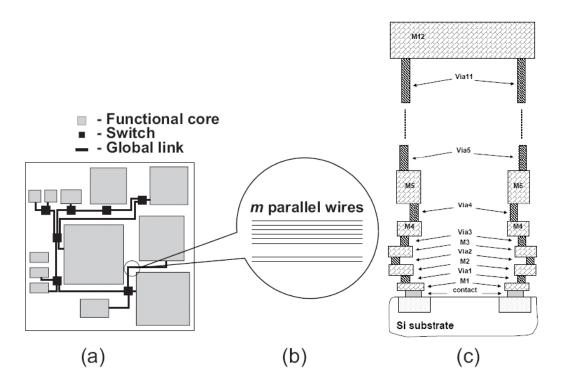

The impact on the overall yield of multi-core chips [15] can be quite significant, given that the data communication infrastructure alone can consume around 10-15% of the total chip area [16]. The inter-core communication links are likely to be routed on the middle and upper metal layers. Hence, the layout scenario is very similar to the example shown in Fig. 1-2, which illustrates a multi-processor SoC built on a network-on-chip

platform, consisting of functional cores, switching blocks and global links. The active devices (processing cores, memory blocks) are on the lower levels on the silicon surface, and the inter-core wires are on the higher levels of the 3D structure [17]. Global signal lines span more metal layers and require more levels of vias in order to go to/from the active devices on the silicon surface and therefore are more prone to manufacturing defects.

Figure 1-2: (a) Global links in NoC-based systems-on-chip; (b) global inter-core link with m signal lines; (c) interconnect line spanning multiple metal/via levels.

Many authors have tried to make the case for the network-on-chip paradigm by stating that "wires are free" and consequently an interconnect architecture consisting of many multi-wire links is, by default, feasible and efficient. In fact, wires are expensive in terms of the cost of the masks that are required in the successive steps of the fabrication of interconnect metal layers through photolithography. Moreover, they are not free in terms of the possible defects that can appear due to technology constraints specific to an increase in the number of metal layers for every process generation, and continuous increase in the aspect ratio of wires (the ratio between their vertical and horizontal dimensions). While the wires on the lower layers can be made with an aspect ratio of less than one, the interconnects on middle and upper metal layers require an aspect ratio of two or higher. This, in turn, places an increased difficulty in achieving reliable contact between wires on different layers, since the vias between such wires will need to be relatively tall and narrow, and as a consequence more likely to exhibit open or resistive defects.

Currently, via duplication is the solution that attempts to address this issue by inserting redundant vias in the routing stage of the chip layout design phase. This method for improving interconnect yield is ad-hoc in nature and can only provide results if enough space is left on the upper level metal layers to insert the redundant vias while preserving the design rules. Most of the authors of technical articles on the topic of via duplication state clearly that, ideally, the solution for interconnect yield improvement should be pushed earlier in the design flow of ICs, more preferably in the front-end rather than in the back-end. A universal front-end solution for improving interconnect yield has not yet been found. However, by examining the categories of interconnect that are more prone to defects, it is possible to develop custom solutions targeting particular interconnect types.

That is, in order to ensure correct fabrication, faults must be detected through postfabrication testing, and, possibly, compensated for through fault-tolerant techniques.

When looking in particular at design, test, manufacturing and the associated CAD tools in the NoC design flow in the context of shrinking transistor size and wire

6

dimensions, it is clear that fabrication defects and variability are significant challenges that are often overlooked. On-chip networks need mechanisms to ensure correct fabrication and life-time operation in presence of new defect/fault mechanisms, process variability, and high availability requirements.

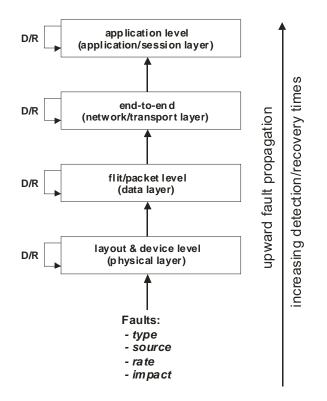

Traditionally, correct fabrication of integrated circuits is verified by postmanufacturing testing using different techniques ranging from scan-based techniques to delay test and current-based test. Due to their particular nature, NoCs are exposed to a wide range of faults that can escape the classic test procedures. Among such faults we can enumerate crosstalk, faults in the buffers of the NoC routers, and higher-level faults such as packet misrouting and data scrambling [6]. These fault types add to the classic faults that must be tested after fabrication for all integrated circuits (stuck-at, opens, shorts, memory faults, etc.). Consequently, the test time of NoC-based systems increases considerably due to these new faults.

Test time is an important component of the test cost and, implicitly, of the total fabrication cost of a chip. For large volume production, the total chip testing time must be reduced as much as possible in order to keep the total cost low. The total test time of an IC is governed by the amount of test data that must be applied and the amount of controllability/observability that the design-for-test (DFT) strategy chosen by designers can provide. The test data increases with chip complexity and size, so the option the DFT engineers are left with is to improve the controllability/observability. Traditionally, this is achieved by increasing the number of test inputs/outputs, but this has the same effect of increasing the total cost of the IC.

DFT techniques such as scan-based test improve the controllability and observability of IC internal components by serializing the test input/output data and feeding/extracting it to/from the IC through a reduced number of test pins. The trade-off is the increase in test time and test frequency, which makes at-speed test difficult using scan-based techniques. While scan-based solutions are useful, their limitations in the particular case of NoC systems demand the development of new test data generation and transport mechanisms that simultaneously minimize the total test time and the number of test I/O pins.

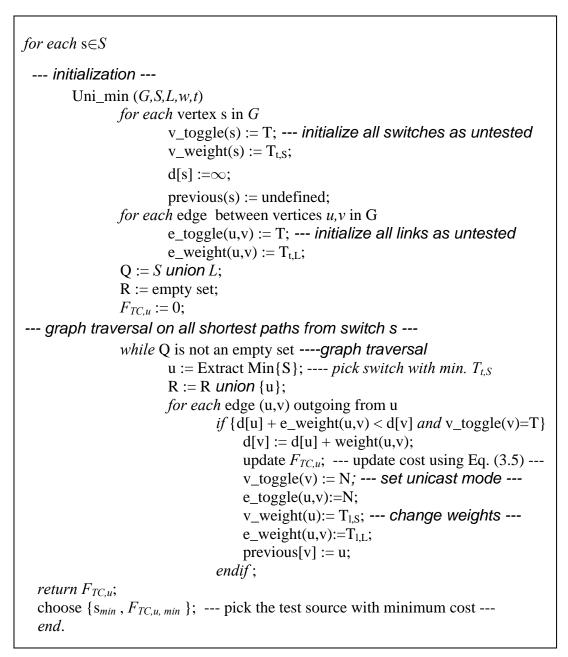

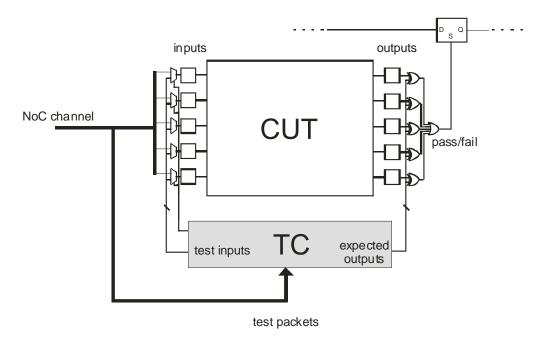

In this work, two types of solutions are proposed *to reduce the test time of NoC* data transport infrastructures: first, we use a built-in self-test solution to generate test data internally, eliminating the need to inject test data using I/O pins. Second, we replace the use of a traditional dedicated test access mechanism (TAM) with a test transport mechanism that reuses the NoC infrastructure progressively to transport test data to NoC components under test. This approach has the advantage that it exploits the inherent high degree of parallelism of the NoC, thus allowing the delivery of multiple test vectors in parallel to multiple NoC components under test. A multicast test delivery mechanism is described, with one test data source that sends test data in a parallel fashion along the subset of already tested NoC components. The test data routing algorithm is optimized off-line, deterministically, such that the shortest paths are always selected for forwarding test packets. This techniques guarantees that the test transport time is minimized which, together with the advantage of testing multiple NoC components in parallel, yields a reduced test time for the overall NoC.

An effective and efficient test procedure is necessary, but not sufficient to guarantee the correct operation of NoC data transport infrastructures during the life-time of the integrated circuits. Defects may appear later in the field, due to causes such as electromigration, thermal effects, material ageing, etc. These effects will become more pronounced with continuous downscaling of device dimensions beyond 65 nm and moving towards the nanoscale domain. New methods are needed to enhance the yield of these links to make them more reliable. The fault-tolerant solution using reconfigurable crossbars and redundant links developed in this work is aimed specifically at the NoC links, and allows both *post-fabrication yield tuning* and *self-repair of links* that may break down later in the life-cycle of the chip.

### **1.1 Dissertation contribution**

This dissertation offers three major contributions:

- 1. A complete NoC test methodology, including the hardware circuitry and scheduling algorithms, which together minimize the test time by distributing test data concurrently to multiple components of the NoC fabric.

- An evaluation of various fault-tolerance mechanisms for NoC infrastructures, and two new metrics relevant to quality-of-services on NoCs.

- 3. A fault-tolerant design method for NoC links that allows fine yield tuning and life-cycle self-repair of NoC interconnect infrastructures. This method uses the above-mentioned test mechanism to diagnose and identify the faulty interconnects.

The rest of this dissertation is organized as follows: Chapter 2 presents background on network-on-chip test aspects and fault models. Chapter 3 presents contribution (1) - a test methodology and scheduling algorithms that minimize the test time of NoC of arbitrary topologies. Chapter 4 presents contribution (2) - an overview and evaluation of fault-tolerance mechanisms and two proposed metrics relevant to NoCs. Chapter 5 describes contribution (3) - a method to provide design fault-tolerant NoC links based on sparse crossbars and tune the yield of NoC links based on the expected defect rate. Chapter 6 concludes the dissertation, outlines a few limitations of the proposed approaches, and provides a set of possible future research directions that can be pursued as a direct follow-up to the contributions presented in this dissertation.

# Chapter 2

### 2 Background on Network-on-chip Testing

### 2.1 Introduction

System-on-Chip (SoC) design methodologies are currently undergoing revolutionary changes, driven by the emergence of multi-core platforms supporting large sets of embedded processing cores. These platforms may contain a set of heterogeneous components with irregular block sizes and/or homogeneous components with a regular block sizes. The resulting platforms are collectively referred to as multi-processor SoC (MP-SoC) designs [7]. Such MP-SoCs imply the seamless integration of numerous Intellectual Property (IP) blocks performing different functions and exchanging data through a dedicated on-chip communication infrastructure. A key requirement of these platforms, whether irregular or regular, is a structured interconnect architecture. The network-on-chip (NoC) architecture is a leading candidate for this purpose [18].

### 2.2 Multi-processor systems-on-chip

Since today's VLSI chips can accommodate in excess of 1 billion transistors, enough to theoretically place thousands of 32-bit RISC [18] processors on a die, leveraging such capabilities is a major challenge. Traditionally, SoC design was based on the use of a slowly evolving set of hardware and software components: general-purpose processors, digital signal processors (DSPs), memory blocks, and other custom-designed hardware IP blocks (digital and analog). With a significant increase in the number of components in complex SoCs, significantly different design methods are required to cope with the deep sub-micron physical design issues, verification and design-for-test of the resulting SoCs.

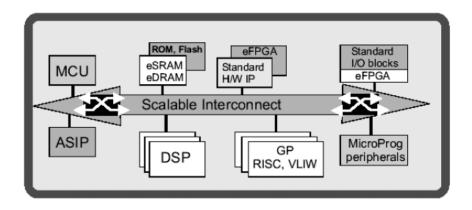

One of the solutions that the design community adopted to reduce the design cycle is the platform-based design paradigm, characterized by the use of higher-level off-the-shelf IP blocks, connected via a modular, scalable SoC interconnect fabric and standard communication interfaces and protocols. Such MP-SoC platforms are highly flexible, programmable and/or reconfigurable for application areas such as wireless, multimedia, networking, automotive. A high-level view of the general MP-SoC platform is given in Fig. 2-1. When designing with such platforms, no IP design is performed, but specification, configuration and assembly of existing IP blocks is greatly facilitated.

Figure 2-1: MP-SoC platform [7]

MP-SoC platforms will include, in the near future, tens to hundreds of embedded processors, in a wide variety of forms, from general-purpose reduced instruction-set computers (RISC) to application-specific instruction-set processors (ASIP) with different trade-offs in time-to-market, performance, power and cost. New designs are being reported from industry [19], with more than 100 embedded heterogeneous processors, for applications ranging from communications, network processing, to security processors, storage array networks, and consumer image processing.

### 2.3 Networks-on-chip

A key component of the MP-SoC platform of Fig. 2-1 is the interconnect fabric connecting the major blocks. Such a fabric must provide orthogonality, scalability, predictable physical parameters and a plug-and-play design style for integrating various hard-wired, reconfigurable or programmable IPs. Such architectures must support high-level, layered communication abstraction, and simplify the automatic mapping of processing resources onto the interconnect fabric. Networks-on-chip are particularly suitable for accomplishing these features.

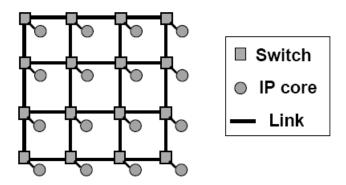

A NoC interconnect fabric is a combination of hardware (switches and inter-switch links) and software components (communication and interfacing protocols). NoCs can be organized in various topologies [20] – mesh, tree, ring, irregular, etc...– and can implement various subsets of the ISO/OSI communication stack [21]. A well-known 2D mesh NoC topology is illustrated in Fig. 2-2. The term *Network-on-chip* is used today mostly in a very broad sense, encompassing the hardware communication infrastructure, the communication protocols and interfaces, operating system communication services, and the design methodology and tools for NoC syndissertation and application mapping. All these components together can be called a *NoC platform* [7]. Some authors use the *Network-on-chip* to denote the entire MP-SoC built on a structured, networked fabric – including the IP cores, the on-chip communication medium, application software and communication protocols [20]. In this dissertation, the *Network-on-chip* term refers to the on-chip communication architecture, including the hardware components (switches, links) and communication protocols.

Figure 2-2: Network-on-chip building blocks in a mesh configuration 2.4 Network-on-chip test – previous work

While much work has centered on design issues, much less effort has been directed to testing such NoCs. Any new design methodology will only be widely adopted if it is complemented by efficient test mechanisms. In the case of NoC-based chips, two main aspects have to be addressed with respect to their test procedures: how to test the NoC communication fabric, and how to test the functional cores (processing, memory and other modules). Since the inception of SoC designs, the research community has targeted principally the testing of the IP cores [22], giving little emphasis to the testing of their communication infrastructures. The main concern for SoC test was the design of efficient test access mechanisms (TAM) for delivering the test data to the individual cores under constraints such as test time, test power, and temperature. Among the different test access mechanisms, TestRail [23] was one of the first to address core-based test of SoCs. Recently, a number of different research groups suggested the reuse of the communication infrastructure as a test access mechanism [24] [25] [26]. In [27] the authors assumed the NoC fabric as fault-free and subsequently used it to transport test data to the functional blocks; however, for large systems, this assumption can be unrealistic, considering the complexity of the design and communication protocols. In [28], the authors proposed a dedicated TAM based on an on-chip network, where network-oriented mechanisms were used to deliver test data to the functional cores of the SoC.

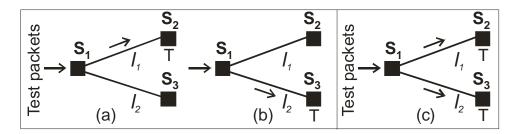

A test procedure for the links of NoC fabrics is presented in [29], targeted specifically to mesh topologies. The NoC switches are assumed to be tested using conventional methods first, and then three test configurations are applied in series to diagnose potential faults of the inter-switch links, as indicated in Fig. 2-3.

Figure 2-3: Test configurations in [29]: (a) straight paths; (b) turning paths; (c) local resource connections

A configuration is set up by adjusting the corresponding destination address fields of the transmitted packets to the last row (column) of the network matrix. The three configurations cover all possible link directions in a mesh NoC: vertical, horizontal, turning paths, and local connections to processing resources. The major limitations of this approach are: 1) applicability to mesh-based NoC only; 2) a test procedure for NoC switches is not defined.

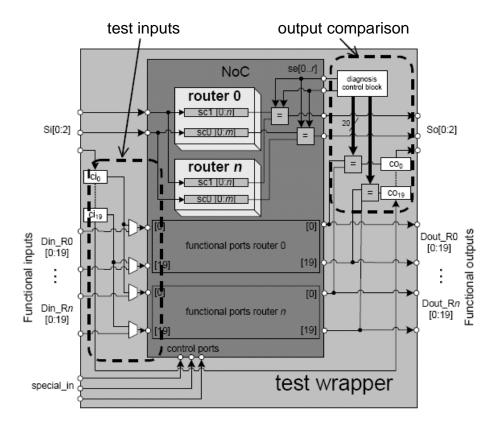

A different approach is presented in [30], based on an extension of the classic wrapper-based SoC test [23] and scan-chain method [31]. Each NoC switch (or router) is subjected to scan-chain insertion, and the set of all NoC switches is wrapped with an

IEEE 1500 test wrapper and tested using the core-based test approach [23]. The overall test architecture is presented in Figure 2-4.

Figure 2-4: Core-based test of NoC routers using an IEEE 1500 test wrapper and scan insertion [30]

The solution presented in [30] addresses the test of the NoC switches only, overlooking completely the aspect of testing the NoC links. For large NoCs, the method inherits the limitations of scan-based test when applied to large cores: slow test speed for long scan chains, the trade-off between the number of test I/Os and scan chain length.

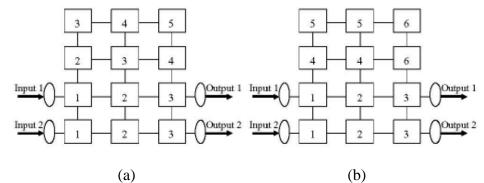

The idea of reusing the NoC fabric for delivering test data to the processing elements appears also in [26], combined with progressive test of NoC routers and overlapping the test of routers and processing elements in time to reduce the total test time. Both unicast and multicast test transport methods are considered, as shown in Figure 2-5.

Figure 2-5: Test data transport for NoC router testing using (a) multicast and (b) unicast [26]

The work presented in [26] does not consider the test of NoC links, and does not show how to minimize the test transport time in either the unicast or multicast transport modes. It is also not clear if the proposed solution delivers an optimal test time when combining test of NoC routers and processing cores.

This dissertation is focused on the test of the NoC infrastructure that includes both NoC switches and inter-switch links. The work complements previous approaches by developing the test strategy for the interconnect infrastructure itself. The test strategies of NoC-based interconnect infrastructures must address two problems [16]: (i) testing of the switch blocks; (ii) testing of the inter-switch wire segments. The test procedures of both switches and inter-switch links are integrated in a streamlined fashion. Two novel techniques characterize the proposed solution. The first is the reuse of the already tested NoC components to transport the test data towards the components under test in a recursive manner. The second is employing the inherent parallelism of the NoC structures to propagate the test data simultaneously to multiple NoC elements under test. Two test scheduling algorithms are provided that guarantee a minimal test time for arbitrary NoC topologies. In the next section we elaborate the set of fault models used for designing the proposed test method, including scheduling algorithms and on-chip test-related hardware.

#### 2.5 Fault models for NoC infrastructure test

When developing a test methodology for NoC fabrics, one needs to start from a set of models that can realistically represent the faults specific to the nature of NoC as a data transport mechanism. As stated previously, a NoC infrastructure is built from two basic types of components: switches and inter-switch links. For each type of component, test patterns must be constructed that exercise its characteristic faults.

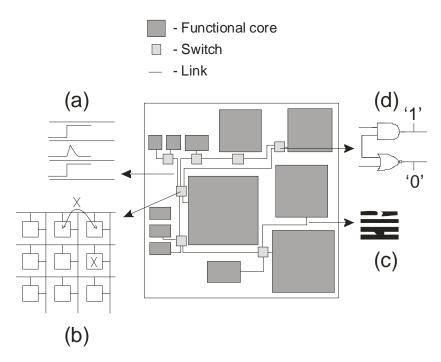

Figure 2-6: Examples of faults that can affect NoC infrastructures: (a) crosstalk faults; (b) memory faults in the input/output buffers of the switches; (c) short/open interconnect faults; (d) stuck-at faults affecting the logic gates of NoC switches.

The range of faults that can affect the NoC infrastructure is significant and it extends from interconnects faults to logic and memory faults. Consequently, the data set required to test all these faults is extremely large, and carries a major overhead to the overall test time of NoC-based integrated circuits. A subset of these faults is represented in Fig. 2-6. In the following subsections the set of faults considered in this work for the NoC switches and links is presented.

#### 2.5.1 Wire/crosstalk fault models for NoC inter-switch links

Cuviello et al. [32] proposed a novel fault model for the global interconnects of DSM SoCs that accounts for cross-talk effects between a set of aggressor lines and a victim line. This fault model is referred to as Maximum Aggressor Fault (MAF) and it occurs when the signal transition on a *single* interconnect line (called the *victim line*) is affected through cross-talk by transitions on *all* the other interconnect lines (called the *aggressors*) due to the presence of the crosstalk effect. In this model, all the aggressor lines switch in the same direction simultaneously.

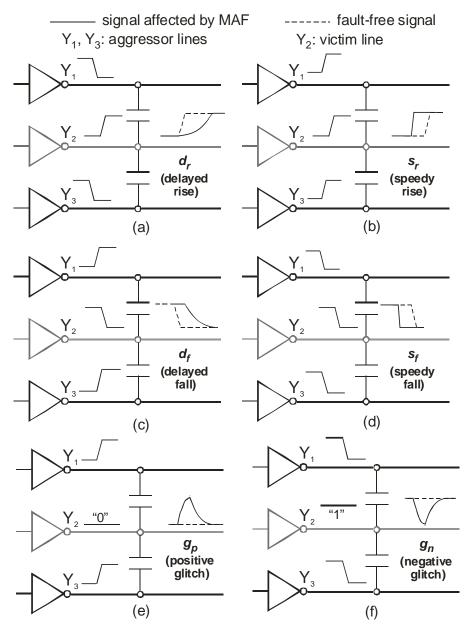

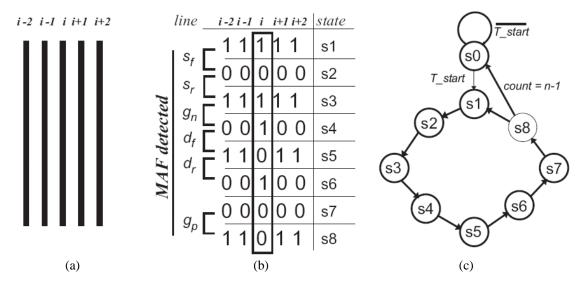

The MAF model is an abstract representation of the set of all defects that can lead to one of the six crosstalk errors: rising/falling delay, positive/negative glitch, and rising/falling speed-up. The possible errors corresponding to the MAF fault model are presented in Fig. 2-7 for a link consisting of 3 wires. The signals on lines  $Y_1$  and  $Y_3$  act as aggressors, while  $Y_2$  is the victim line. The aggressors act collectively to produce a delay, glitch or speed-up on the victim.

This abstraction covers a wide range of defects including design errors, design rules violations, process variations and physical defects. For a link consisting of N wires, the MAF model assumes the worst-case situation with one victim line and (N-I) aggressors. For links consisting of a large number of wires, considering all such variations is prohibitive from a test coverage point of view [31].

The transitions needed to sensitize the MAF faults can be easily derived from Fig. 2-7 based on the waveform transitions indicated. For an inter-switch link consisting of N wires, a total of 6N faults need to be tested, and requiring 6N 2-vector tests. These 6N MAF faults cover all the possible process variations and physical defects that can cause

any crosstalk effect on any of the *N* interconnects. They also cover more traditional faults such as stuck-at, stuck-open and bridging faults.

Figure 2-7: MAF crosstalk errors (Y<sub>2</sub> – victim wire; Y<sub>1</sub>, Y<sub>3</sub> – aggressor wires).

#### 2.5.2 Logic/memory fault models for FIFO buffers in NoC switches

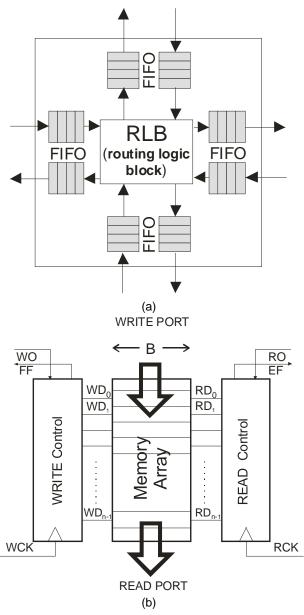

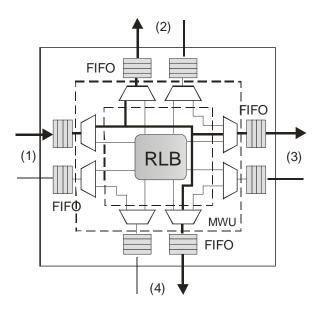

NoC switches generally consist of a combinational block in charge of functions such as arbitration, routing, error control, and first-in/first-out (FIFO) memory blocks that serve as communication buffers [33][34]. Fig. 2-8(a) shows the generic architecture of a NoC switch. As information arrives at each of the ports, it is stored in FIFO buffers and then routed to the target destination by the routing logic block (RLB).

The FIFO communication buffers for NoC fabrics can be implemented as register banks [35] or dedicated SRAM arrays [36]. In both cases, functional test is preferable due to its reduced time duration, good coverage, and simplicity.

The block diagram of a NoC FIFO is shown in Fig. 2-8(b). From a test point of view, the NoC-specific FIFOs fall under the category of restricted two-port memories. Due to the unidirectional nature of the NoC communication links, they have one write-only port and one read-only port, and are referred to as *(wo-ro)2P* memories. Under these restrictions, the FIFO function can be divided in three ways: the memory-cells array, the addressing mechanism, and the FIFO-specific functionality [37].

Figure 2-8: (a) 4-port NoC switch – generic architecture; (b) dual port NoC FIFO.

Memory array faults can be stuck-at, transition, data retention or bridging faults [31]. Addressing faults on the RD/WD lines are also important as they may prevent cells from being read/written. In addition, functionality faults on the *empty* and *full* flags (EF and FF, respectively) are included in our fault models set [37].

### 2.6 Summary

In this chapter, the problems of NoC testing and prior work in this area were described. Then, the set of fault models that used in this work for developing the test scheduling algorithms and the associated on-chip test hardware were detailed. Different fault models are outlined for testing NoC channels and routers. The choice for constructing test vectors for NoC links is the maximum aggressor fault (MAF) which takes the worst-case crosstalk scenario into consideration, with the benefit that it also covers other, more traditional faults (opens, shorts, stuck-at). For the input/output buffers of the NoC routers we use memory-specific fault models which take into account the dual-port characteristic of the FIFO buffers and allow functional test for these components. The routing logic blocks of the NoC switches are simply tested using classic stuck-at, open, and short fault models.

# **Chapter 3**

### **3** Test Time Minimization for Networks-on-Chip<sup>1</sup>

A significant portion of the total production cost of an IC is represented by its associated test procedures. A direct measure of an IC's test cost is the time spent for testing it. With increasing transistor-count and complexity, multi-core SoCs pose a particular challenge in terms of keeping the test time under reasonable limits. Much research effort is invested in minimizing the test time of large SoCs, and, consequently, the total production cost. In the case of NoC-based MP-SoCs, the test time of the NoC infrastructure adds to the total IC production cost. Reducing the NoC test time contributes to lowering the total SoC test time, and, implicitly, production cost. This chapter presents a test method and corresponding hardware circuitry that minimize the test time of NoC interconnect fabrics.

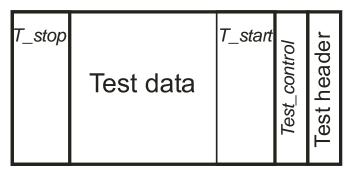

### 3.1 Test data organization